文章目录

- 一、Pcie的发送时序

- 1.1 不带数据的TLP包

- 1.2 带数据的TLP包

- 1.3 连续发送数据的TLP包

- 二、Pcie的接收时序

- 2.1 不带数据的TLP包

- 2.2 带数据的TLP包

- 2.3 连续接收数据的TLP包

- 三、riffa框架和用户channel的接口

- 3.1 RX接口波形:

- 3.2 TX接口波形:

一、Pcie的发送时序

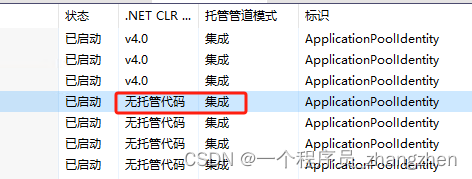

这里介绍的是Xilinx VIVADO 软件集成的7 Series Integrated Block for PCI Express.硬核,它与用户通信用 AXI4 接口。

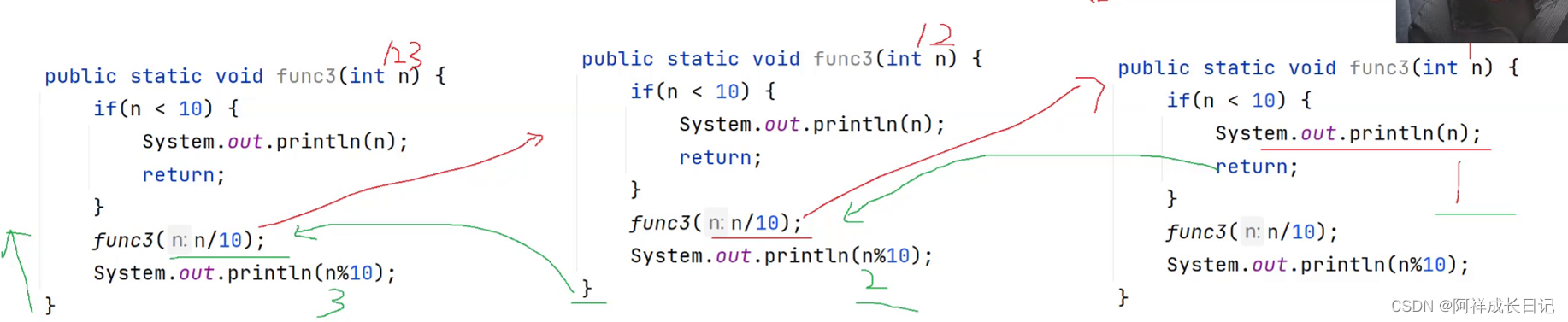

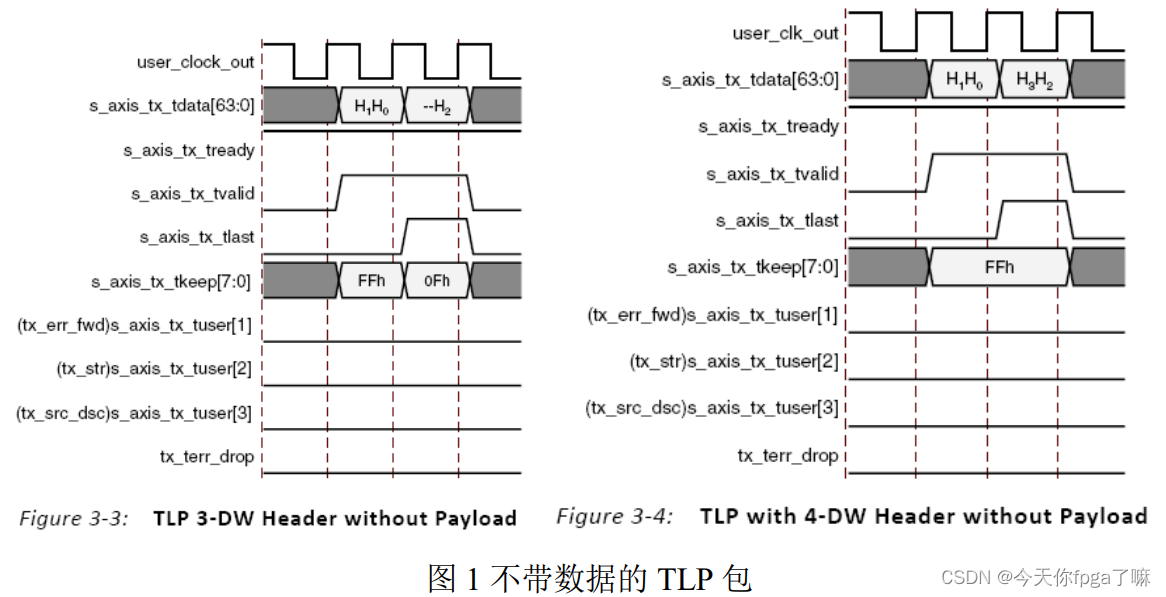

1.1 不带数据的TLP包

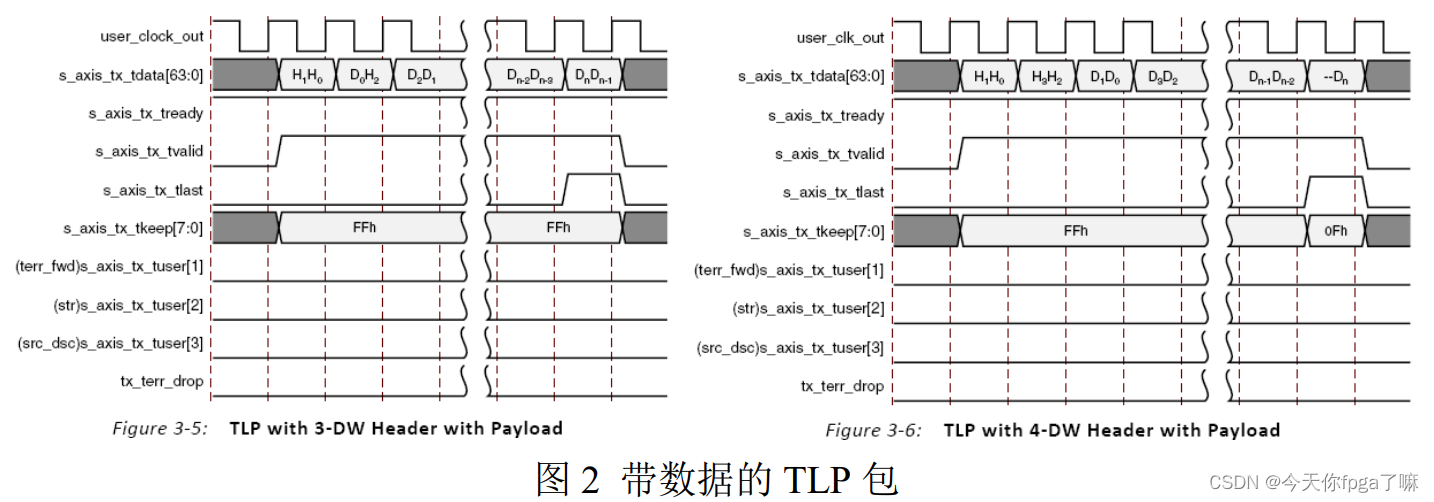

1.2 带数据的TLP包

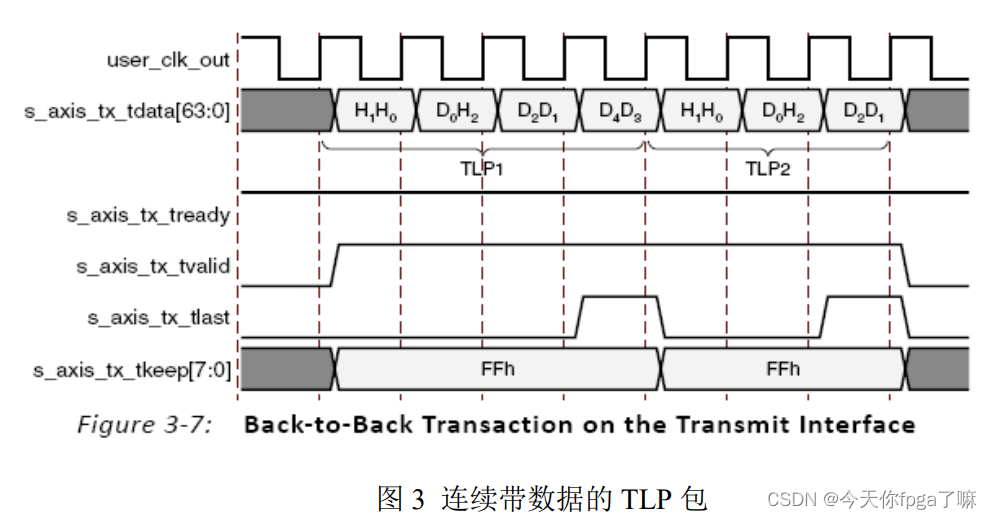

1.3 连续发送数据的TLP包

二、Pcie的接收时序

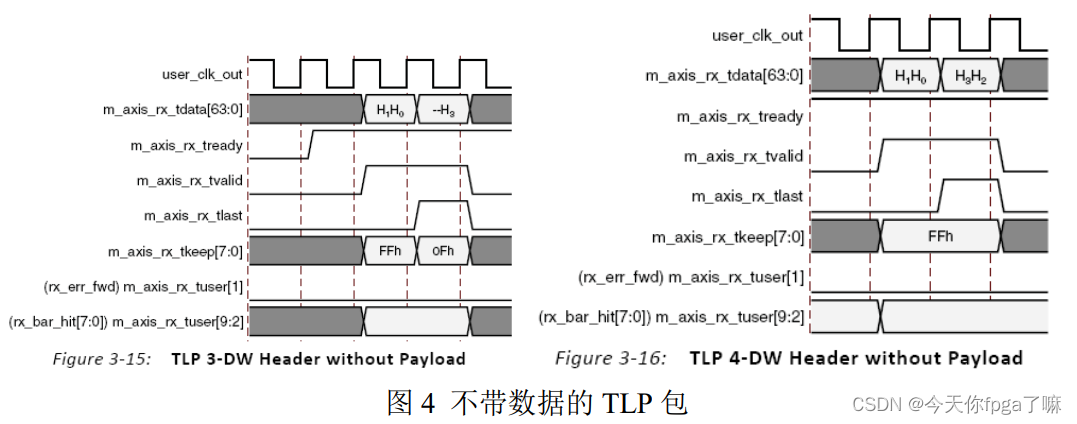

2.1 不带数据的TLP包

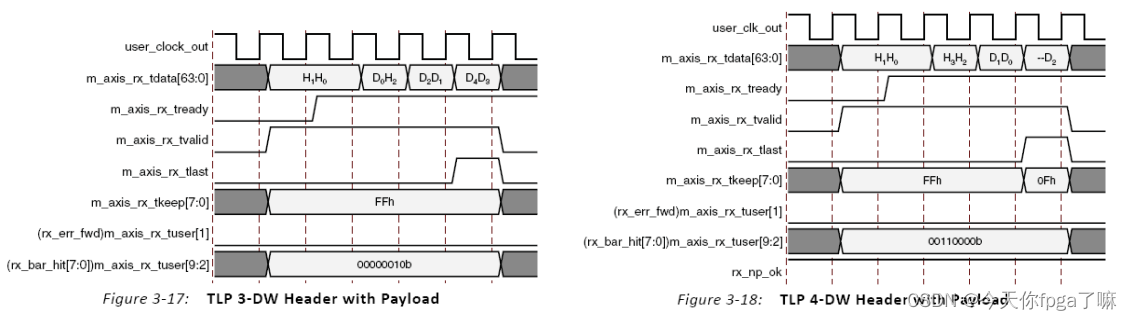

2.2 带数据的TLP包

2.3 连续接收数据的TLP包

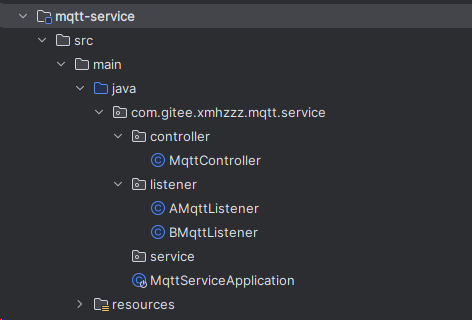

三、riffa框架和用户channel的接口

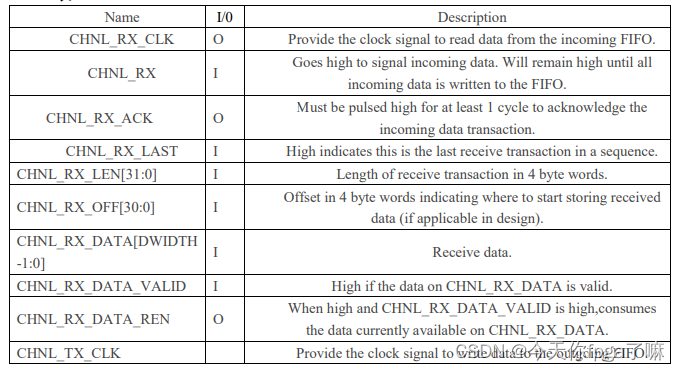

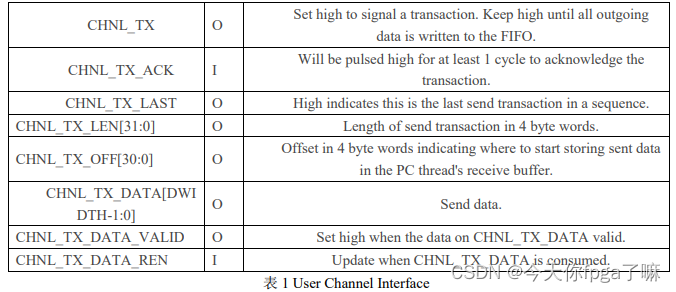

用户接口是用户与 RIFFA 交互的接口,使用起来非常简单,其端口定义如下表。

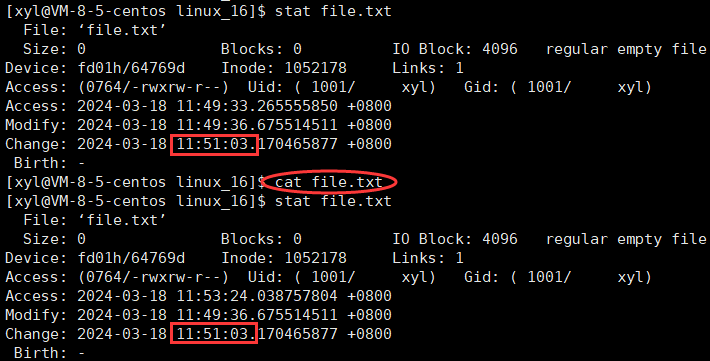

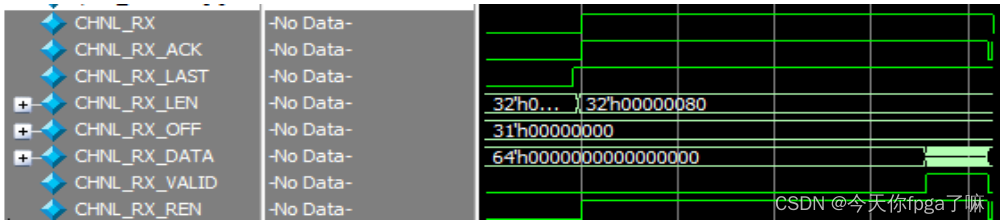

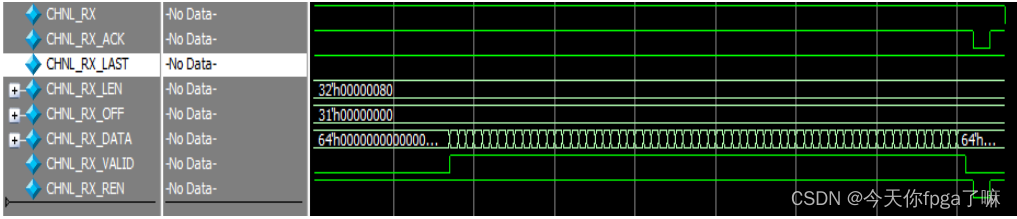

3.1 RX接口波形:

波形细节:

注意:RX接口中CHNL_RX信号不是在接收数据后立刻拉低的,而是会有1~2拍的延时。

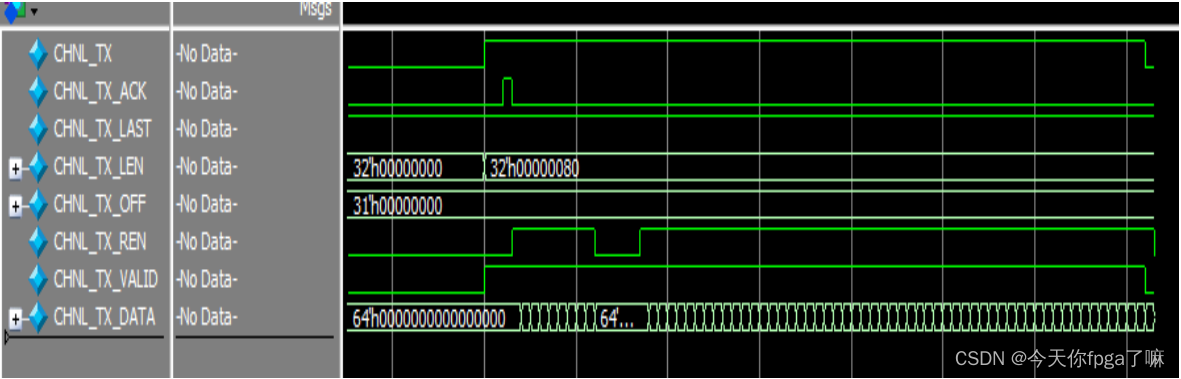

3.2 TX接口波形:

注意:这里CHNL_TX信号会在数据发送完毕后立刻拉低