0. 环境

- pzp203

- ubuntu18 + vivado2018

pzp203是一款plutosdr的国产兼容版。出厂默认是基于linux系统的,用libiio调用。软硬件兼容adalm-pluto。开发板提供网盘资料,是添加了板卡适配的。

1. hdl

1.1 准备源码

hdl

https://github.com/analogdevicesinc/hdl/releases

切换分支到2019_r1,通过Download as zip下载

hdl-2019_r1.tar.gz

放到工作区,

~/work/pzp203/ad9361os/

解压

tar -zvxf hdl-2019_r1.tar.gz1.2 生成 vivado 工程

设置vivado环境

source /tools/Xilinx/Vivado/2018.3/settings64.sh

开始编译

cd /home/xxjianvm/work/pzp203/ad9361os/hdl-2019_r1

make fmcomms2.zed

# 如果用基于pluto的HDL,META-ADI未支持pluto,无法顺利加载ad9361,这里还是用fmcomms2的hdl

得到了vivado工程。

1.3 适配

vivado 打开工程

source /tools/Xilinx/Vivado/2018.3/settings64.sh

vivado &

Open Project -> /home/xxjianvm/work/pzp203/ad9361os/hdl-2019_r1/projects/fmcomms2/zed/fmcomms2_zed.xpr

1.3.1 修改芯片型号

PROJECT MANAGER -> Settings -> Project Settings -> General -> Project device: xc7z020clg400-1 -> OK -> Apply -> NO -> OK更新IP

IP INTEGRATOR -> Open Block Design -> Report IP Status -> Upgrade Selected -> OK1.3.2 适配ddr

双击 sys_ps7 ->

-> DDR Configuration

-> DDR Controller Configuration

-> Memory Type: DDR3

-> Memory Part: MT41K256M16 RE-125

-> Effective DRAM Bus Width: 32 Bit

-> OK1.3.3 适配ETH0,SD0,UART0,USB0

双击 sys_ps7 ->

-> Peripheral I/O Pins

-> 点击位于 MIO12-MIO13 的 UART1

-> 展开 SD0

-> 取消勾选 Card Detect

-> 取消勾选 Write Protect

-> MIO Configuration

-> Bank 0 I/O Voltage: LVCMOS 1.8V

-> Bank 1 I/O Voltage: LVCMOS 1.8V

-> 展开 I/O Peripherals

-> 展开 GPIO

-> 勾选 GPIO MIO

-> 勾选 USB0 Reset

-> 选择 MIO 48

-> OK1.3.4 适配 ad9361

双击 axi_ad9361

-> Cmos Or Lvds N: 1

-> OK

点击 rx_clk_in、rx_frame_in、rx_data_in[11:0]、tx_clk_in、tx_frame_in、tx_data_in[11:0] -> 右键 Make External -> 删除引出引脚中的_0

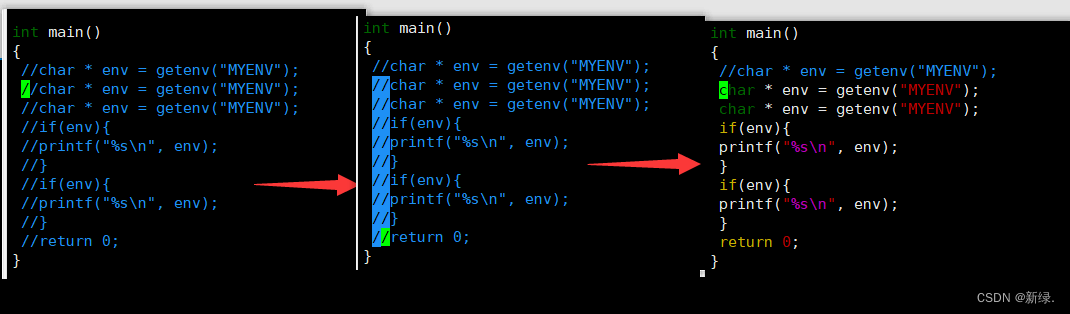

修改 system_wrapper.v

把

rx_clk_in_n,

rx_clk_in_p,

rx_data_in_n,

rx_data_in_p,

rx_frame_in_n,

rx_frame_in_p,

input rx_clk_in_n;

input rx_clk_in_p;

input [5:0]rx_data_in_n;

input [5:0]rx_data_in_p;

input rx_frame_in_n;

input rx_frame_in_p;

wire rx_clk_in_n;

wire rx_clk_in_p;

wire [5:0]rx_data_in_n;

wire [5:0]rx_data_in_p;

wire rx_frame_in_n;

wire rx_frame_in_p;

.rx_clk_in_n(rx_clk_in_n),

.rx_clk_in_p(rx_clk_in_p),

.rx_data_in_n(rx_data_in_n),

.rx_data_in_p(rx_data_in_p),

.rx_frame_in_n(rx_frame_in_n),

.rx_frame_in_p(rx_frame_in_p),

修改为:

rx_clk_in,

rx_data_in,

rx_frame_in,

input rx_clk_in;

input [11:0]rx_data_in;

input rx_frame_in;

wire rx_clk_in;

wire [11:0]rx_data_in;

wire rx_frame_in;

.rx_clk_in(rx_clk_in),

.rx_data_in(rx_data_in),

.rx_frame_in(rx_frame_in),把

tx_clk_out_n,

tx_clk_out_p,

tx_data_out_n,

tx_data_out_p,

tx_frame_out_n,

tx_frame_out_p,

output tx_clk_out_n;

output tx_clk_out_p;

output [5:0]tx_data_out_n;

output [5:0]tx_data_out_p;

output tx_frame_out_n;

output tx_frame_out_p;

wire tx_clk_out_n;

wire tx_clk_out_p;

wire [5:0]tx_data_out_n;

wire [5:0]tx_data_out_p;

wire tx_frame_out_n;

wire tx_frame_out_p;

.tx_clk_out_n(tx_clk_out_n),

.tx_clk_out_p(tx_clk_out_p),

.tx_data_out_n(tx_data_out_n),

.tx_data_out_p(tx_data_out_p),

.tx_frame_out_n(tx_frame_out_n),

.tx_frame_out_p(tx_frame_out_p),

修改为:

tx_clk_out,

tx_data_out,

tx_frame_out,

output tx_clk_out;

output [11:0]tx_data_out;

output tx_frame_out;

wire tx_clk_out;

wire [11:0]tx_data_out;

wire tx_frame_out;

.tx_clk_out(tx_clk_out),

.tx_data_out(tx_data_out),

.tx_frame_out(tx_frame_out),修改 systm_top.v

把

input rx_clk_in_p,

input rx_clk_in_n,

input rx_frame_in_p,

input rx_frame_in_n,

input [ 5:0] rx_data_in_p,

input [ 5:0] rx_data_in_n,

output tx_clk_out_p,

output tx_clk_out_n,

output tx_frame_out_p,

output tx_frame_out_n,

output [ 5:0] tx_data_out_p,

output [ 5:0] tx_data_out_n,

修改为:

input rx_clk_in,

input rx_frame_in,

input [ 11:0] rx_data_in,

output tx_clk_out,

output tx_frame_out,

output [ 11:0] tx_data_out_p,

把

.rx_clk_in_n (rx_clk_in_n),

.rx_clk_in_p (rx_clk_in_p),

.rx_data_in_n (rx_data_in_n),

.rx_data_in_p (rx_data_in_p),

.rx_frame_in_n (rx_frame_in_n),

.rx_frame_in_p (rx_frame_in_p),

.tx_clk_out_n (tx_clk_out_n),

.tx_clk_out_p (tx_clk_out_p),

.tx_data_out_n (tx_data_out_n),

.tx_data_out_p (tx_data_out_p),

.tx_frame_out_n (tx_frame_out_n),

.tx_frame_out_p (tx_frame_out_p),

修改为:

.rx_clk_in (rx_clk_in),

.rx_data_in (rx_data_in),

.rx_frame_in (rx_frame_in),

.tx_clk_out (tx_clk_out),

.tx_data_out (tx_data_out),

.tx_frame_out (tx_frame_out),并添加

wire [31:0] gpio_bd;

wire gpio_muxout_tx;

wire gpio_muxout_rx;

不加怕影响到GPIO引脚号。

vivado2018还需要打开 axi_ad9361的ip,ADC_IODELAY_ENABLE 设置为0

ad_data_in.v中

把

parameter IODELAY_ENABLE = 1,

修改为:

parameter IODELAY_ENABLE = 0,

并把 axi_ad9361_cmos_if.v中的 ad_data_in 都设置 .IODELAY_CTRL (0),

参考:AD-FMCOMMS3-EBZ 调试 Tuning TX/RX FAILED!,https://blog.csdn.net/Claud_Ma/article/details/120837057

1.3.5 适配引脚

修改引脚约束文件为以下内容,(编辑文件 Sources -> Constrants -> constrs_1 -> system_constr.xdc):

# constraints

# ad9361

set_property -dict {PACKAGE_PIN P18 IOSTANDARD LVCMOS18} [get_ports gpio_en_agc] ;

set_property -dict {PACKAGE_PIN W19 IOSTANDARD LVCMOS18} [get_ports gpio_resetb] ;

set_property -dict {PACKAGE_PIN P15 IOSTANDARD LVCMOS18} [get_ports gpio_sync] ;

set_property -dict {PACKAGE_PIN V8 IOSTANDARD LVCMOS18} [get_ports gpio_ctl[0]] ;

set_property -dict {PACKAGE_PIN W8 IOSTANDARD LVCMOS18} [get_ports gpio_ctl[1]] ;

set_property -dict {PACKAGE_PIN W10 IOSTANDARD LVCMOS18} [get_ports gpio_ctl[2]] ;

set_property -dict {PACKAGE_PIN W9 IOSTANDARD LVCMOS18} [get_ports gpio_ctl[3]] ;

set_property -dict {PACKAGE_PIN U7 IOSTANDARD LVCMOS18} [get_ports gpio_status[0]] ;

set_property -dict {PACKAGE_PIN V7 IOSTANDARD LVCMOS18} [get_ports gpio_status[1]] ;

set_property -dict {PACKAGE_PIN T9 IOSTANDARD LVCMOS18} [get_ports gpio_status[2]] ;

set_property -dict {PACKAGE_PIN U10 IOSTANDARD LVCMOS18} [get_ports gpio_status[3]] ;

set_property -dict {PACKAGE_PIN Y7 IOSTANDARD LVCMOS18} [get_ports gpio_status[4]] ;

set_property -dict {PACKAGE_PIN Y6 IOSTANDARD LVCMOS18} [get_ports gpio_status[5]] ;

set_property -dict {PACKAGE_PIN Y9 IOSTANDARD LVCMOS18} [get_ports gpio_status[6]] ;

set_property -dict {PACKAGE_PIN Y8 IOSTANDARD LVCMOS18} [get_ports gpio_status[7]] ;

set_property -dict {PACKAGE_PIN N18 IOSTANDARD LVCMOS18} [get_ports rx_clk_in] ;

set_property -dict {PACKAGE_PIN R16 IOSTANDARD LVCMOS18} [get_ports rx_frame_in] ;

set_property -dict {PACKAGE_PIN V17 IOSTANDARD LVCMOS18} [get_ports rx_data_in[1]] ;

set_property -dict {PACKAGE_PIN V18 IOSTANDARD LVCMOS18} [get_ports rx_data_in[0]] ;

set_property -dict {PACKAGE_PIN Y18 IOSTANDARD LVCMOS18} [get_ports rx_data_in[3]] ;

set_property -dict {PACKAGE_PIN Y19 IOSTANDARD LVCMOS18} [get_ports rx_data_in[2]] ;

set_property -dict {PACKAGE_PIN T17 IOSTANDARD LVCMOS18} [get_ports rx_data_in[5]] ;

set_property -dict {PACKAGE_PIN R18 IOSTANDARD LVCMOS18} [get_ports rx_data_in[4]] ;

set_property -dict {PACKAGE_PIN V20 IOSTANDARD LVCMOS18} [get_ports rx_data_in[7]] ;

set_property -dict {PACKAGE_PIN W20 IOSTANDARD LVCMOS18} [get_ports rx_data_in[6]] ;

set_property -dict {PACKAGE_PIN T20 IOSTANDARD LVCMOS18} [get_ports rx_data_in[9]] ;

set_property -dict {PACKAGE_PIN U20 IOSTANDARD LVCMOS18} [get_ports rx_data_in[8]] ;

set_property -dict {PACKAGE_PIN V16 IOSTANDARD LVCMOS18} [get_ports rx_data_in[11]] ;

set_property -dict {PACKAGE_PIN W16 IOSTANDARD LVCMOS18} [get_ports rx_data_in[10]] ;

set_property -dict {PACKAGE_PIN U14 IOSTANDARD LVCMOS18} [get_ports tx_clk_out] ;

set_property -dict {PACKAGE_PIN V15 IOSTANDARD LVCMOS18} [get_ports tx_frame_out] ;

set_property -dict {PACKAGE_PIN P14 IOSTANDARD LVCMOS18} [get_ports tx_data_out[1]] ;

set_property -dict {PACKAGE_PIN R14 IOSTANDARD LVCMOS18} [get_ports tx_data_out[0]] ;

set_property -dict {PACKAGE_PIN V12 IOSTANDARD LVCMOS18} [get_ports tx_data_out[3]] ;

set_property -dict {PACKAGE_PIN W13 IOSTANDARD LVCMOS18} [get_ports tx_data_out[2]] ;

set_property -dict {PACKAGE_PIN W14 IOSTANDARD LVCMOS18} [get_ports tx_data_out[5]] ;

set_property -dict {PACKAGE_PIN Y14 IOSTANDARD LVCMOS18} [get_ports tx_data_out[4]] ;

set_property -dict {PACKAGE_PIN T14 IOSTANDARD LVCMOS18} [get_ports tx_data_out[7]] ;

set_property -dict {PACKAGE_PIN T15 IOSTANDARD LVCMOS18} [get_ports tx_data_out[6]] ;

set_property -dict {PACKAGE_PIN Y16 IOSTANDARD LVCMOS18} [get_ports tx_data_out[9]] ;

set_property -dict {PACKAGE_PIN Y17 IOSTANDARD LVCMOS18} [get_ports tx_data_out[8]] ;

set_property -dict {PACKAGE_PIN T16 IOSTANDARD LVCMOS18} [get_ports tx_data_out[11]] ;

set_property -dict {PACKAGE_PIN U17 IOSTANDARD LVCMOS18} [get_ports tx_data_out[10]] ;

set_property -dict {PACKAGE_PIN P16 IOSTANDARD LVCMOS18} [get_ports txnrx] ;

set_property -dict {PACKAGE_PIN N17 IOSTANDARD LVCMOS18} [get_ports enable] ;

set_property -dict {PACKAGE_PIN T10 IOSTANDARD LVCMOS18 PULLTYPE PULLUP} [get_ports spi_csn] ;

set_property -dict {PACKAGE_PIN T11 IOSTANDARD LVCMOS18} [get_ports spi_clk] ;

set_property -dict {PACKAGE_PIN T12 IOSTANDARD LVCMOS18} [get_ports spi_mosi] ;

set_property -dict {PACKAGE_PIN U12 IOSTANDARD LVCMOS18} [get_ports spi_miso] ;

# spi pmod JA1

set_property -dict {PACKAGE_PIN W11 IOSTANDARD LVCMOS18} [get_ports pl_spi_clk_o] ;

set_property -dict {PACKAGE_PIN U9 IOSTANDARD LVCMOS18} [get_ports pl_spi_miso] ;

set_property -dict {PACKAGE_PIN U8 IOSTANDARD LVCMOS18} [get_ports pl_spi_mosi] ;

set_property -dict {PACKAGE_PIN T5 IOSTANDARD LVCMOS18} [get_ports iic_scl] ;

set_property -dict {PACKAGE_PIN U5 IOSTANDARD LVCMOS18} [get_ports iic_sda] ;

# clocks

create_clock -name rx_clk -period 16.27 [get_ports rx_clk_in]修改引脚约束文件(编辑文件 Sources -> Constrants -> constrs_1 -> zed_system_constr.xdc):

#只留下以下内容:

# Define SPI clock

#create_clock -name spi0_clk -period 40 [get_pins -hier */EMIOSPI0SCLKO]

#create_clock -name spi1_clk -period 40 [get_pins -hier */EMIOSPI1SCLKO]

修改 system_top.v。

注释掉端口:

// inout [31:0] gpio_bd,

// output hdmi_out_clk,

// output hdmi_vsync,

// output hdmi_hsync,

// output hdmi_data_e,

// output [15:0] hdmi_data,

// output i2s_mclk,

// output i2s_bclk,

// output i2s_lrclk,

// output i2s_sdata_out,

// input i2s_sdata_in,

// output spdif,

// inout iic_scl,

// inout iic_sda,

// inout [ 1:0] iic_mux_scl,

// inout [ 1:0] iic_mux_sda,

// input otg_vbusoc,

// inout gpio_muxout_tx,

// inout gpio_muxout_rx,

// output spi_udc_csn_tx,

// output spi_udc_csn_rx,

// output spi_udc_sclk,

// output spi_udc_data

// ad_iobuf #(.DATA_WIDTH(2)) i_iobuf_iic_scl (

// .dio_t ({iic_mux_scl_t_s,iic_mux_scl_t_s}),

// .dio_i (iic_mux_scl_o_s),

// .dio_o (iic_mux_scl_i_s),

// .dio_p (iic_mux_scl));

// ad_iobuf #(.DATA_WIDTH(2)) i_iobuf_iic_sda (

// .dio_t ({iic_mux_sda_t_s,iic_mux_sda_t_s}),

// .dio_i (iic_mux_sda_o_s),

// .dio_o (iic_mux_sda_i_s),

// .dio_p (iic_mux_sda));

修改 system_wrapper.v

// IOBUF iic_fmc_scl_iobuf

// (.I(iic_fmc_scl_o),

// .IO(iic_fmc_scl_io),

// .O(iic_fmc_scl_i),

// .T(iic_fmc_scl_t));

// IOBUF iic_fmc_sda_iobuf

// (.I(iic_fmc_sda_o),

// .IO(iic_fmc_sda_io),

// .O(iic_fmc_sda_i),

// .T(iic_fmc_sda_t));

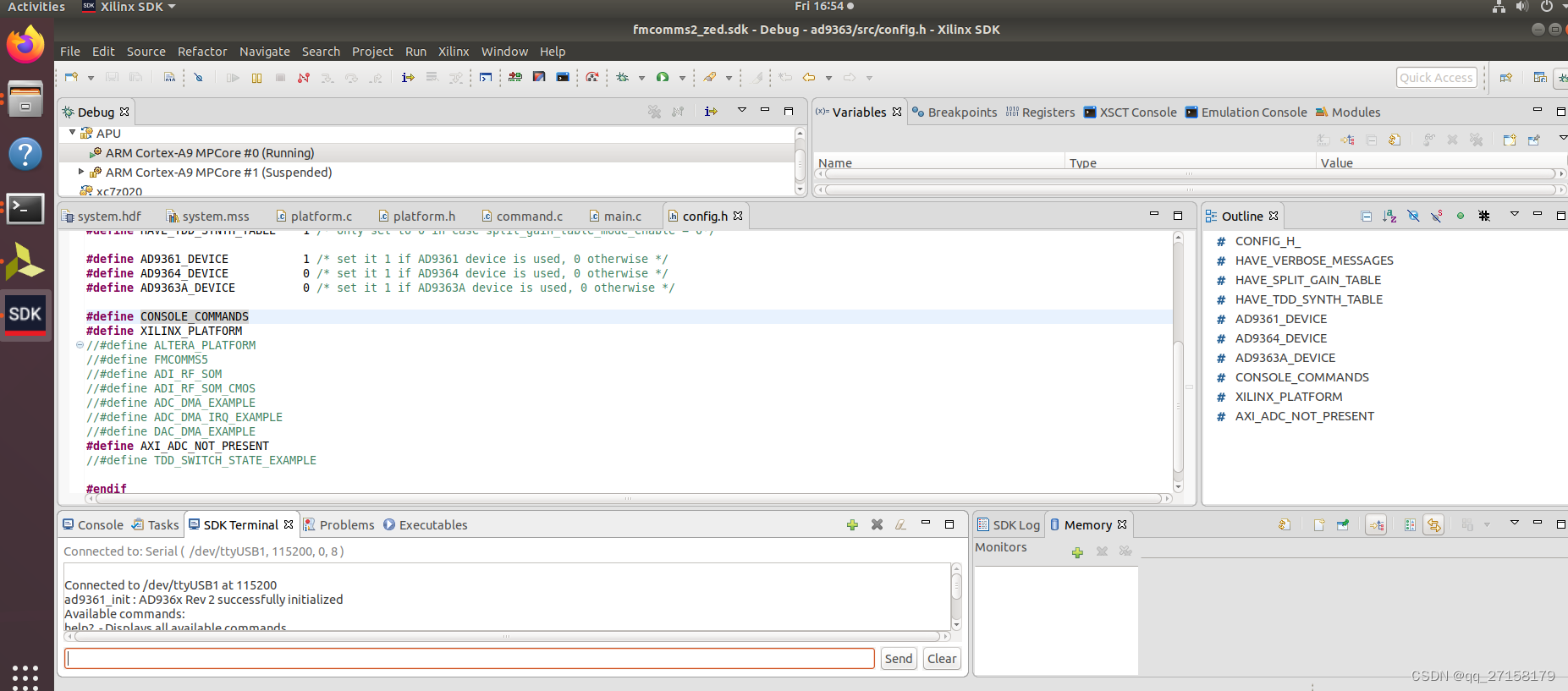

1.3.6 xadc(ad9363的noos工程,和ad9361的区别是需要取消注释:#define AXI_ADC_NOT_PRESENT)

创建一个 xadc

Diagram -> + -> XADC Wizard ->

双击 xadc_wiz_0 ->

-> Basic

-> Interface Options -> AXI4Lite

-> Startup Channel Selection -> Channel Sequencer

-> Timing Mode: Continuous Mode

-> DRP Timing Options

-> DCLK 100M

-> ADC Setup

-> Sequencer Mode: Continuous

-> Alarms

-> 全部取消勾选

-> Channel Sequencer

-> 勾选 TEMPERATURE

-> 勾选 VCCINT

-> 勾选 VCCAUX

-> 勾选 VCCBRAM

-> 勾选 VCCPINT

-> 勾选 VCCPAUX

-> 勾选 VCCDDRO

-> 勾选 VP/VN

-> OK连线

Run Connection Automation -> OK

1.4 编译

Run Synthesis

Run Implementation

Generate Bitstream

1.5 导出 hdf

Vivado -> File -> Export -> Export Hardware ->

-> Include bitstream -> OK

Vivado -> File -> Launch SDK -> OK

得到

/home/xxjianvm/work/pzp203/ad9361os/hdl-2019_r1/projects/pluto/pluto.sdk/system_top_hw_platform_0/system.hdf

2. no-os sdk

2.1 hello

File -> New -> Application Project

-> Project name: ad9361_test

-> Finish编译

调试

Debug As -> Launch on Hardware (system debugger)

Debug Configuration -> Target Setup

-> 勾选 Reset entire system

-> 勾选 Program FPGA板子记得调到JTAG模式。

串口权限

ls /dev/ttyUSB*

sudo chmod 666 /dev/ttyUSB0永久修改

whoami

该用户添加至dialout用户组,因为tty设备是属于dialout用户组

sudo usermod -aG dialout xxjianvm看到SDK Terminal打印

hello world

2.2 添加 ad9361 驱动

拷贝源码

把

~/work/zynq_dev/ad9361noos/no-OS-2019_R1/ad9361/sw

~/work/zynq_dev/ad9361noos/no-OS-2019_R1/ad9361/sw/console_commands

~/work/zynq_dev/ad9361noos/no-OS-2019_R1/ad9361/sw/platform_xilinx

内的源文件(*.c,*.h)拷贝到

~/work/pzp203/ad9361os/hdl-2019_r1/projects/fmcomms2/zed/fmcomms2_zed.sdk/ad9361noos/src

至于platform.c和platform.h,不覆盖源文件,把源码添加到各自的文件内。

删除 hello_world.c

2.3 修改源码

打开 command.c

把

#include "../ad9361_api.h"

修改为

#include "ad9361_api.h"打开 config.h

取消注释:

#define CONSOLE_COMMANDS

#define XILINX_PLATFORM

#define AXI_ADC_NOT_PRESENT

编译调试下载。

2.4 用串口命令发送

help?

参考:

[1]windows 下AD9361的 no-os master 工程搭建,https://blog.csdn.net/weixin_37728585/article/details/104835364

[2]https://wiki.analog.com/resources/fpga/docs/hdl

[3]https://wiki.analog.com/resources/eval/user-guides/ad-fmcomms2-ebz/software/no-os-setup

[4]https://wiki.analog.com/resources/eval/user-guides/ad-fmcomms2-ebz/software/baremetal

[5]https://ez.analog.com/rf/wide-band-rf-transceivers/tes-gui-and-api-software-ad9371-ad9375/f/q-a/80764/how-to-use-ad9361-no-os-setup