从本质上看,集成运放是一种高性能的直接耦合放大电路。尽管品种繁多,内部结构也各不相同,但是它们的基本组成部分、结构形式和组成原则基本一致。因此,对于典型电路的分析具有普遍意义,一方面可以从中理解集成运放的性能特点,另一方面可以了解复杂电路的分析方法。

一、双极型集成运放

我们知道,集成运放有四个组成部分。因此,在分析集成运放电路时,首先应将电路“化整为零”,分为偏置电路、输入级、中间级和输出级四个部分;进而“分析功能”,弄清每部分电路的结构形式和性能特点;最后“统观整体”,研究各部分相互间的联系,从而理解电路如何实现所具有的功能;必要时再进行“定量估算”。

在集成运放电路中,若有一个支路的电流可以直接估算出来,通常该电流就是偏置电路的基准电流,电路中与之相关联的电流源(如镜像电流源、比例电流源等)部分,就是偏置电路。将偏置电路分离出来,剩下部分一般为三级放大电路,按信号的流通方向,以“输入”和“输出”为线索,既可将三级分开,又可得出每一级属于哪种基本放大电路。为了克服温漂,集成运放的输入级几乎毫无例外地采用差分放大电路;为了增大放大倍数,中间级多采用共射(共源)放大电路;为了提高带负载能力且具有尽可能大的不失真输出电压范围,输出级多采用互补式电压跟随电路。

1、F007 电路分析

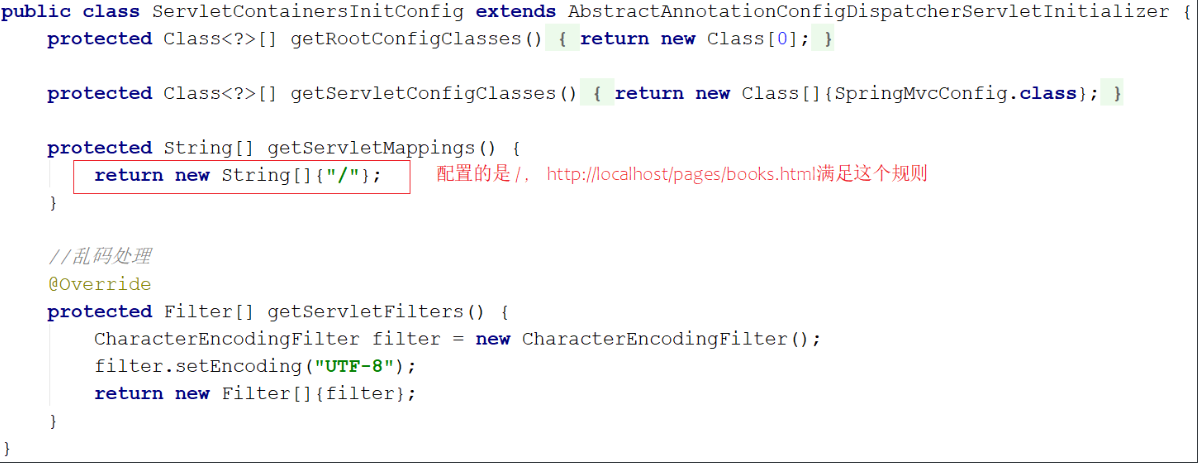

F007 是通用型集成运放,其电路如图4.3.1所示,它由

±

15

V

±15\,\textrm V

±15V 两路电源供电。从图中可以看出,从

+

V

C

C

+V_{CC}

+VCC 经

T

12

T_{12}

T12、

R

5

R_5

R5 和

T

11

T_{11}

T11 到

−

V

C

C

-V_{CC}

−VCC 所构成的回路的电流能够直接估算出来,因而

R

5

R_5

R5 中的电流为偏置电路的基准电流。

T

10

T_{10}

T10 与

T

11

T_{11}

T11 构成微电流源,而且

T

10

T_{10}

T10 的集电极电流

I

C

10

I_{C10}

IC10 等于

T

9

T_9

T9 管集电极电流

I

C

9

I_{C9}

IC9 与

T

3

T_3

T3、

T

4

T_4

T4 的基极电流

I

B

3

I_{B3}

IB3、

I

B

4

I_{B4}

IB4 之和,即

I

C

10

=

I

C

9

+

I

B

3

+

I

B

4

I_{C10}=I_{C9}+I_{B3}+I_{B4}

IC10=IC9+IB3+IB4;

T

8

T_8

T8 与

T

9

T_9

T9 为镜像关系,为第一级提供静态电流;

T

13

T_{13}

T13 与

T

12

T_{12}

T12 为镜像关系,为第二、三级提供静态电流。F007 的偏置电路如图中所标注。将偏置电路分离出来后,可得到 F007 的放大电路部分,如图4.3.2所示。根据信号的流通方向可将其分为三级,下面就各级作具体分析。

F007 是通用型集成运放,其电路如图4.3.1所示,它由

±

15

V

±15\,\textrm V

±15V 两路电源供电。从图中可以看出,从

+

V

C

C

+V_{CC}

+VCC 经

T

12

T_{12}

T12、

R

5

R_5

R5 和

T

11

T_{11}

T11 到

−

V

C

C

-V_{CC}

−VCC 所构成的回路的电流能够直接估算出来,因而

R

5

R_5

R5 中的电流为偏置电路的基准电流。

T

10

T_{10}

T10 与

T

11

T_{11}

T11 构成微电流源,而且

T

10

T_{10}

T10 的集电极电流

I

C

10

I_{C10}

IC10 等于

T

9

T_9

T9 管集电极电流

I

C

9

I_{C9}

IC9 与

T

3

T_3

T3、

T

4

T_4

T4 的基极电流

I

B

3

I_{B3}

IB3、

I

B

4

I_{B4}

IB4 之和,即

I

C

10

=

I

C

9

+

I

B

3

+

I

B

4

I_{C10}=I_{C9}+I_{B3}+I_{B4}

IC10=IC9+IB3+IB4;

T

8

T_8

T8 与

T

9

T_9

T9 为镜像关系,为第一级提供静态电流;

T

13

T_{13}

T13 与

T

12

T_{12}

T12 为镜像关系,为第二、三级提供静态电流。F007 的偏置电路如图中所标注。将偏置电路分离出来后,可得到 F007 的放大电路部分,如图4.3.2所示。根据信号的流通方向可将其分为三级,下面就各级作具体分析。

(1)输入级

输入信号

u

I

u_I

uI 加在

T

1

T_1

T1 和

T

2

T_2

T2 管的基极,而从

T

4

T_4

T4 管(即

T

6

T_6

T6 管)的集电极输出信号,故输入级是双端输入、单端输出的差分放大电路,完成了整个电路的对地输出的转换。

T

1

T_1

T1 与

T

2

T_2

T2、

T

3

T_3

T3 与

T

4

T_4

T4 管两两特性对称,构成共集-共基电路,从而提高电路的输入电阻,改善频率响应。

T

1

T_1

T1 与

T

2

T_2

T2 管为纵向管,

β

\beta

β 大;

T

3

T_3

T3 与

T

4

T_4

T4 管为横向管,

β

\beta

β 小但耐压高;

T

5

T_5

T5、

T

6

T_6

T6 与

T

7

T_7

T7 管构成的电流源电路作为差分放大电路的有源负载;因此输入级可承受较高的输入电压并具有较强的放大能力。

T

5

T_5

T5、

T

6

T_6

T6 与

T

7

T_7

T7 构成的电流源电路不但作为有源负载,而且将

T

3

\pmb{T_3}

T3 管集电极动态电流转换为输出电流

Δ

i

B

16

\pmb{\Delta i_{B16}}

ΔiB16 的一部分。由于电路的对称性,当有差模信号输入时,

Δ

i

C

3

=

−

Δ

i

C

4

\Delta i_{C3}=-\Delta i_{C4}

ΔiC3=−ΔiC4,

Δ

i

C

5

≈

Δ

i

C

3

\Delta i_{C5}\approx\Delta i_{C3}

ΔiC5≈ΔiC3(忽略

T

7

T_7

T7 管的基极电流),

Δ

i

C

5

=

Δ

i

C

6

\Delta i_{C5}=\Delta i_{C6}

ΔiC5=ΔiC6(因为

R

1

=

R

3

R_1=R_3

R1=R3),因而

Δ

i

C

6

≈

−

Δ

i

C

4

\Delta i_{C6}\approx -\Delta i_{C4}

ΔiC6≈−ΔiC4,所以

Δ

i

B

16

=

Δ

i

C

4

−

Δ

i

C

6

≈

2

Δ

i

C

4

\Delta i_{B16}=\Delta i_{C4}-\Delta i_{C6}\approx2\Delta i_{C4}

ΔiB16=ΔiC4−ΔiC6≈2ΔiC4,输出电流加倍,当然会使电压放大倍数增大。电流源电路还对共模信号起抑制作用,当共模信号输入时,

Δ

i

C

3

=

Δ

i

C

4

\Delta i_{C3}=\Delta i_{C4}

ΔiC3=ΔiC4,而

Δ

i

C

6

=

Δ

i

C

5

≈

Δ

i

C

3

\Delta i_{C6}=\Delta i_{C5}\approx\Delta i_{C3}

ΔiC6=ΔiC5≈ΔiC3(忽略

T

7

T_7

T7 管的基极电流),

Δ

i

B

16

=

Δ

i

C

4

−

Δ

i

C

6

≈

0

\Delta i_{B16}=\Delta i_{C4}-\Delta i_{C6}\approx0

ΔiB16=ΔiC4−ΔiC6≈0,可见,共模信号基本不传递到下一级,提高了整个电路的共模抑制比。

此外,当某种原因使输入级静态电流增大时,

T

8

T_8

T8 与

T

9

T_9

T9 管集电极电流会相应增大,但因为

I

C

10

=

I

C

9

+

I

B

3

+

I

B

4

I_{C10}=I_{C9}+I_{B3}+I_{B4}

IC10=IC9+IB3+IB4,且

I

C

10

I_{C10}

IC10 基本恒定,所以

I

C

9

I_{C9}

IC9 的增大势必使

I

B

3

I_{B3}

IB3、

I

B

4

I_{B4}

IB4 减小,从而使输入级静态电流

I

C

1

I_{C1}

IC1、

I

C

2

I_{C2}

IC2、

I

C

3

I_{C3}

IC3、

I

C

4

I_{C4}

IC4 减小,使它们基本不变。当某种原因使输入级静态电流减小时,各电流的变化与上述过程相反。

综上所述,输入级是一个输入电阻大、输入端耐压高、对共模信号抑制能力强、有较大差模放大倍数的双端输入、单端输出差分放大电路。

(2)中间级

中间级是以

T

16

T_{16}

T16 和

T

17

T_{17}

T17 组成的复合管为放大管,以电流源为集电极负载的共射放大电路,具有很强的放大能力。

(3)输出级

输出级是准互补电路,

T

18

T_{18}

T18 和

T

19

T_{19}

T19 复合而成的 PNP 型管与 NPN 型管

T

14

T_{14}

T14 构成互补形式,为了弥补它们的非对称性,在发射极加了两个阻值不同的电阻

R

9

\pmb{R_9}

R9 和

R

10

\pmb{R_{10}}

R10。

R

7

R_7

R7、

R

8

R_8

R8 和

T

15

T_{15}

T15 构成

U

B

E

U_{BE}

UBE 倍增电路,为输出级设置合适的静态工作点,以消除交越失真。

R

9

\pmb{R_9}

R9 和

R

10

\pmb{R_{10}}

R10 还作为输出电流

i

O

\pmb{i_O}

iO(发射极电流)的采样电阻与

D

1

\pmb{D_1}

D1、

D

2

\pmb{D_2}

D2 共同构成过电流保护电路,这是因为

T

14

T_{14}

T14 导通时

R

7

R_7

R7 上电压与二极管

D

1

D_1

D1 上电压之和等于

T

14

T_{14}

T14 管 b - e 间电压与

R

9

R_9

R9 上电压值和,即

u

R

7

+

u

D

1

=

u

B

E

14

+

i

O

R

9

u_{R_7}+u_{D1}=u_{BE14}+i_OR_9

uR7+uD1=uBE14+iOR9当

i

O

i_O

iO 未超过额定值时,

u

D

1

<

U

O

N

u_{D1}<U_{ON}

uD1<UON,

D

1

D_1

D1 截止;而当

i

O

i_O

iO 过大时,

R

9

R_9

R9 上电压变大使

D

1

D_1

D1 导通,为

T

14

T_{14}

T14 的基极分流,从而限制了

T

14

T_{14}

T14 的发射极电流,保护了

T

14

T_{14}

T14 管。

D

2

D_2

D2 在

T

18

T_{18}

T18 和

T

19

T_{19}

T19 导通时起保护作用。

在图4.3.1中,电容 C 的作用是相位补偿;外接电位器

R

w

R_w

Rw 起调零作用,改变其滑动端,可改变

T

5

T_5

T5 和

T

6

T_6

T6 管的发射极电阻,以调整输入级的对称程度。

F007 的电压放大倍数可达几十万倍,输入电阻可达

2

MΩ

2\,\textrm {MΩ}

2MΩ 以上。

2、F324 电路分析

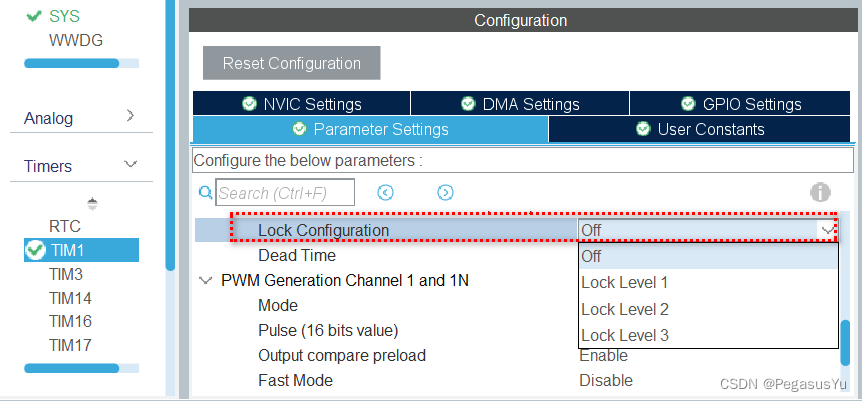

F324 是四个独立的通用型运算放大电路集成在一个芯片上,它既可以单电源(3 ~ 30 V)工作,又可以双电源(±1.5 ~ ±15 V)工作,而且静态功耗少。电路原理图如图4.3.3所示。基准电流

I

R

I_R

IR 来源于 F324 内部的基准电流源电路,它为四个运放同时提供基准电流。多集电极晶体管

T

11

T_{11}

T11、

T

12

T_{12}

T12 和

T

13

T_{13}

T13 利用集电区面积不同而构成比例电流源,为第一、二级提供静态电流。

T

20

T_{20}

T20 与

T

19

T_{19}

T19 构成镜像电流源,为末级提供静态电流。去掉偏置电路部分,并将

T

17

T_{17}

T17 等效成一个电阻,电路可简化成如图4.3.4所示的三级放大电路。

F324 是四个独立的通用型运算放大电路集成在一个芯片上,它既可以单电源(3 ~ 30 V)工作,又可以双电源(±1.5 ~ ±15 V)工作,而且静态功耗少。电路原理图如图4.3.3所示。基准电流

I

R

I_R

IR 来源于 F324 内部的基准电流源电路,它为四个运放同时提供基准电流。多集电极晶体管

T

11

T_{11}

T11、

T

12

T_{12}

T12 和

T

13

T_{13}

T13 利用集电区面积不同而构成比例电流源,为第一、二级提供静态电流。

T

20

T_{20}

T20 与

T

19

T_{19}

T19 构成镜像电流源,为末级提供静态电流。去掉偏置电路部分,并将

T

17

T_{17}

T17 等效成一个电阻,电路可简化成如图4.3.4所示的三级放大电路。 输入级是双端输入、单端输出的差分放大电路,

T

1

T_1

T1 与

T

2

T_2

T2 管为纵向 PNP 管,

β

\beta

β 大;

T

3

T_3

T3 与

T

4

T_4

T4 为横向 PNP 管,b - e 间耐压高;又采用了共集 - 共射形式;因而输入级有较强的放大能力,能承受较大的差模输入电压,并且具有较高的输入电阻。同时由于

T

15

T_{15}

T15 和

T

16

T_{16}

T16 管构成的电流源作为有源负载,将

T

3

T_3

T3 集电极电流的变化转换为输出电流,所以使单端输出电路对差模信号的放大能力接近双端输出的情况。

输入级是双端输入、单端输出的差分放大电路,

T

1

T_1

T1 与

T

2

T_2

T2 管为纵向 PNP 管,

β

\beta

β 大;

T

3

T_3

T3 与

T

4

T_4

T4 为横向 PNP 管,b - e 间耐压高;又采用了共集 - 共射形式;因而输入级有较强的放大能力,能承受较大的差模输入电压,并且具有较高的输入电阻。同时由于

T

15

T_{15}

T15 和

T

16

T_{16}

T16 管构成的电流源作为有源负载,将

T

3

T_3

T3 集电极电流的变化转换为输出电流,所以使单端输出电路对差模信号的放大能力接近双端输出的情况。

中间级是共集 - 共射放大电路,

T

5

T_5

T5 与

T

6

T_6

T6 管构成两级射极输出电路,使第二级输入电阻很大,从而提高了前级的电压放大倍数。与此同时,在输入级输出电流有限的情况,由于

T

5

T_5

T5 与

T

6

T_6

T6 管的电流放大作用,使

T

7

T_7

T7 获得更大的基极动态电流,从而使中间级具有很强的放大能力。

输出级的工作情况与 F007 有所不同。当负载电阻接入时(见图中虚线所示),在单电源供电的情况下,输出级是由

T

8

T_8

T8 与

T

9

T_9

T9 管构成的共集放大电路,50 μA 电流源为它提供静态电流。此时

T

7

T_7

T7 管的集电极电位

u

C

7

=

u

B

E

8

+

u

B

E

9

+

u

R

2

+

u

O

u_{C7}=u_{BE8}+u_{BE9}+u_{R_2}+u_O

uC7=uBE8+uBE9+uR2+uO而输出端电位

u

O

u_O

uO 即为

T

10

T_{10}

T10 管发射极电位,所以

T

10

T_{10}

T10 管发射结承受反向电压,使

T

10

\pmb{T_{10}}

T10 截止。为了获得尽可能大的最大不失真输出电压,应使静态时

u

O

=

V

C

C

/

2

\pmb{u_O=V_{CC}/2}

uO=VCC/2,一般通过在 F324 的输入端加偏置电压来实现。当通过耦合电容接负载电阻时,就构成 OTL 互补电路。

当双电源供电时,输出级的工作情况与 F007 相同。应当指出,由于电路中对于

T

10

T_{10}

T10 管没有消除交越失真的偏置电路,输出会出现轻微的交越失真。

电阻

R

2

\pmb{R_2}

R2 一方面用于补偿输出级中 NPN 管与 PNP 管的不对称性,另一方面与

T

21

\pmb{T_{21}}

T21 构成正向过流保护电路。正向输出电流与

R

2

R_2

R2 上电流相等,因此

R

2

R_2

R2 是输出电流的采样电阻。正常工作时

T

21

T_{21}

T21 管处于截止状态,一旦输出电流过大,

R

2

R_2

R2 上的电压使

T

21

T_{21}

T21 管导通,它的集电极电流使

T

8

T_8

T8 管的基极驱动电流减小,从而将

T

9

T_9

T9 管的发射极电流

i

E

9

i_{E9}

iE9 限制为

u

B

E

21

/

R

2

u_{BE21}/R_2

uBE21/R2。

电容

C

C

C 起相位补偿作用。从图中所标注的电流可以看出,F324 的静态功耗很小。即使在单电源供电情况下,零输入时输出电压也可以接近于零。

通过对 F007 和 F324 电路原理图的分析,一方面了解了通用型晶体管集成运放电路的工作原理,另一方面得到集成放大电路的一般规律。

应当特别指出,分析集成运放电路的结构特点和工作原理是为了更好地理解它们的性能特点及主要参数,以便合理地使用它们。这里的重点不是设计和改进集成电路,因此只需对电路原理有个基本了解即可。

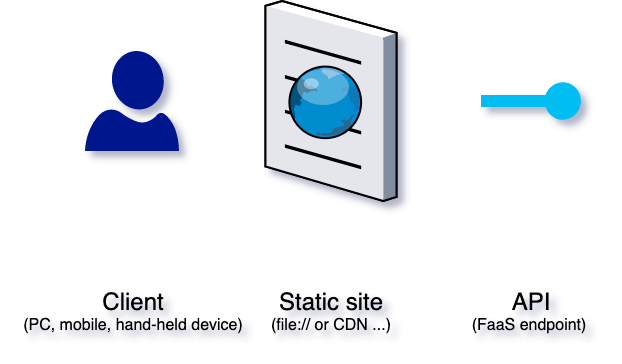

二、单极型集成运放

在测量设备中,常需要高输入电阻的集成运放,其输入电流小到 10 pA 以下,这对于任何双极型集成运放都无法实现,必须采用场效应管构成的集成运放。由于同时制作 N 沟道和 P 沟道互补对称管工艺较易实现,所以 CMOS 技术广泛用于集成运放。CMOS 集成运放的输入电阻高达

1

0

10

Ω

10^{10}\,Ω

1010Ω 以上,并可在很宽的电源电压范围内工作。它们所需的芯片面积只是可比的双极型设计的 1/3 ~ 1/5,因此 CMOS 电路的集成度更高。

与 F324 一样,C14573 是四个独立的运放制作在一个芯片上的器件,其电路原理图如图4.3.5所示,它全部由增强型 MOS 管构成,与晶体管集成运放电路结构相类比可知。

T

1

T_1

T1、

T

2

T_2

T2 和

T

7

T_7

T7 管构成多路电流源,在已知

T

1

T_1

T1 管的开启电压的前提下,利用外接电阻可以求出基准电压

I

R

I_R

IR,一般选择

I

R

I_R

IR 为 20 ~ 200 μA。根据

T

1

T_1

T1、

T

2

T_2

T2 和

T

7

T_7

T7 管的结构尺寸可以得到

T

3

T_3

T3、

T

4

T_4

T4 与

T

8

T_8

T8 管的漏极电流,它们为放大电路提供静态电流。把偏置电路简化后,便可得到如图4.3.6所示的放大电路部分。由图可知,C14573 是两级放大电路。

与 F324 一样,C14573 是四个独立的运放制作在一个芯片上的器件,其电路原理图如图4.3.5所示,它全部由增强型 MOS 管构成,与晶体管集成运放电路结构相类比可知。

T

1

T_1

T1、

T

2

T_2

T2 和

T

7

T_7

T7 管构成多路电流源,在已知

T

1

T_1

T1 管的开启电压的前提下,利用外接电阻可以求出基准电压

I

R

I_R

IR,一般选择

I

R

I_R

IR 为 20 ~ 200 μA。根据

T

1

T_1

T1、

T

2

T_2

T2 和

T

7

T_7

T7 管的结构尺寸可以得到

T

3

T_3

T3、

T

4

T_4

T4 与

T

8

T_8

T8 管的漏极电流,它们为放大电路提供静态电流。把偏置电路简化后,便可得到如图4.3.6所示的放大电路部分。由图可知,C14573 是两级放大电路。 第一级是以 P 沟道管

T

3

T_3

T3 和

T

4

T_4

T4 为放大管、以

T

5

T_5

T5 和

T

6

T_6

T6 管构成的电流源为有源负载、采用共源形式的双端输入、单端输出差分放大电路,有源负载使单端输出电路的动态输出电流近似等于双端输出时的情况。由于第二级电路从

T

8

T_8

T8 的栅极输入,其输入电阻非常大,所以使第一级具有很强的电压放大能力。

第一级是以 P 沟道管

T

3

T_3

T3 和

T

4

T_4

T4 为放大管、以

T

5

T_5

T5 和

T

6

T_6

T6 管构成的电流源为有源负载、采用共源形式的双端输入、单端输出差分放大电路,有源负载使单端输出电路的动态输出电流近似等于双端输出时的情况。由于第二级电路从

T

8

T_8

T8 的栅极输入,其输入电阻非常大,所以使第一级具有很强的电压放大能力。

第二级是共源放大电路,以 N 沟道管

T

8

T_8

T8 为放大管,漏极带有源负载,因此也具有很强的电压放大能力。但它的输出电阻很大,因而带负载能力较差,是为高阻抗负载而设计的,适用于以场效应管为负载的电流。

电容

C

C

C 起相位补偿作用。

在使用时,工作电源电压

V

D

D

V_{DD}

VDD 与

V

S

S

V_{SS}

VSS 之间的差值应满足

5

V

≤

(

V

D

D

−

V

S

S

)

≤

15

V

5\,\textrm V\leq(V_{DD}-V_{SS})\leq15\,\textrm V

5V≤(VDD−VSS)≤15V;可以单电源供电(正、负均可);也可以双电源供电,并允许正负电源不对称。使用者可根据对输出电压动态范围的要求选择电源电压的数值。