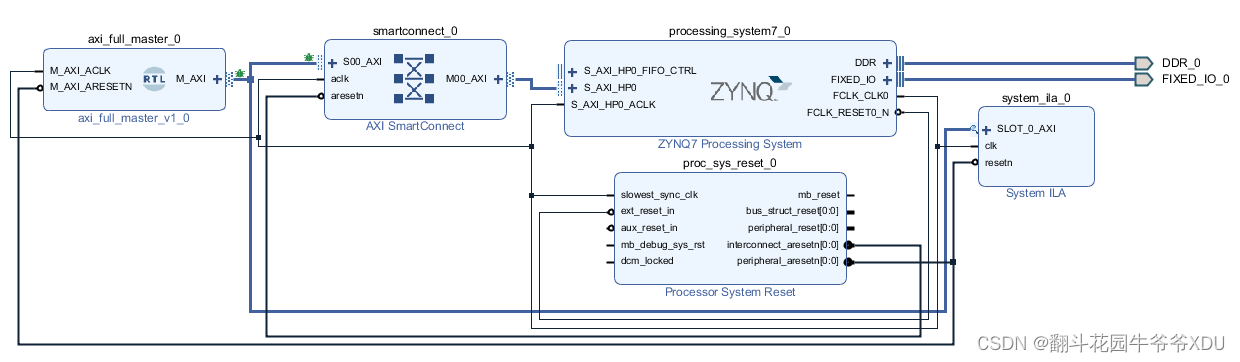

AXI_HP接口

通过AXI_HP接口,可直接通过AXI_FULL协议向DDR中通过DMA传输数据。

BD设计

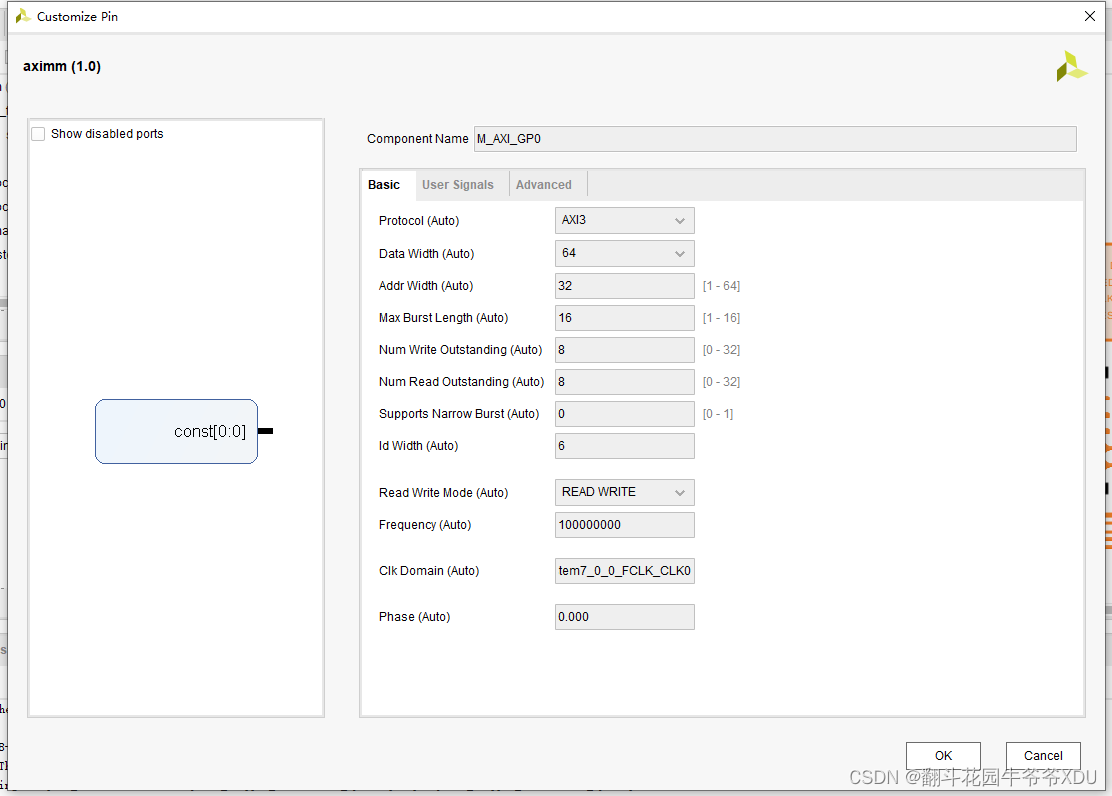

AXI_HP接口设置

AXI_Master代码

module axi_full_master #

(

parameter C_M_TARGET_SLAVE_BASE_ADDR = 32'h40000000,

parameter integer C_M_AXI_BURST_LEN = 16,

parameter integer C_M_AXI_ID_WIDTH = 1,

parameter integer C_M_AXI_ADDR_WIDTH = 32,

parameter integer C_M_AXI_DATA_WIDTH = 64,

parameter integer C_M_AXI_AWUSER_WIDTH = 0,

parameter integer C_M_AXI_ARUSER_WIDTH = 0,

parameter integer C_M_AXI_WUSER_WIDTH = 0,

parameter integer C_M_AXI_RUSER_WIDTH = 0,

parameter integer C_M_AXI_BUSER_WIDTH = 0

)

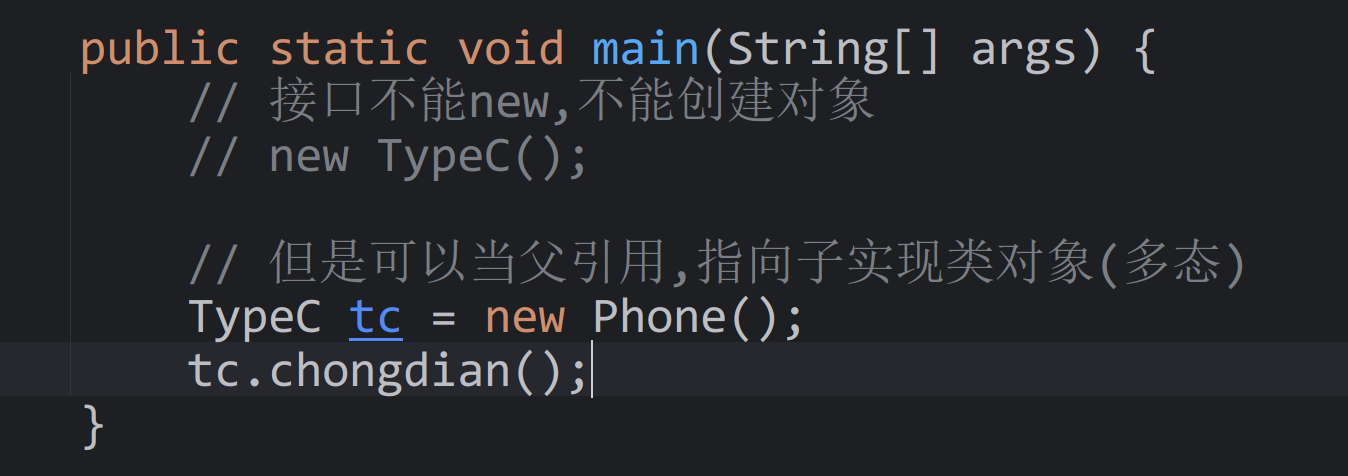

//编码测试

(

input wire M_AXI_ACLK ,

input wire M_AXI_ARESETN ,

output wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_AWID ,

output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_AWADDR ,

output wire [7 : 0] M_AXI_AWLEN ,

output wire [2 : 0] M_AXI_AWSIZE ,

output wire [1 : 0] M_AXI_AWBURST ,

output wire M_AXI_AWLOCK ,

output wire [3 : 0] M_AXI_AWCACHE ,

output wire [2 : 0] M_AXI_AWPROT ,

output wire [3 : 0] M_AXI_AWQOS ,

output wire [C_M_AXI_AWUSER_WIDTH-1 : 0] M_AXI_AWUSER ,

output wire M_AXI_AWVALID ,

input wire M_AXI_AWREADY ,

output wire [C_M_AXI_DATA_WIDTH-1 : 0] M_AXI_WDATA ,

output wire [C_M_AXI_DATA_WIDTH/8-1 : 0] M_AXI_WSTRB ,

output wire M_AXI_WLAST ,

output wire [C_M_AXI_WUSER_WIDTH-1 : 0] M_AXI_WUSER ,

output wire M_AXI_WVALID ,

input wire M_AXI_WREADY ,

input wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_BID ,

input wire [1 : 0] M_AXI_BRESP ,

input wire [C_M_AXI_BUSER_WIDTH-1 : 0] M_AXI_BUSER ,

input wire M_AXI_BVALID ,

output wire M_AXI_BREADY ,

output wire [C_M_AXI_ID_WIDTH-1 : 0] M_AXI_ARID ,

output wire [C_M_AXI_ADDR_WIDTH-1 : 0] M_AXI_ARADDR ,

output wire [7 : 0] M_AXI_ARLEN ,

output wire [2 : 0] M_AXI_ARSIZE ,

output wire [1 : 0] M_AXI_ARBURST ,

output wire M_AXI_ARLOCK ,

output wire [3 : 0] M_AXI_ARCACHE ,

output wire [2

![洛谷:P3068 [USACO13JAN] Party Invitations S(枚举、前缀和)](https://img-blog.csdnimg.cn/direct/11aac5edd8ef41b7914307871ae1063a.png)