行为Verilog

Vivado synthesis支持行为Verilog硬件描述语言(VHDL),除了如另外指出的。

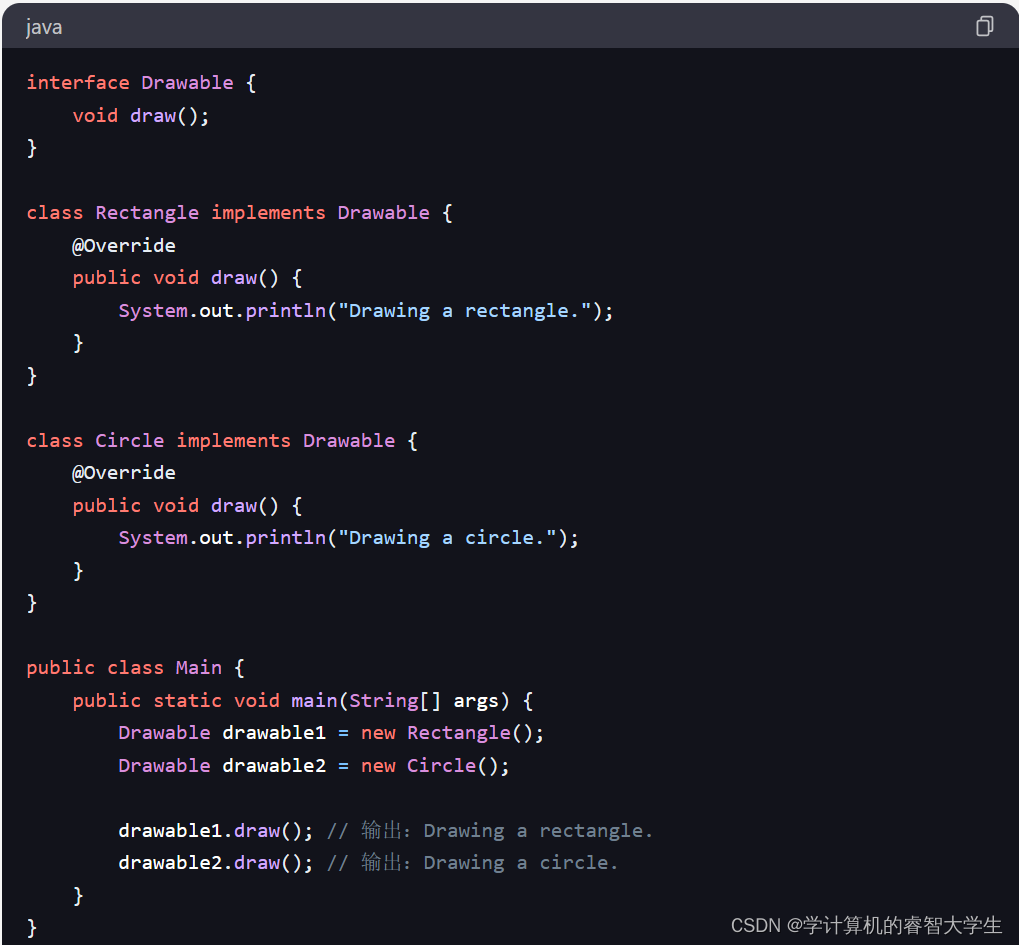

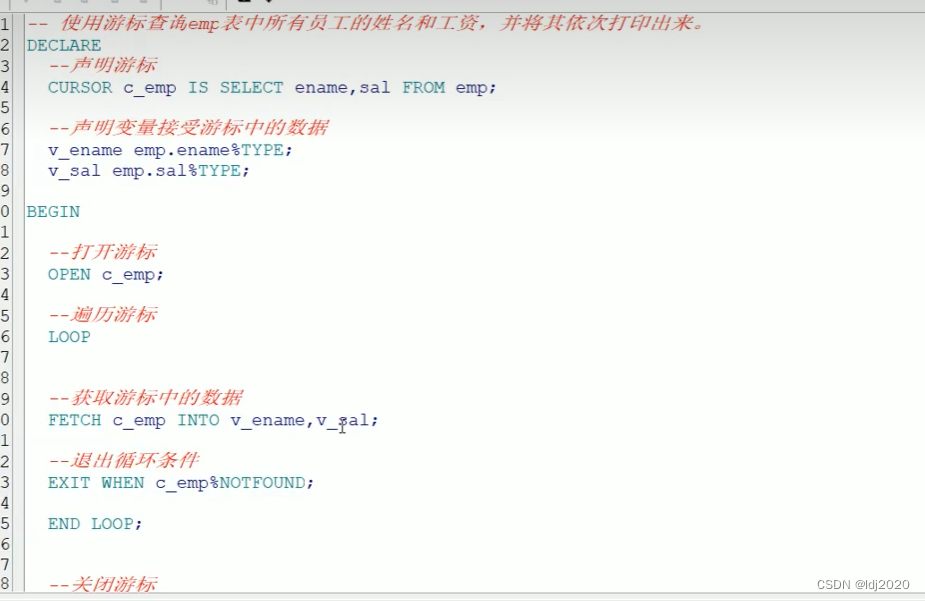

行为Verilog中的变量

•行为Verilog中的变量声明为整数。

•这些声明仅用于测试代码。Verilog提供诸如reg和用于实际硬件描述的导线。

•reg和wire之间的差异取决于变量是否在过程块(reg)或在连续分配(wire)中。

○ reg和wire的默认宽度都是一位(标量)。

○ 要为声明的reg或导线指定N位宽度(矢量),请使用左右位位置用冒号分隔的方括号定义。

○ 在Verilog-2001中,reg和wire数据类型可以是有符号的,也可以是无符号的。

变量声明示例

初始值

在Verilog-2001中声明寄存器时对其进行初始化。

•初始值:

○ 是一个常数。

○ 不能依赖于早期的初始值。

○ 不能是函数或任务调用。

○ 可以是传播到寄存器的参数值。

○ 指定矢量的所有位。

•当您在声明中将寄存器指定为初始值时,Vivado synthesis会设置此值在全局复位或通电时在寄存器的输出上。

•当以这种方式分配值时:

○ 该值在Verilog文件中作为寄存器上的INIT属性携带。

○ 该值与任何本地重置无关。

将初始值分配给寄存器

将设置/重置(初始)值分配给寄存器。

•当寄存器复位线变为适当值时,将值分配给寄存器。看见下面的编码示例。

•将初始值分配给变量时:

○ 该值被实现为触发器,其输出由本地重置控制。

Reg和Wire的阵列

Verilog允许reg和wire的阵列。

数组示例一

这个编码示例描述了一个由32个元素组成的数组。每个元素都有4位宽。

reg[3:0]mem_array[31:0];

阵列示例二

该编码示例描述了64个8位宽元素的阵列。这些元素可以是仅在结构Verilog代码中分配。

wire[7:0]mem_array[63:0];

多维阵列

Vivado合成支持最多二维的多维数组类型。

•多维阵列可以是:

○ 任何网络

○ 任何变量数据类型

•使用数组进行代码分配和算术运算。

•一次不能选择数组中的多个元素。

•不能将多维数组传递给:

○ 系统任务或功能

○ 常规任务或功能

多维阵列示例一

此编码示例描述了一个256 x 16线元素的阵列,每个元素8位。这些元素只能在结构Verilog代码中分配。

多维阵列示例二

此编码示例描述了256 x 8个寄存器元件的阵列,每个寄存器元件64位宽。这些

元素可以在行为Verilog代码中分配。

reg[63:0]regarray2[255:0][7:0];

数据类型

位数据类型的Verilog表示包含以下值:

•0=逻辑零

•1=逻辑一

•x=未知逻辑值

•z=高阻抗

支持的数据类型

•净

○ 金属丝

○ 魔杖

○ wor

•寄存器

○ 规则

○ 整数

•常数

○ 参数

○ 多维阵列(存储器)

网络和寄存器

Net和Registers可以是:

•单比特(标量)

•多位(矢量)

行为数据类型示例

此编码示例显示了在的声明部分中找到的示例Verilog数据类型Verilog模块。

法律声明

Vivado synthesis支持行为Verilog法律声明。

•以下陈述(变量和信号分配)是合法的:

○ variable=表达式

○ if(条件)语句

○ else语句

○ case(表达式),例如:

○ for(variable=表达式;条件;variable=变量+表达式)语句

○ while(condition)语句

○ 永久声明

○ 功能和任务

•所有变量都声明为integer或reg。

•变量不能声明为连线。

表达

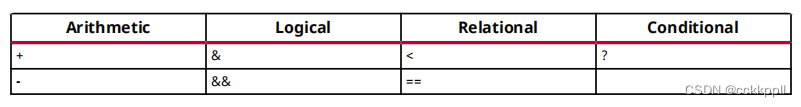

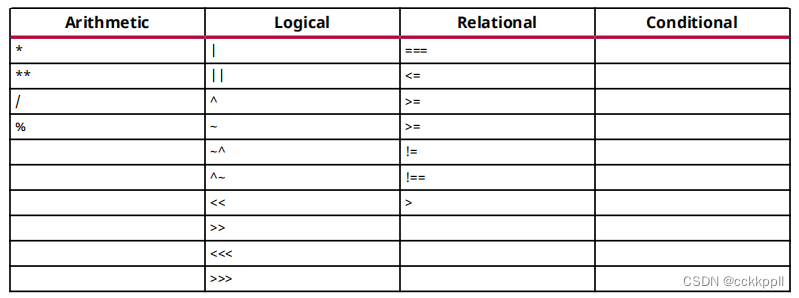

行为Verilog表达式包括:

•常数

•具有以下运算符的变量:

○ 算术

○ 必然的

-逐位

必然的

○ 关系的

○ 有条件的

逻辑运算符

逻辑运算符所属的类别(按位还是按逻辑)取决于它是否应用于涉及几个比特或单个比特的表达式。

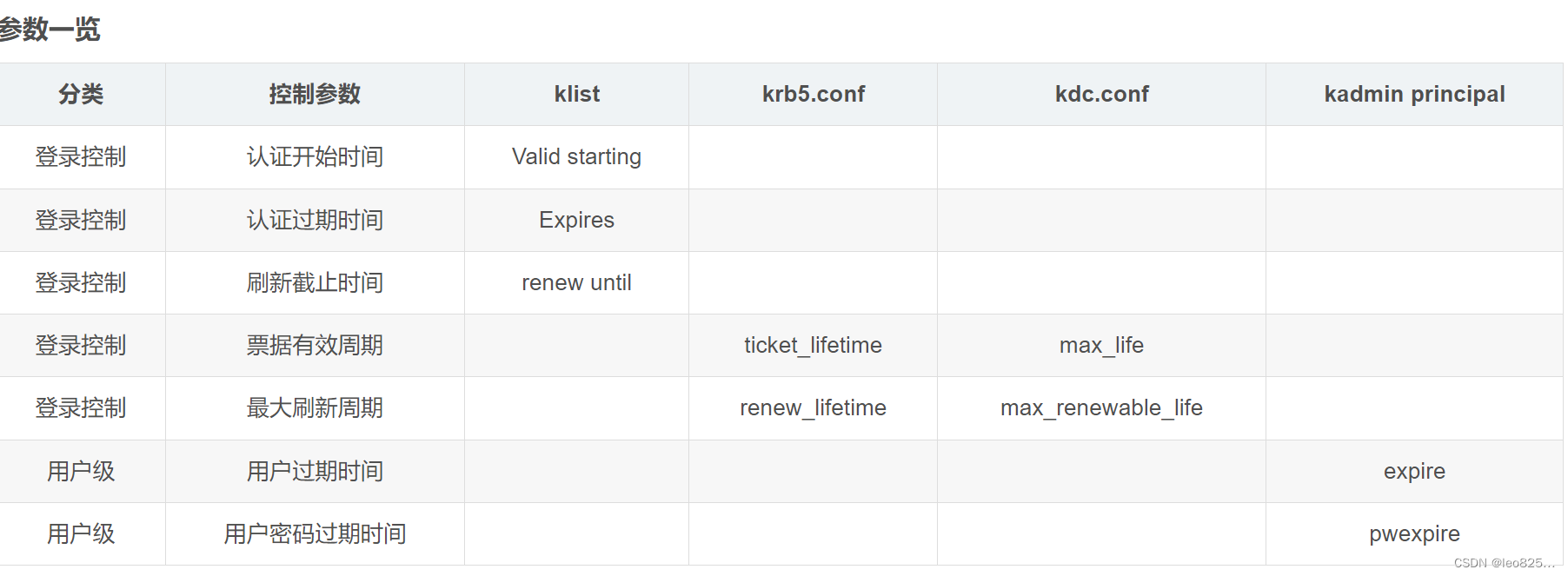

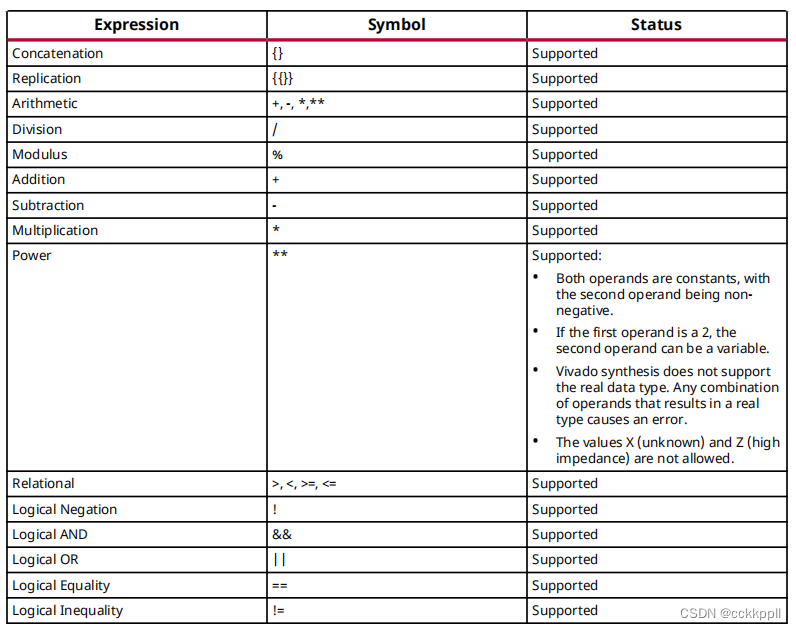

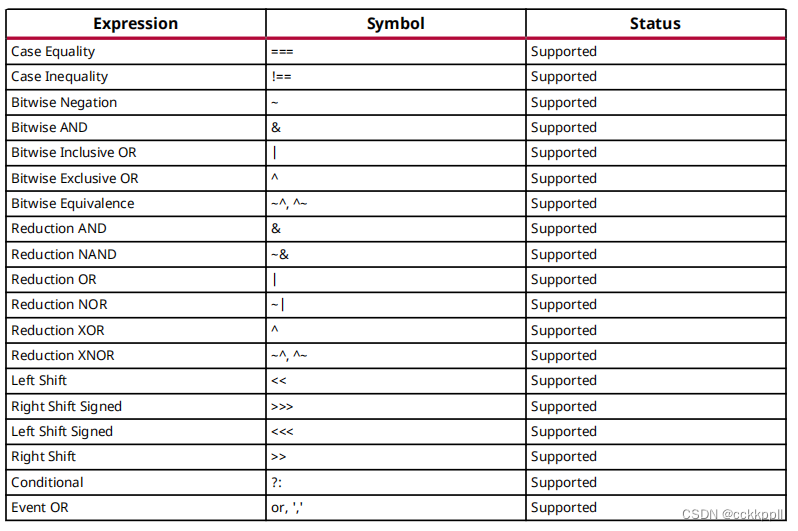

支持的运算符

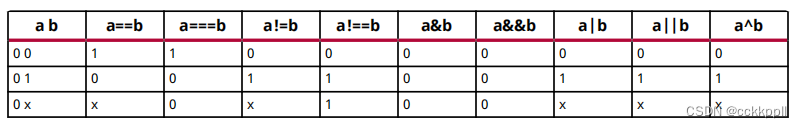

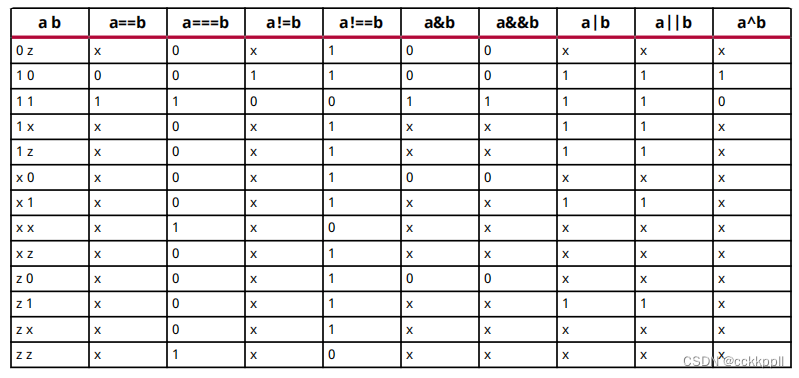

计算表达式

下表中的(==)和(!==)运算符为:

•特殊的比较运算符。

•用于模拟,查看变量是否分配了值(x)或(z)。

•通过合成处理为(==)或(!=)。

有关Verilog的更多信息,请参阅Vivado Design Suite用户指南:逻辑仿真(UG900)Vivado模拟的格式。

基于最常用运算符的求值表达式

阻碍

Vivado合成支持一些块语句,如下所示:

•块语句将语句分组在一起。它们由开始和结束关键字指定。块语句按照块中列出的顺序执行语句。

•Vivado合成仅支持顺序块。

•Vivado合成不支持并行块。

•所有过程语句都出现在模块内部定义的块中。

•两种程序块是初始块和始终块

•Verilog在每个块中使用开始和结束关键字来封装语句。因为初始块在合成过程中被忽略,总是只描述块。

•总是块通常采用以下格式。每一句话都是一项程序性任务以分号结尾的行。