目录

1.概述

2.MCU大厂的选择

2.1 瑞萨自研STT-MRAM

2.2 ST专注PCM

2.3 英飞凌和台积电联手RRAM

2.4 NXP如何计划eNVM

3.小结

1.概述

上篇文章,我们简述了当前主流的存储器技术,现在我们来讲讲各大MCU大厂的技术选择

2.MCU大厂的选择

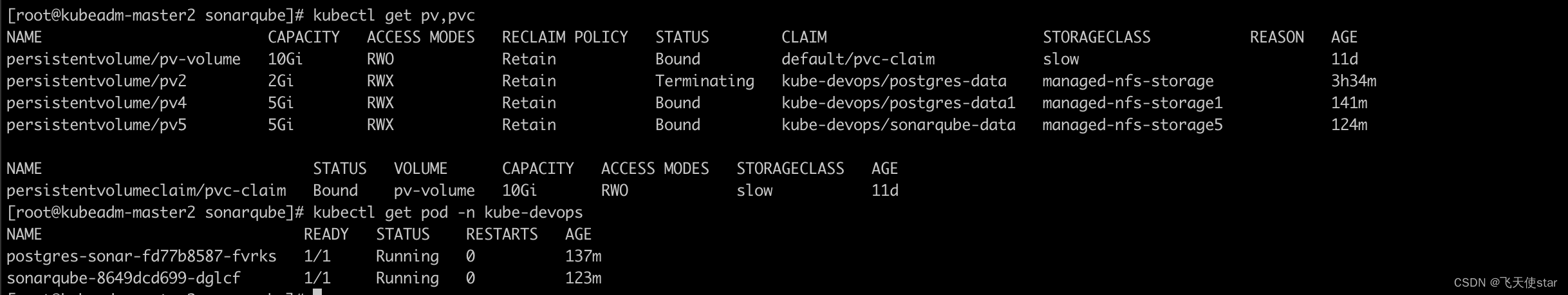

瑞萨日前宣布,公司已基于STT-MRAM的电路技术开发出具有快速读写能力的测试芯片。该MCU 测试芯片采用 22 纳米工艺制造,包括一个 10.8Mbit嵌入式 MRAM 存储单元阵列。它实现了超过 200 MHz 的随机读取访问频率和10.4MB/s的写入吞吐量。

2.1 瑞萨自研STT-MRAM

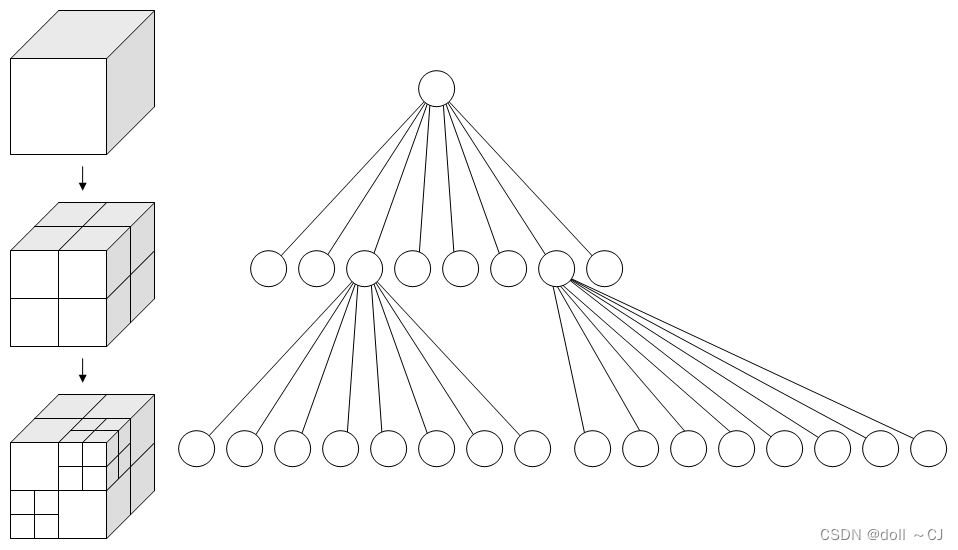

STT-MRAM的基本架构如下:

它使用MTJ(Magnetic Tunnel Junction --磁隧道结)存储信息,而不是传统的电荷存储方式。

每个MTJ包含两个铁磁层和一个隧道势垒层。其中一个铁磁层(Fixed Layer--蓝色)具有固定的磁性方向,而另一个铁磁层(Free Layer--绿色)可以通过外部电磁场或自旋传递转矩改变其磁性方向。如果两个铁磁层具有不同的方向,则MTJ电阻高,表明“逻辑1”状态。如果两层具有相同的方向,则MTJ电阻为低,表示“逻辑0”状态。

STT-MRAM通过将自旋极化电流直接穿过MTJ结构来改变自由层的磁方向,意味着使状态反转的阈值电流将随着MTJ的尺寸变小而减小。

2.2 ST专注PCM

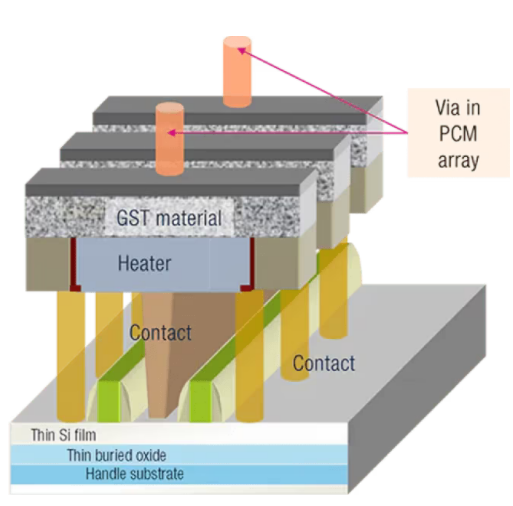

意法半导体的Stellar P\G系列使用PCM技术作为eNVM解决方案,应用到了28nm FD-SOI技术平台。所谓PCM,就是相变材料在焦耳热作用下在结晶体态和非晶态下转换,从而呈现不同阻态。

ST的PCM技术采用锗锑碲 (GST) 合金制造而成,且在制造过程中利用了材料可在非晶态和结晶态之间进行快速热控制变化的物理特性,分别对应逻辑"0"和逻辑"1"相对应。具体来讲可通过非晶态(逻辑0)的高电阻和结晶态(逻辑1)的低电阻进行电气区分。PCM支持在低电压下进行读写操作,并且具备单比特位可变更性,因此相较于eFlash更有优势。

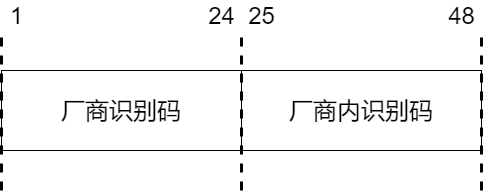

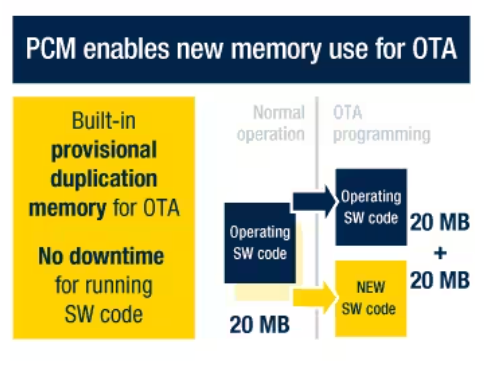

意法半导体在存储单元和GST合金上的专利布局,让其在汽车越来越多的OTA场景中抢占了先机,如下图:

2.3 英飞凌和台积电联手RRAM

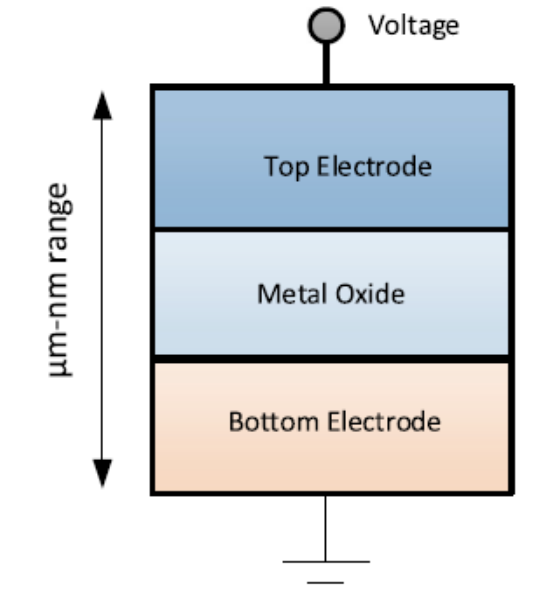

据英飞凌官网发布,TC4xx的NVM采用其与台积电联合研发的28nm RRAM技术。

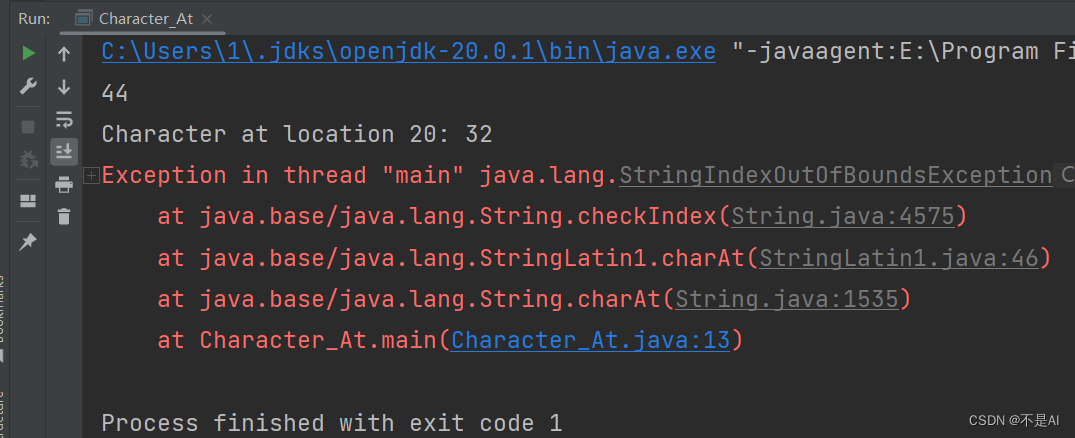

RRAM(也称ReRAM),作为结构最简单的存储技术其结构看上去像一个三明治,绝缘介质层(阻变层)被夹在两层金属之间,形成由上、下电极和阻变层构成金属-介质层-金属(metal-insulator-metal,简称MIM)三层结构。

阻变原理是基于器件阻变层中导电通路(一般称之为conductive filament, 导电细丝)实现的,即通过在上、下电极施加不同的脉冲电压激励,使介质层发生阻变,产生物理性变化。

导电细丝会在阻变层中呈现导通或断开两种状态:非易失性的低阻态(Low Resistance State,LRS)或高阻态(High Resistance State,HRS),从而实现了“0”,“1”状态的区分和存储。

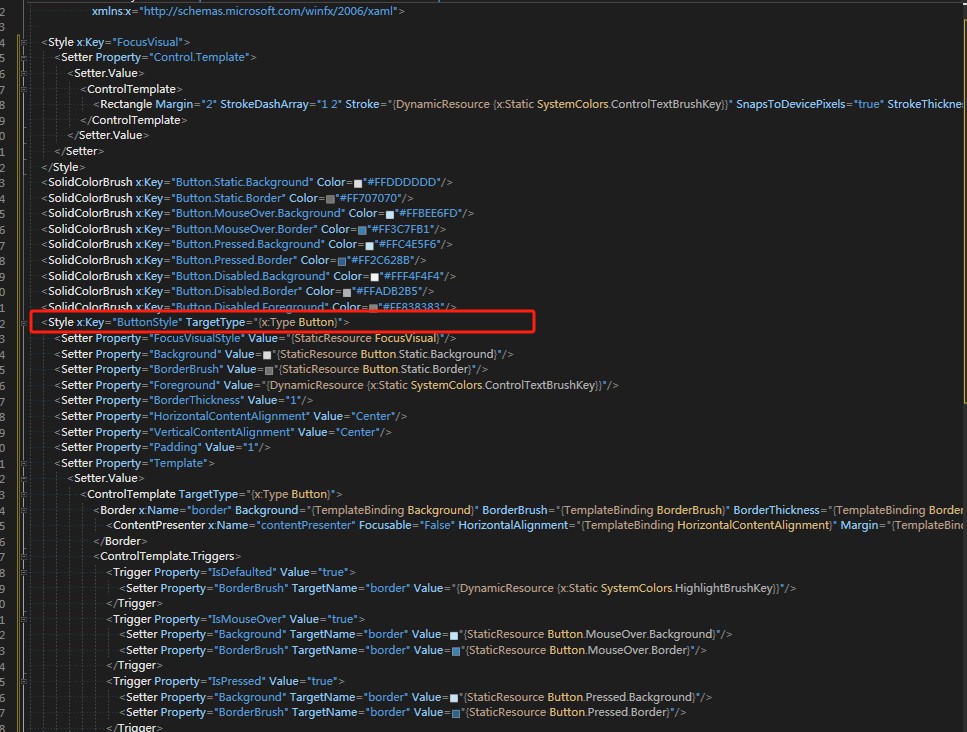

2.4 NXP如何计划eNVM

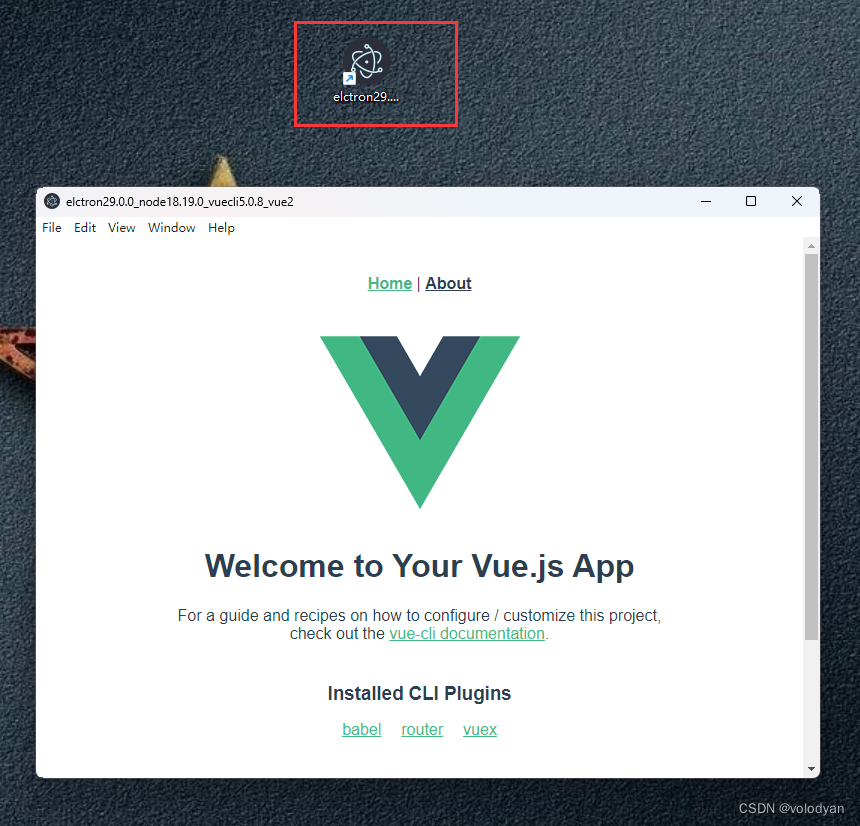

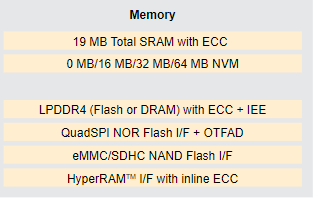

S32Z和S32E处理器采用TSMC 16nm FinFET技术实现。如下图:

目前还没有掌握到它这64MB的NvM采用什么技术。

3.小结

可以看到,eFlash制程工艺对MCU的架构和产品迭代影响是巨大的。而国内MCU厂商要想实现弯道超车,设计是一方面,生产、工艺则是重中之重。

就好像我想在空中修一栋房子,想法是好的,前提是生产建造技术要能够支撑我的想法。

兵马未动,粮草先行。而针对MCU的国产替代,我理解是设计未动,工艺先行。