简介

PCIe中有4种复位机制,早期的3种被称为传统复位(Conventional Reset)。传统复位中的前2种又称为基本复位(Fundamental Resets),分别为冷复位(Cold Reset),暖复位(Warm Reset)。第3种复位为热复位(Hot Reset)。第4种复位被称为功能级复位(Function Level Reset),出现在PCIe 2.0规范中。

传统复位

2.1. 基本复位

基本复位由硬件处理,并且是复位整个设备,重新初始化所有硬件的逻辑、端口状态以及配置寄存器。唯一的例外是,有一组标识为"sticky"的寄存器位,因为要记录复位过程中的错误,所以其配套有辅助电源(Vaux)。如果主电源和辅助电源同时关闭,那么Stick寄存器也会复位。

两种基本复位的定义:

冷复位:启动设备主电源或重启设备主电源都会导致冷复位。

暖复位(可选):不关闭主电源下的触发。规范没有定义实现机制,厂商可自行选择是否添加此功能,并设计具体触发的机制,可以考虑通过检测电源状态来实现。

基本复位发生和退出时,正负电压端阻抗必须满足要求,发射端的阻抗和直流也必须满足要求,详见技术规范。

两种基本复位方法:

-

通过辅助边带信号PERST#(PCI Express Reset)触发。

-

如果未提供边带信号,则重启电源时,组件或插槽会自动产生复位。

2.2. PERST# 基本复位的产生

PERST#信号是边带信号,系统不一定设计有。芯片组可能提供PERST#信号,如下图ICH对外提供PERST#信号。当POWERGOOD信号触发时,ICH会发出PERST#信号。PERST#边带信号会接入所有PCIe设备。

当设备电源关闭,POWERGOOD信号触发,然后产生PERST#信号,这是一个冷复位。(此时设备电源也会同时开启)。

当设备电源开启,系统可以通过其他方式产生PERST#信号以实现暖复位。

2.3. 自主复位的产生

设备在主电源接通时,应该自己产生复位信号,然后对设备进行本地复位。如果设备检测到电源超出范围,也必须生成自主复位。

2.4. 链路从低功耗唤醒

当设备的主要电源被关闭作为电源管理策略的一部分时,如果设备设计用于发出唤醒信号,它可能能够请求恢复到完全供电状态。当电源恢复时,设备必须进行复位。系统的电源控制器可以通过激活PERST#引脚向设备发送复位信号,但如果没有这样做,或者设备不支持PERST#,则设备必须在感知到主电源重新连接时自主生成其自己的基本复位。

2.5. 热复位(带内复位)

热复位是通过在链路上发送特定的TS1消息来实现的。这些消息中的第5个符号的第0位被设置为1,以表示这是一个热复位消息。这些消息将在所有通道上广播,以确保所有链路邻居都能够接收到,并执行相应的操作以响应热复位。一旦完成发送,发送器和接收器将进入特定的状态以处理热复位。这个过程有助于在高速数据链路中进行重置操作,以确保链路的正确性和稳定性。

软件发起的热复位是通过在桥接设备的配置寄存器中设置特定的位来实现的。这个位被称为Secondary Bus Reset位。当此位被设置时,与该桥接设备相关联的所有设备都将接收到复位信号,并进行自我复位。这种复位操作通常由具有桥接功能的设备(例如Root Complex设备或交换机)执行,并且可以通过其控制寄存器进行触发。交换机在接收到热复位信号后将广播给其下游端口,并要求所有下游设备进行复位。这确保了整个链路中的所有设备都可以正确地响应热复位,并重新初始化其状态。

如上图,如果Root Compex或Switch被软件启用了热复位,那么Root Compex或Switch会对其所有下端设备发生热复位。

当热复位接收器检测到连续2个热复位的TS1消息埋,它会进入Hot Reset状态并持续2ms,然后退出检测状态,上行端口和下行端口都会进行初始化,然后再进入检测状态,然后开始免链路的训练。如果下游设备也是交换机或桥接器,它也会将Hot Reset消息转发给其下游端口。

2.6. 热复位方法

2.6.1. 次级总线复位

上级桥接设备的Secondary Bus Reset位于配置空间的Bridge Control寄存器中,可以通过软件修改达到热复位。软件对Secondary Bus Reset寄存器先写入0再写入1,即发出TS1消息,连续2次。

2.6.2. 链路禁用

通过在下游设备的链路控制寄存器中设置Link Disable位,软件可以禁用链路。当禁用链路时,下游组件会收到禁用信号并执行相应的操作,这也会导致它们进行热复位。禁用链路的操作将触发下游端口进入Recovery LTSSM状态,并开始发送具有Disable位设置的TS1消息。需要注意的是,只有在禁用链路后,才能对下游端口进行控制。因此,Link Disable位被保留给上行端口,例如终端设备或交换机上行端口。

Link Control Register寄存器位于PCI Express Capability的Offset PXCAP + 10h: PXLC – PCI Express Link Control。

当上行端口识别到带有Disabled位设置的传入TS1消息时,物理层会向链路层发送LinkUp=0(false)信号,并使所有通道进入电气空闲状态。在经过2毫秒的超时后,上行端口将进入Detect状态,但下行端口将保持在Disabled LTSSM状态,直到被指示退出该状态(例如通过清除Link Disable位),因此链路将保持禁用状态,并且在未被解除禁用之前不会尝试进行训练。

功能层级复位

3.1. FLR

FLR(Function-Level Reset)功能允许软件仅重置多功能设备中的某一个功能,而无需对所有功能进行复位。为了确定是否支持FLR功能,软件可以检查设备能力寄存器中的Function-Level Reset Capability位。如果此位被设置,软件可以通过设置设备控制寄存器中的Initiate Function-Level Reset位来启动FLR操作。FLR的实现虽然推荐,但并非每个设备都支持该功能,因此在尝试使用FLR之前,软件应先确认设备是否支持该功能。

是否支持FLR,通过查看位于PCI Express Capability的Offset PXCAP + 4h: PXDCAP – PCI Express Device Capabilities。

设置FLR,通过设置于通过查看位于PCI Express Capability的Offset PXCAP + 8h: PXDC – PCI Express Device Control。

FLR重置功能的内部状态和寄存器,使其处于静止状态,但不会影响任何sticky位、硬件初始化的位或链路特定的寄存器(如Captured Power、ASPM Control、Max_Payload_Size或Virtual Channel寄存器)。如果已发送了一个未解除的Assert INTx中断消息,则必须发送相应的Deassert INTx消息,除非该中断由内部的另一个功能共享并且仍然处于已断言状态。当接收到FLR时,该功能的所有外部活动都需要停止。

3.2. 时间要求

-

与可能访问该功能的其他软件协调,确保在FLR期间不尝试访问该功能。

-

清除整个命令寄存器,使该功能处于静止状态。

-

确保先前请求的完成已通过轮询设备状态寄存器中的Transactions Pending位进行返回,直到该位被清除或等待足够长的时间以确保这些完成永远不会被返回。多长时间足够长呢?如果使用了完成超时,可以在发送FLR之前等待超时时间。如果禁用了完成超时,则至少等待100毫秒。

-

启动FLR并等待100毫秒。

-

设置功能的配置寄存器,并使其能够进行正常操作。

当FLR完成后,无论何时完成,都必须清除Transactions Pending位。

3.3. 复位退出

在退出复位状态后,链路训练和初始化必须在20毫秒内开始。由于复位信号是异步的,设备可能在不同的时间退出复位状态,但必须在此时间内开始进行训练。

为了允许复位组件执行内部初始化,系统软件必须在复位结束后至少等待100毫秒才能尝试发送配置请求到它们。如果软件在100毫秒等待时间之后向设备发起配置请求,但设备仍未完成自我初始化,它会返回带有CRS状态的完成。由于配置请求只能由CPU发起,因此完成将返回给根复杂性。作为响应,根复杂性可以自动重新发出配置请求,或者使失败对软件可见。规范还指出,如果启用了CRS软件可见性,则软件应仅使用100毫秒的等待周期,否则可能会导致长时间超时或处理器停滞。

在复位后,设备被允许有1.0秒(-0% / +50%)的时间来做出对配置请求的正确响应。因此,在判断一个无响应的设备是否损坏之前,系统必须小心等待那么长的时间。这个值继承自PCI,这种长时间延迟的原因可能是一些设备将配置空间实现为本地存储器,必须在配置软件能够正确查看之前进行初始化。它的初始化可能涉及从慢速串行EEPROM复制所需的信息,因此可能需要一些时间。

开发实践

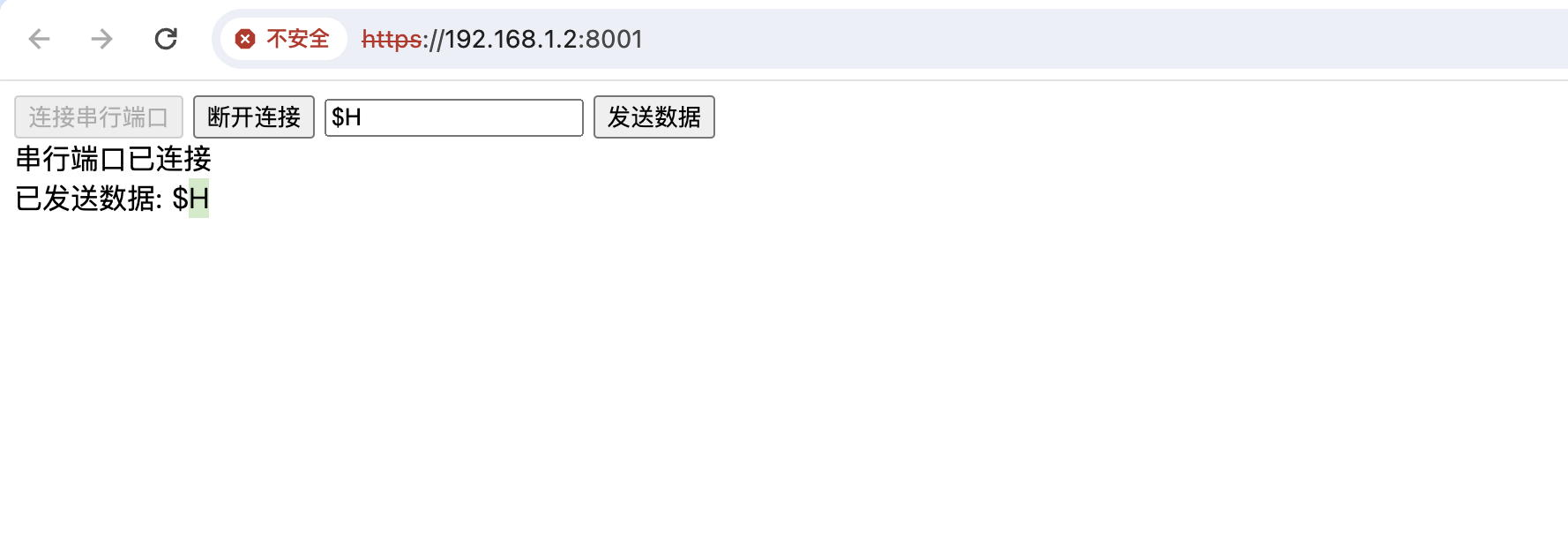

Linux下和Windows下的PCIe复位,均是通过操作Capacity Register来实现的。Windows下操作Capacity Register可以通过rw-everything或内核驱动WinIo来实现。以下具体方法使用Linux。

4.1. 传统复位

能够软件操作的只有Hot Reset。两种Hot Reset的方法都需要在上行设备上进行设置。

获取上行设备路径:

michael@ubuntu22:~$ readlink /sys/bus/pci/devices/0000:0f:00.0

../../../devices/pci0000:00/0000:00:02.2/0000:0f:00.0

# 上面的内容即是DBF设备的完整路径,0000:00:02.2即是它的上行设备DBF4.1.1. Secondary Bus Reset

# 获取Bridge Control寄存器

root@ubuntu22:~# setpci -s 00:02.2 3e.w

0012

root@ubuntu22:~# setpci -s 00:02.2 BRIDGE_CONTROL

0012

# 连续设置2个Reset, 0x52=0x12|0x40,即设置Secondary Bus Rset=1

root@ubuntu22:~# setpci -s 00:02.2 BRIDGE_CONTROL=0x52

root@ubuntu22:~# setpci -s 00:02.2 BRIDGE_CONTROL=0x52

# 还原

root@ubuntu22:~# setpci -s 00:02.2 BRIDGE_CONTROL=0x52

# 通知系统移除设备 /

root@ubuntu22:/home/michael# echo 1 > /sys/bus/pci/devices/0000:0f:00.0/remove

# Rescan

echo 1 > /sys/bus/pci/rescan4.1.2. Link Disable Rset

# 获取Link Control Register

root@ubuntu22:~# setpci -s 00:02.2 CAP_EXP+10.b

40

# 连续设置2个Reset, 0x50=0x40|0x10,即设置Link Disable=1

root@ubuntu22:~# setpci -s 00:02.2 CAP_EXP+10.b=0x50

# 还原

sleep 1

root@ubuntu22:~# setpci -s 00:02.2 CAP_EXP+10.b=0x40

# 通知系统移除设备 /

root@ubuntu22:/home/michael# echo 1 > /sys/bus/pci/devices/0000:0f:00.0/remove

# Rescan

echo 1 > /sys/bus/pci/rescan4.2. FLR

# 获取PXDCAP寄存器查看是否支持FLR

root@ubuntu22:/home/michael# setpci -s 0f:00.0 CAP_EXP+4.L

112c8da1

# 28Bit为1,支持FLR

# 连续设置2个Reset, 0x50=0x40|0x10,即设置Link Disable=1

root@ubuntu22:~# setpci -s 00:02.2 CAP_EXP+10.b=0x50

# 还原

sleep 1

root@ubuntu22:~# setpci -s 00:02.2 CAP_EXP+10.b=0x40

# 通知系统移除设备 /

root@ubuntu22:/home/michael# echo 1 > /sys/bus/pci/devices/0000:0f:00.0/remove

# Rescan

echo 1 > /sys/bus/pci/rescan