【安全硬件】Chap.6 芯片生产猜疑链与SoC设计流程;可能会存在的安全威胁Untrusted IC Supply Chain Threats

- 背景

- 1. IC和半导体产业的全球化

- 2. 芯片生产猜疑链——Untrusted IC Supply Chain Threats

- 可能会存在的安全威胁

- 3. SoC Design Flow

- 主要参考来源

背景

在现代 超大规模集成电路设计(VLSI) 行业中,设计和制造是分开进行的,设计者通常对负责生产的代工厂几乎没有控制权,自然而然地会认为代工厂根本不可信。集成电路 (IC) 生产供应链的跨国、分布式和多步骤性质引入了基于芯片硬件的漏洞。

1. IC和半导体产业的全球化

IC和半导体产业的全球化。由于芯片设计公司的竞争对手会千方百计地提高产品上市时间和产品功能和性能。许多芯片公司的解决方案是增加团队规模——将更多资源投入到项目中,增加工程师来掩盖设计复杂性和上市时间压力的问题。

一旦做出该决定,公司为了节约开发成本会选择增加更低成本的工程师,从公司的管理层做出的决定可以看出需要在非发达国家寻求拥有良好技术基础的专业工程师比如中国和印度。并不是说这些国家的工程师比北美或欧洲的工程师更有效率,而是因为他们的价格要低得多——便宜四到八倍。

所以,由于IC设计的复杂性超过了团队的设计生产力时,IC产业会逐渐成为全球性的企业跨境合作。

Among the forces reshaping the semiconductor industry, few are more important than R&D productivity’s inability to keep pace with the challenges of product development. However, there are steps companies can take to close the gap: Cooperation between companies in various regions, IC production has became a global enterprise.

IC 开发生产力下降意味着工程岗位流失

What happens when chip-design Complexity outpaces design productivity

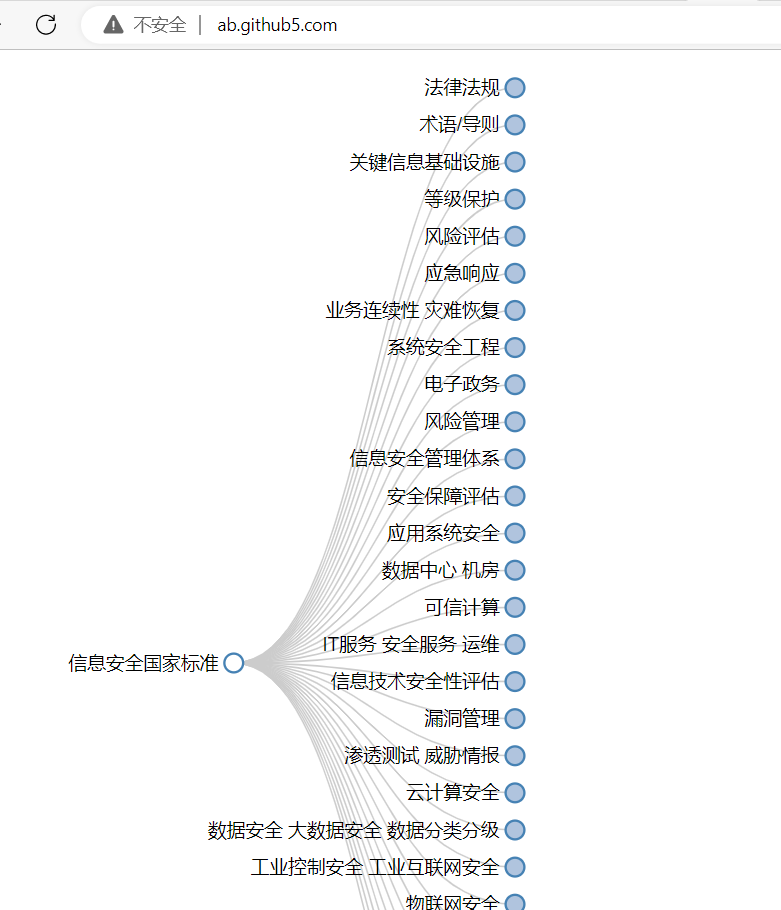

2. 芯片生产猜疑链——Untrusted IC Supply Chain Threats

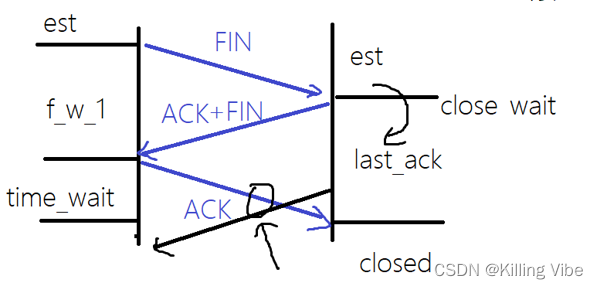

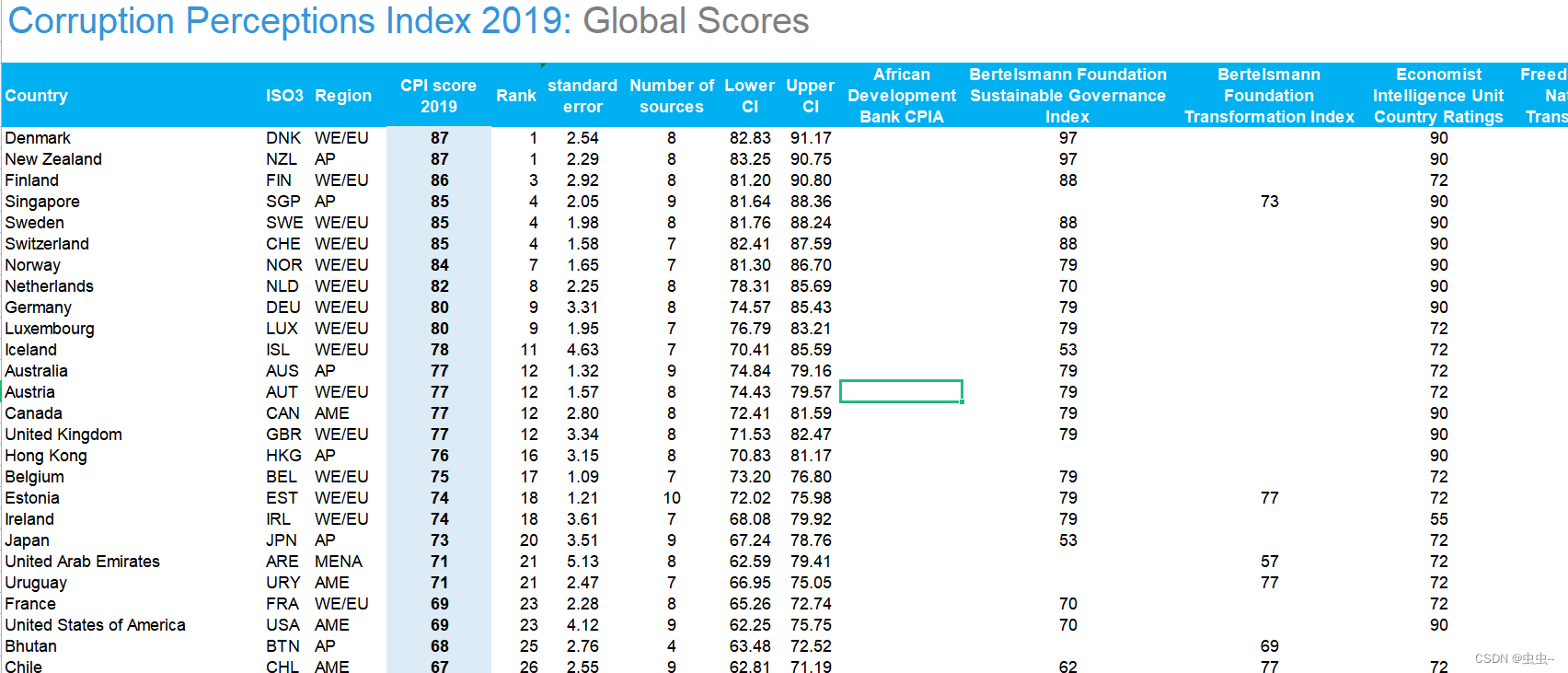

IC设计和半导体产业全球供应链概述:设计 IC 涉及从第三方设计公司采购知识产权 (IP) 设计,在内部设计一些组件,将两者结合起来,然后生成 IC 布局。然后将设计蓝图(例如,根据 GDS-II 布局格式)发送到代工厂,代工厂开发昂贵的掩模并制造 IC。然后,IC 会在制造现场进行测试,通常还会在第三方测试机构进行测试。最后,无故障的 IC 被封装和销售。

-

如今,设计 IC 的第一阶段涉及将知识产权 (IP) 设计外包给第三方设计公司(例如英国的 ARM 或 Imagination Technologies)。由于第三方的IP通常有很多保护的方式使得使用的设计师和购买的消费者无法验证IP的内容,因此理解为Semi-trusted。

-

第二阶段是设计额外的组件和系统集成,这通常在内部完成,在此步骤结束时会生成 IC 布局。由于是自己人设计完成的,因此理解为Trusted。

-

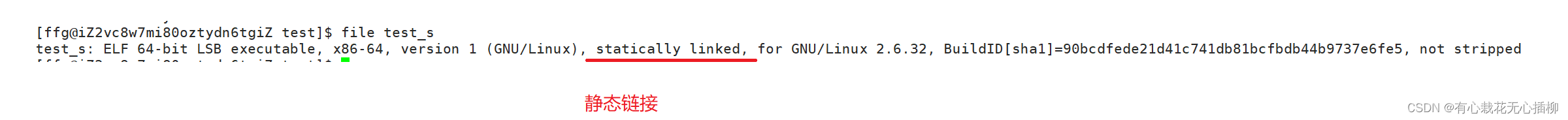

在第三阶段,设计蓝图(例如,GDS-II 布局格式)被发送到开发昂贵掩模并制造 IC 的代工厂,然后在制造现场进行测试,通常还会在第三方测试中进行测试设施。值得注意的是,目前大多数制造设施都位于东亚的中国大陆和台湾等地。设计者通常对负责生产的代工厂几乎没有控制权,自然而然地会认为代工厂根本不可信,因此理解为Untrusted。

-

测试阶段是自己人测试,因此理解为Trusted。

-

最后阶段是 IC 封装,也可以在另一个地理位置完成,很大可能是由另一个企业完成,因此理解为Untrusted。

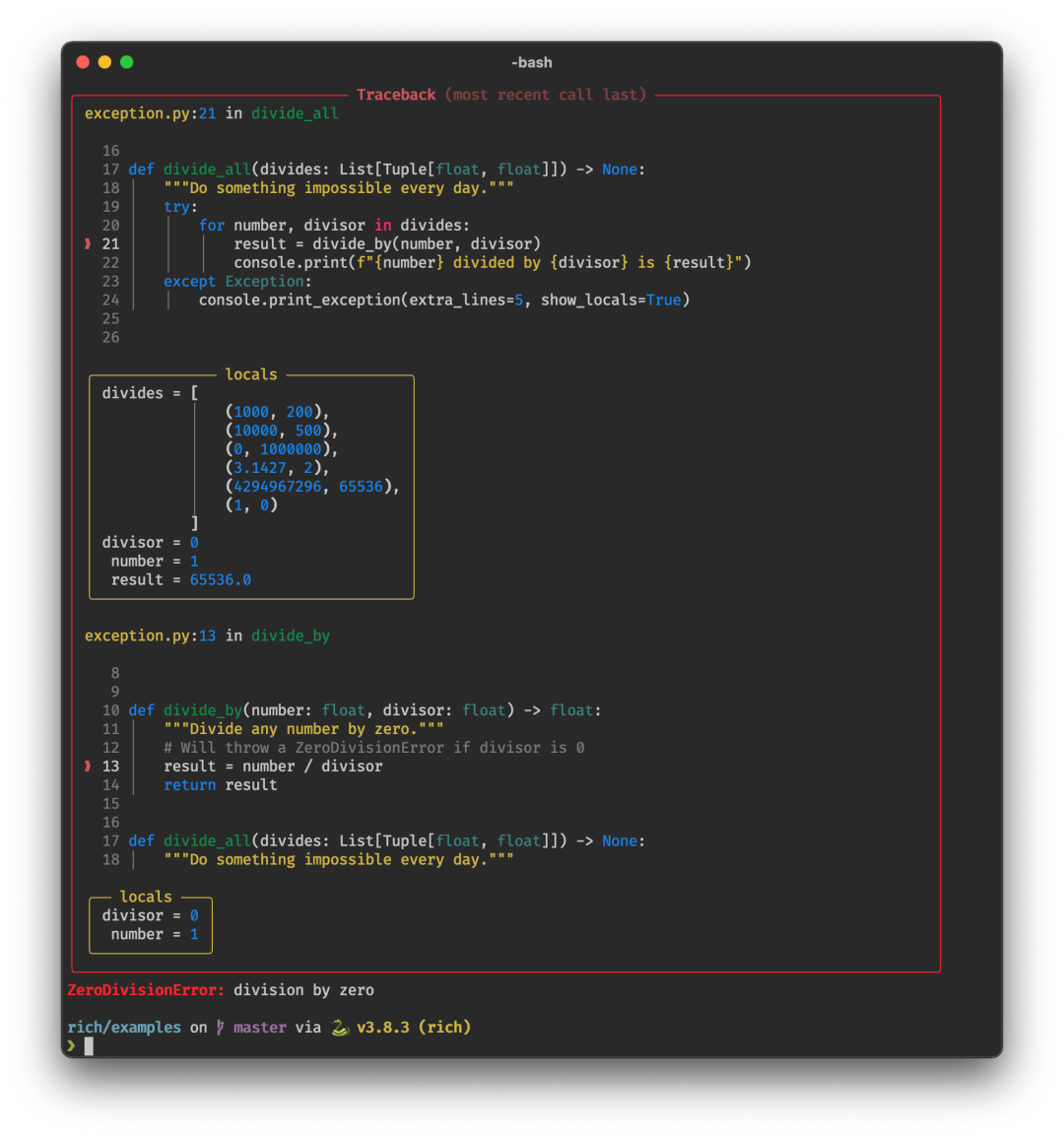

可能会存在的安全威胁

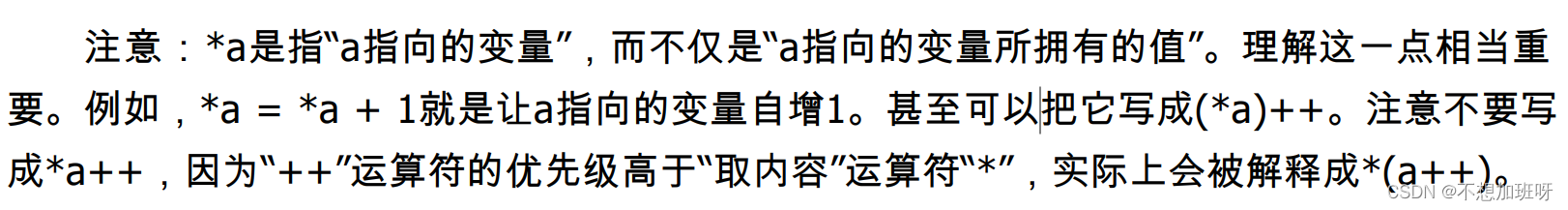

IC 供应链的这种分布式特性在很大程度上依赖于来自世界各地的重复使用专业知识,引入了许多硬件安全威胁,最突出的是木马程序插入的风险。基于这一假设,设计者研究了代工厂布局层可能发生的各种攻击,例如硬件木马插入、IP 和 IC 盗版和假冒,并已经做出了许多努力来降低这些风险。如上图所示,其中芯片生产猜疑链各部分中可能会存在的安全威胁有:

-

硬件木马。Hardware Trojans: An attacker either in the design house or in the foundry may add malicious circuits or modify existing circuits.

-

IP 盗版和 IC 过量生产。IP piracy and IC overbuilding: An IP user or a rogue foundry may illegally pirate the IP without the knowledge and consent of the designer. A malicious foundry may build more than the required number of ICs and sell the excess ICs in the gray market.

-

逆向工程 。Reverse engineering (RE): An attacker can reverse engineer the IC/IP design to his/her desired abstraction level. He can then reuse the recovered IP or improve it.

-

侧信道估计。Side-channel analysis: An attacker can extract the secret information by exploiting a physical modality (power consumption, timing, or electromangnetic emission) of the hardware that executes the target application.

-

伪造。Counterfeiting: An attacker illegally forges or imitates the original component/design.

A Primer on Hardware Security: Models, Methods, and Metrics

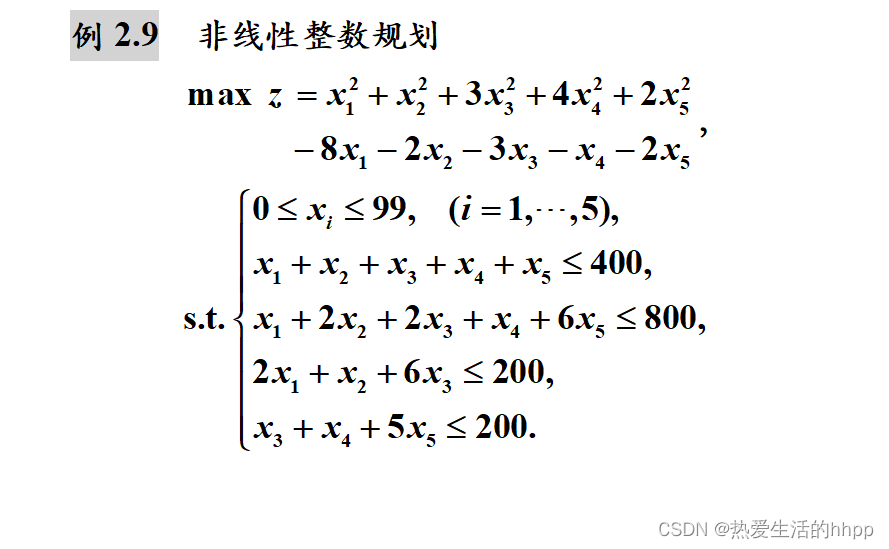

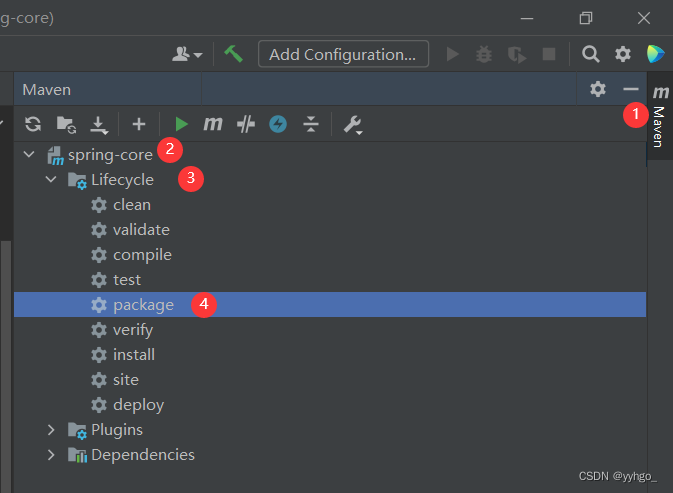

3. SoC Design Flow

- SoC 设计细节——SoC Design specifics:

需要将功能需求转化为如system C语言的模型,完成基本的功能测试,并以此为标准,通过其他算法探索其他方案。

SoC Design specifics:

- user’s requirements

- functionality

- modes of operation

- work plan:设计过程、任务、时间表和里程碑

- performance

- power

- size

- 软硬件分工——Architecture Design; HW/SW partitioning

决定硬件软件分别实现那些功能,定义软硬件之间的接口(interface)和协议(protocols),购买软硬件IP实现系统功能。 - 原型验证——Prototype on platform,如FPGA或ASIC平台

以基于FPGA平台的原型验证为例,具体实施一般分为三个阶段:

- 功能设计阶段:硬件的行为模型与软件的工作原型一起创建。

- 电路设计阶段:功能块的行为描述被转移到电路中。对于数字块,此过程是自动化的,并且基于合成算法。对于模拟块,这必须手动完成;正在进行模拟设计过程自动化的研究。

- 物理设计阶段:主要设计任务包括:平面规划,焊盘环设计,放置,时钟树设计,功率和IR压降分析(动态和静态),布线和设计规则检查。

-

软硬件联合验证——HW/SW co-verification:

-

代工厂批量生产和发货——Volume manufacture and ship

-

PCB制造和设备组装—— PCB manufacture and device assembly

IC生产供应链已成为跨国分布式业务,涉及世界各地的公司。

主要参考来源

Soton: Dr Basel Halak