LPDDR6相比LPDDR5在ZQ校准这一块删除了command-based相关的描述,删除了ZQ校准模式切换的描述,仅支持background-based的校准。

回顾一下LPDDR5 基于background-based的校准:

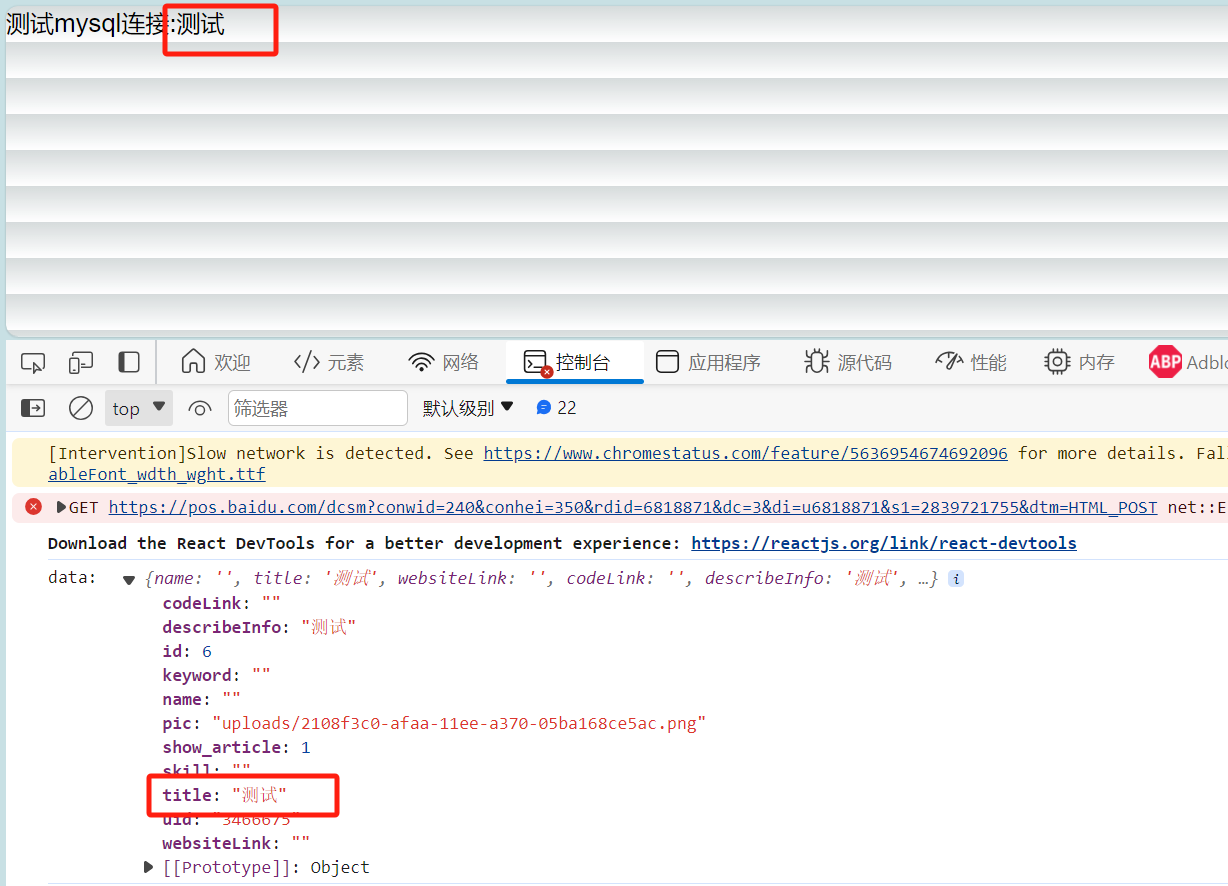

background ZQC是通过MR28 OP[5]来选择的,当选择为0(默认)即为background ZQC,当选择为background ZQC后还需要选择calibration interval,因为dram是自动做的ZQC,多久做一次需要人为设定,通过MR28 OP[3:2]可以选择ZQ interval(对于command-based ZQC,该设定不生效,因为基于命令的ZQC全是由用户通过命令发送的)。

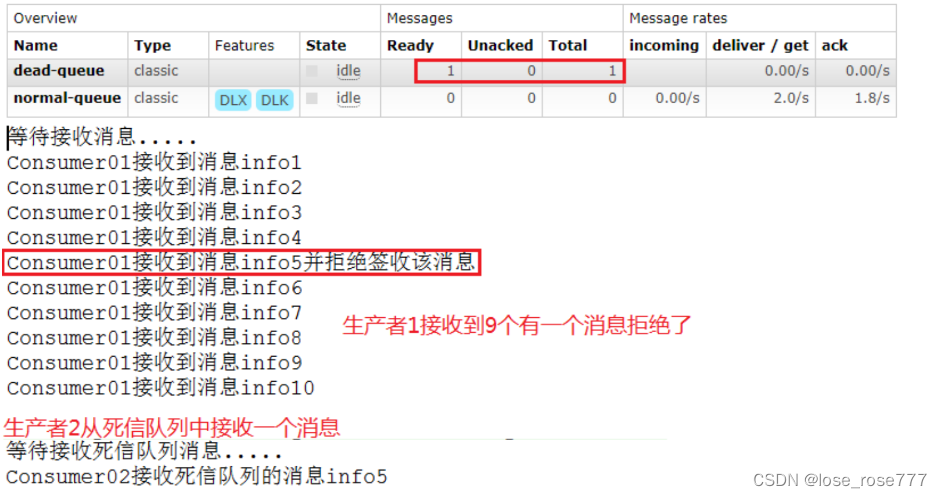

每个dram颗粒都需要一个ZQ精准电阻,有的时候dram厂商给到用户的是一个封装好的dram package,在package中可能可能只会有一个精准电阻,而被多个dram颗粒公用。在LPDDR5协议中 share ZQ是允许的,即在多个dram中已经进行了内部的仲裁,每个dram都有机会独占ZQ来进行各自的ZQC,仲裁策略是dram厂商保证的,用户不感知。

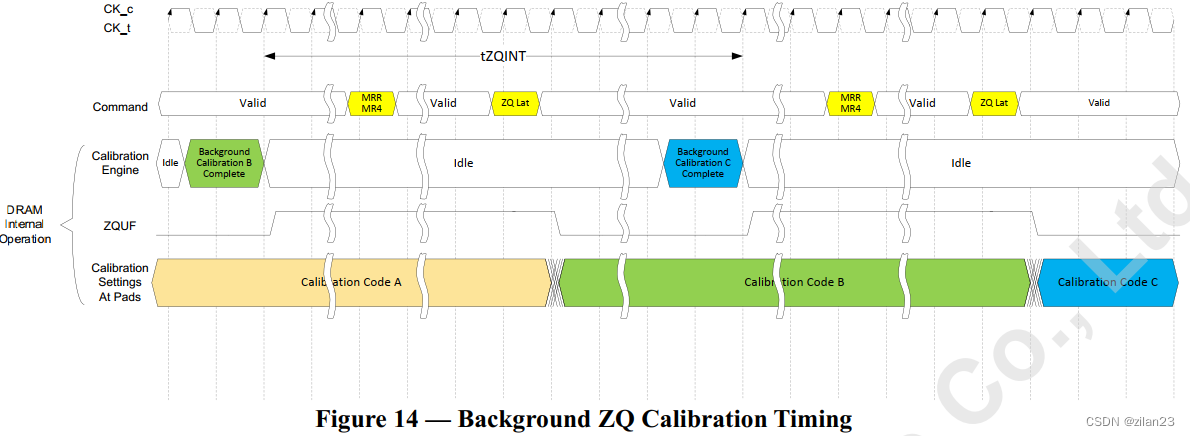

由于background ZQC是颗粒按照ZQ interval定期做的,因此什么时候该发送ZQL是可以推算出来的,即每间隔ZQ interval发送一次ZQL,即可latch到此次ZQC的值,更新到dram内部电阻上。但这样做有的时候对于controller不是特别友好,因为controller需要内部设置一个计数器来统计ZQ interval,并且有的时候此次的ZQC的值和上次是一样的(温度变化不大),其实没有必要再latch一次。为了解决这个问题,dram有一个mr,即MR4 OP[5] 位 (ZQUF),用来表示ZQC的值和上次不一样,需要ZQL来更新。只要定期读这个flag,每当该flag为1的时候再发送ZQL即可。每次ZQL会将flag清0。进行ZQL的时候需要保证没有DQ的动作。

当VDDQ进行DVFSQ或者下电的时候,ZQ必须stop,即通过MR28 OP[1]写1来实现,当VDDQ回到0.5V的时候,需要将MR28 OP[1]写0来重启ZQ,这个时候dram会自动做一次ZQC(只有background ZQC会做,如果是command-based ZQC 不会自动做),可以等待一段时间后发送ZQL,即可latch到此次ZQC的电阻值。

一个比较tricky的地方是,当MR28 OP[1]写0来重启ZQ后,dram会进行一次自动的ZQC。但对于share-ZQ的package来说,ZQC是需要dram按顺序串行进行的,协议对于zq stop解除的时间顺序是有要求的,即initiator die应该晚于所有non-initiator(target) die来重启ZQ,因为initiator是ZQC的发起方,如果有initiator已经发起了ZQC,但有的non-initiator还在ZQ stop,那该non-initiator就会skip此次ZQC。协议允许non-initiator稍稍晚于initiator一些,只有100 ns的margin。