目录

赋值语句:

(1).非阻塞(Non_Blocking)赋值方式( 如 b <= a; ):

(2).阻塞(Blocking)赋值方式( 如 b = a; ):

例:

块语句:

顺序块:

例:

并行块:

例:

编辑

块名:

起始时间和结束时间:

赋值语句:

在Verilog HDL语言中,信号有两种赋值方式:

(1).非阻塞(Non_Blocking)赋值方式( 如 b <= a; ):

1) 块结束后才完成赋值操作。

2) b的值并不是立刻就改变的。

3) 这是一种比较常用的赋值方法。(特别在编写可综合模块时)

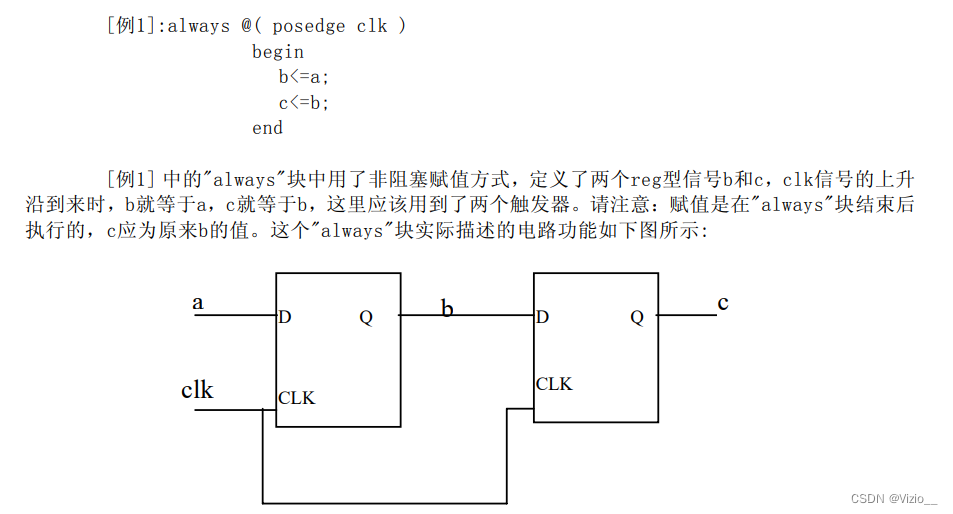

这种方式的赋值并不是马上执行的,也就是说"always"块内的下一条语句执行后,b并不等于a,而是 保持原来的值。"always"块结束后,才进行赋值。

(2).阻塞(Blocking)赋值方式( 如 b = a; ):

1) 赋值语句执行完后,块才结束。

2) b的值在赋值语句执行完后立刻就改变的。

3) 可能会产生意想不到的结果。

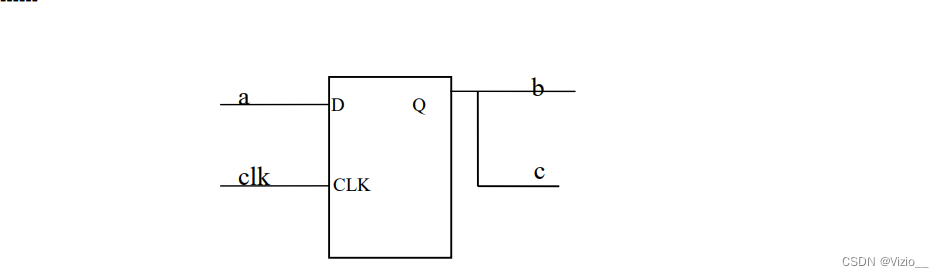

这种赋值方式是马上执行的。也就是说执行下一条语句时,b已等于a。尽管这种方式看起来很直观, 但是可能引起麻烦

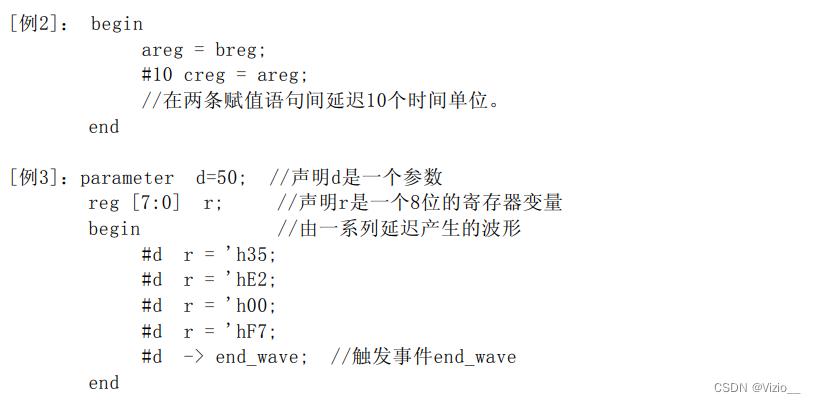

例:

块语句:

块语句通常用来将两条或多条语句组合在一起,使其在格式上看更象一条语句。块语句有两 种,一种是begin_end语句,通常用来标识顺序执行的语句,用它来标识的块称为顺序块。一种是 fork_join语句,通常用来标识并行执行的语句,用它来标识的块称为并行块。

顺序块:

顺序块有以下特点:

1) 块内的语句是按顺序执行的,即只有上面一条语句执行完后下面的语句才能执行。

2) 每条语句的延迟时间是相对于前一条语句的仿真时间而言的。

3) 直到最后一条语句执行完,程序流程控制才跳出该语句块。

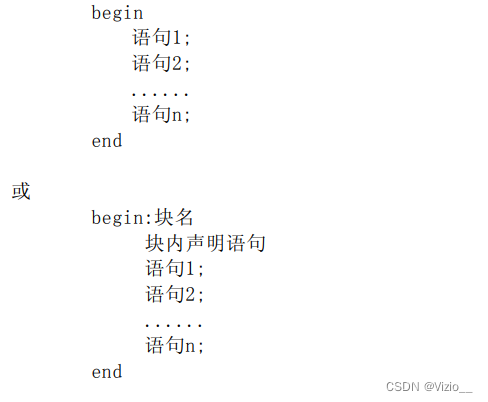

格式如下:

其中:

块名即该块的名字,一个标识名。

块内声明语句可以是参数声明语句、reg型变量声明语句、integer型变量声明语句、real 型变量声明语句。

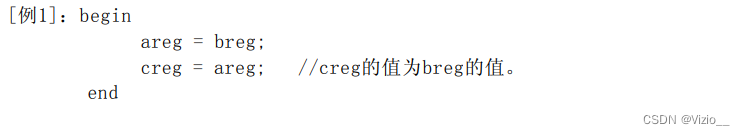

例:

并行块:

并行块有以下四个特点:

1) 块内语句是同时执行的,即程序流程控制一进入到该并行块,块内语句则开始同时并行 地执行。

2) 块内每条语句的延迟时间是相对于程序流程控制进入到块内时的仿真时间的。

3) 延迟时间是用来给赋值语句提供执行时序的。

4) 当按时间时序排序在最后的语句执行完后或一个disable语句执行时,程序流程控制跳 出该程序块。

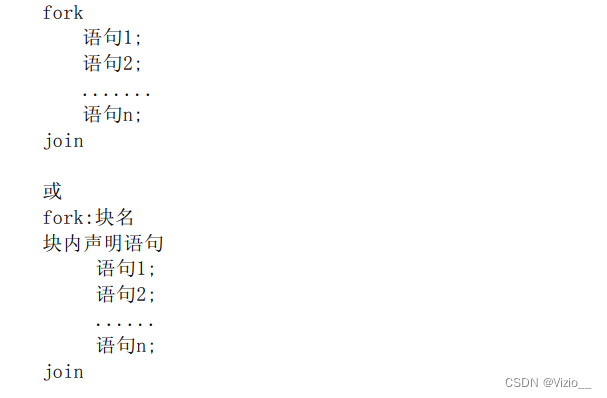

并行块的格式如下:

块名即标识该块的一个名字,相当于一个标识符

块内说明语句可以是参数说明语句、reg型变量声明语句、integer型变量声明语句、real 型变量声明语句、time型变量声明语句、事件(event)说明语句。

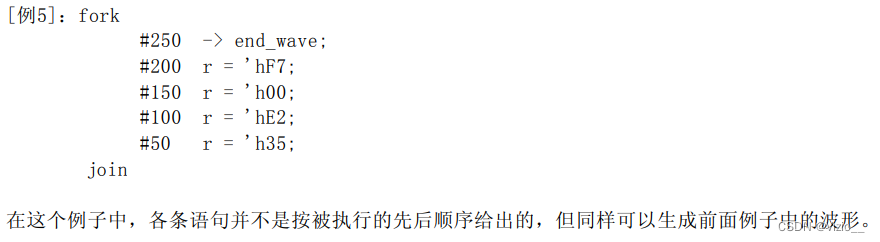

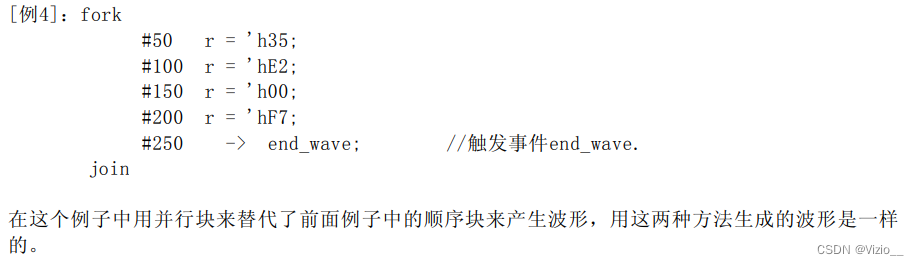

例:

块名:

在VerilgHDL语言中,可以给每个块取一个名字,只需将名字加在关键词begin或fork后面即 可。这样做的原因有以下几点。

1) 这样可以在块内定义局部变量,即只在块内使用的变量。

2) 这样可以允许块被其它语句调用,如被disable语句。

3) 在Verilog语言里,所有的变量都是静态的,即所有的变量都只有一个唯一的存储地址, 因此进入或跳出块并不影响存储在变量内的值。

起始时间和结束时间:

在并行块和顺序块中都有一个起始时间和结束时间的概念。对于顺序块,起始时间就是第一条语句开 始被执行的时间,结束时间就是最后一条语句执行完的时间。而对于并行块来说,起始时间对于块内 所有的语句是相同的,即程序流程控制进入该块的时间,其结束时间是按时间排序在最后的语句执行完的时间。

当一个块嵌入另一个块时,块的起始时间和结束时间是很重要的。至于跟在块后面的语句只有在该块 的结束时间到了才能开始执行,也就是说,只有该块完全执行完后,后面的语句才可以执行。

在fork_join块内,各条语句不必按顺序给出,因此在并行块里,各条语句在前还是在后是无关紧要 的。见下例: