文章目录

- 移位运算与乘法

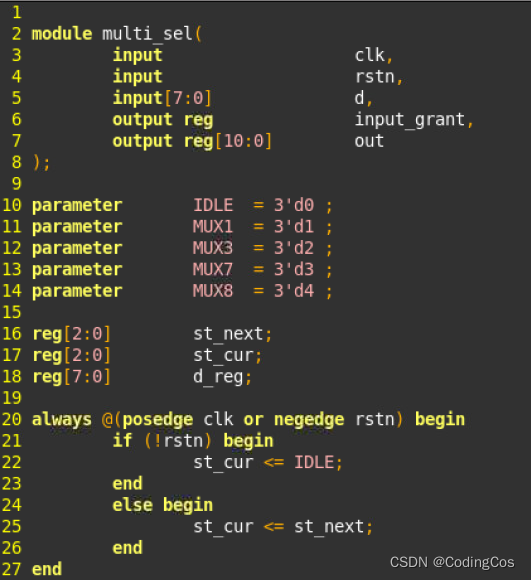

- parameter

- parameter 特点

- parameter 基本语法

- parameter 示例

- 局部参数

- 局部参数示例

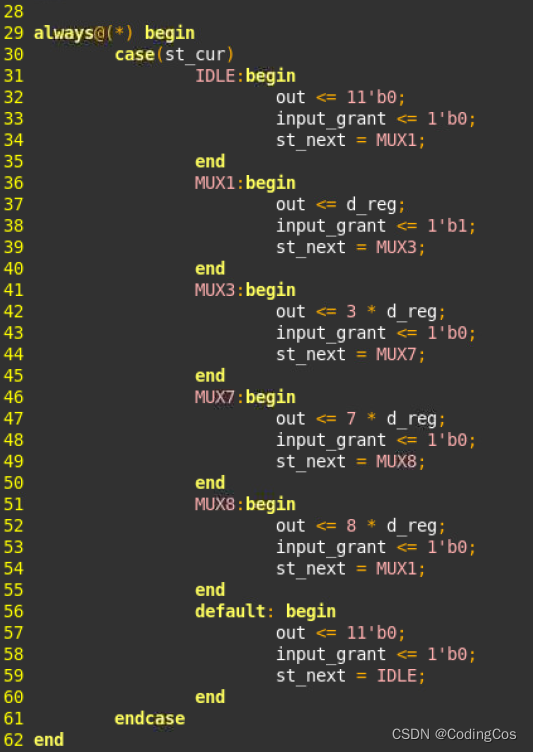

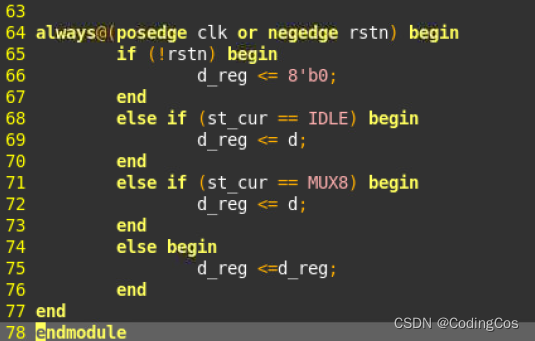

- 状态机代码实现

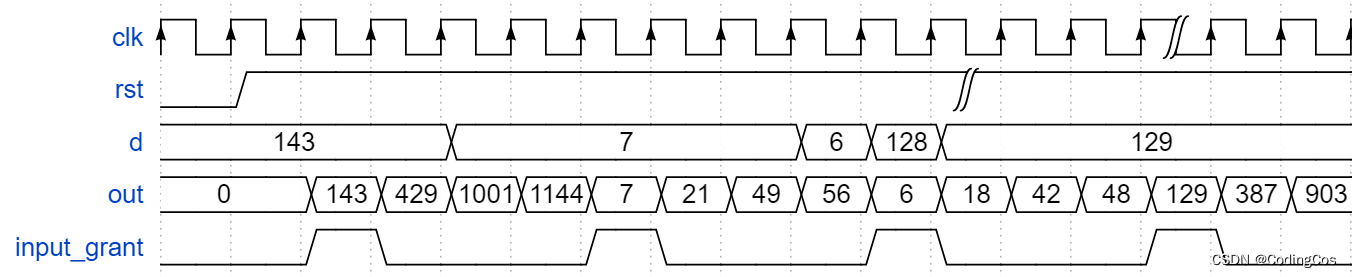

- VCS 仿真结果

文章 【芯片设计- RTL 数字逻辑设计入门 11.1 – 状态机实现 移位运算与乘法 1】 介绍了状态机,本篇文章主要就是使用状态机的方式来实现移位运算与乘法。

移位运算与乘法

已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效)

parameter

这里先介绍下 SystemVerilog中的关键字parameter。在SystemVerilog中,parameter关键字用于定义模块、类或函数内的常量。这些常量在编译时确定,可以在模块实例化时进行重写,从而提供了设计的可配置性和灵活性。parameter可以定义标量、数组或结构等类型的常量。

parameter 特点

- 静态定义:

parameter在编译时设置,不能在运行时更改。 - 默认值:在声明时可以设置默认值。

- 可重载:在模块实例化时可以更改其值。

- 数据类型:可以有特定的数据类型,如整型、实型、字符串等。

parameter 基本语法

parameter type parameter_name = default_value;

或者省略类型,让编译器自动推断:

parameter parameter_name = default_value;

parameter 示例

module adder #( parameter integer DATA_WIDTH = 8 // 定义参数DATA_WIDTH,默认值为8 ) (

input logic [DATA_WIDTH-1:0] a, b, // 使用参数设置输入端口宽度

output logic [DATA_WIDTH-1:0] sum // 使用参数设置输出端口宽度

);

// 实现一个DATA_WIDTH位的加法器

assign sum = a + b;

endmodule

// 在实例化时使用默认参数

adder adder_instance1 (

.a(a_signal),

.b(b_signal),

.sum(sum_signal)

);

// 在实例化时重载参数,将DATA_WIDTH设置为16

adder #(.DATA_WIDTH(16)) adder_instance2 (

.a(a_signal),

.b(b_signal),

.sum(sum_signal)

);

在这个例子中,adder模块定义了一个名为DATA_WIDTH的参数,其默认值为8。当你实例化adder模块时,你可以接受这个默认值,也可以提供一个新的值来重写它。这样,你就可以根据需要创建不同位宽的加法器实例。

局部参数

除了parameter,SystemVerilog还提供了localparam关键字,用于定义不可更改的局部常量。

localparam type localparam_name = constant_value;

localparam定义了一个局部常数,这个常数不能在模块实例化时被重写,用于内部模块展开或计算,而不打算作为模块的配置接口。

局部参数示例

在这个例子中,MAX_VALUE被定义为一个localparam,用于确定计数器的最大值,它内部使用,不可从外部更改。这样可以确保模块的行为在设计阶段被固定,并且在不同的实例化中保持一致。

状态机代码实现

VCS 仿真结果