以下综合

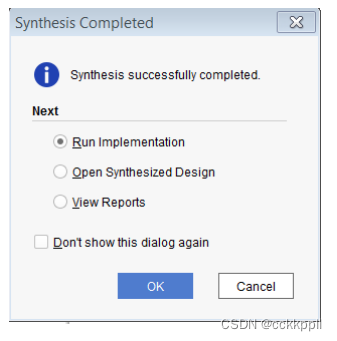

运行完成后,将打开Synthesis Completed对话框,如下所示图形

选择其中一个选项:

•运行实施:启动当前实施项目的实施设置。

•打开综合设计:打开综合网表、活动约束集和将目标设备集成到综合设计环境中,以便执行I/O引脚规划、设计分析和平面布置。

•查看报告:打开“报告”窗口,以便查看报告。

•不再显示此对话框:使用复选框可停止显示此对话框。

提示:通过选择“工具”>“设置”>“窗口行为”,可以恢复为显示对话框。分析综合结果合成完成后,您可以查看报告,并打开、分析和使用合成的设计“报告”窗口包含各种综合和Vivado IDE中的实现工具。

视频:有关更多信息,请参阅以下内容:Vivado Design Suite QuickTake视频:高级合成使用Vivado。打开“报告”视图,如下图所示,然后选择特定运行的报告。

使用综合设计环境

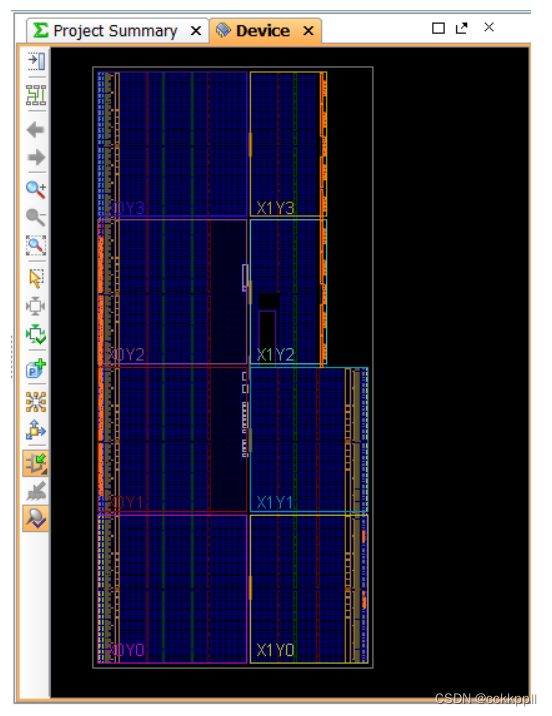

Vivado IDE提供了一个从几个不同角度分析设计的环境视角。当您打开一个合成设计时,软件会加载合成网表,活动约束集和目标设备。要打开合成设计,请从Flow Navigator或流量菜单。打开合成设计后,Vivado IDE将打开一个设备窗口,如中所示如下图所示。

从这个角度,您可以检查设计逻辑和层次结构,查看资源或者运行设计规则检查(DRC)。有关更多信息,请参阅Vivado设计套件用户指南:设计分析和闭合技术(UG906)探究逻辑Vivado IDE提供了几个逻辑探索视角:所有窗口交叉探测到提供最有用的信息:

•“网表”和“层次结构”窗口包含可导航的层次树样式视图。

•原理图窗口允许选择性逻辑扩展和分层显示。

•设备窗口提供设备、放置的逻辑对象的图形视图,以及连通性探索逻辑层次“网表”窗口显示综合设计的逻辑层次结构。您可以扩展和在网表中选择任何逻辑实例或网。

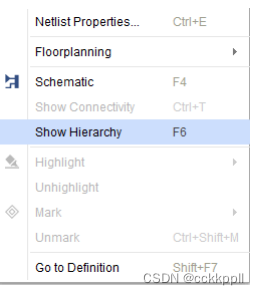

在其他窗口中选择逻辑对象时,“网表”窗口会自动展开为显示选定的逻辑对象,并且有关实例或网络的信息显示在实例或网络属性窗口。“综合设计”窗口显示RTL逻辑层次结构的图形表示。每个模块的大小与其他模块的大小成相对比例,因此您可以确定大小和任何选定模块的位置。要打开“层次”窗口,请在“网表”窗口中右键单击以显示上下文菜单。选择显示层次结构,如下图所示。也可以按F6键打开层次结构窗口。

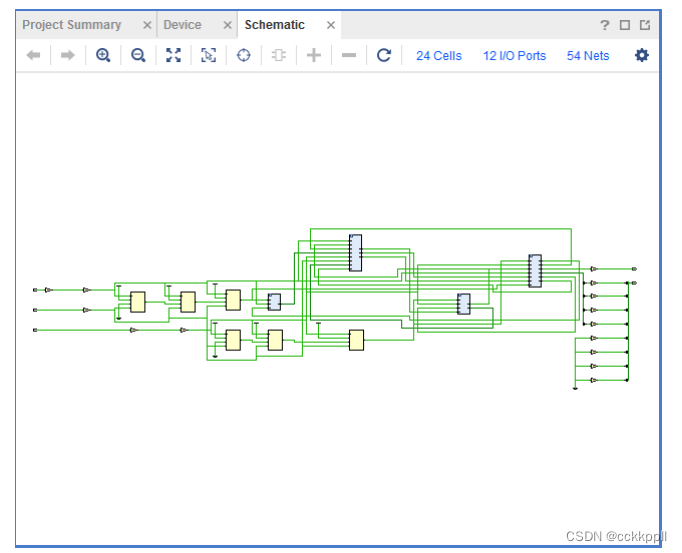

探索逻辑示意图

“原理图”窗口允许对逻辑设计进行选择性扩展和探索。你必须至少选择一个逻辑对象才能打开和显示“原理图”窗口。在“原理图”窗口中,查看并选择任何逻辑。您可以将计时路径组显示到显示路径上的所有实例。这有助于平面规划,因为它可以帮助您可视化其中时序关键模块在设计中。要打开“原理图”窗口,请选择一个或多个实例、网络或定时路径,然后选择从窗口工具栏或右键单击菜单中选择原理图,或按F4键。窗口打开,显示所选逻辑,如下图所示。

您可以选择并展开任何接点、实例或层次模块的逻辑。

运行时间分析

综合设计的时序分析有助于确保路径具有必要的有效实施的制约因素。Vivado合成是定时驱动的,可调整基于所提供的约束的输出。随着在设计中分配更多的物理约束,例如Pblocks和LOC约束,时序分析的结果变得更加准确,尽管这些结果仍然包含一些路径延迟的估计。综合设计使用路由延迟的估计来执行分析您可以在此级别运行时序分析,以确保覆盖正确的路径时序路径的更一般的想法。

重要!只有实施后的时间分析(地点和路线)才包括路由。综合设计的运行时序分析不如实现的设计。

![[开源]GPT Boss – 用图形化的方式部署您的私人GPT镜像网站](https://img-blog.csdnimg.cn/direct/b37ea7bc78a447fbb13f3fd305ac5509.png#pic_center)