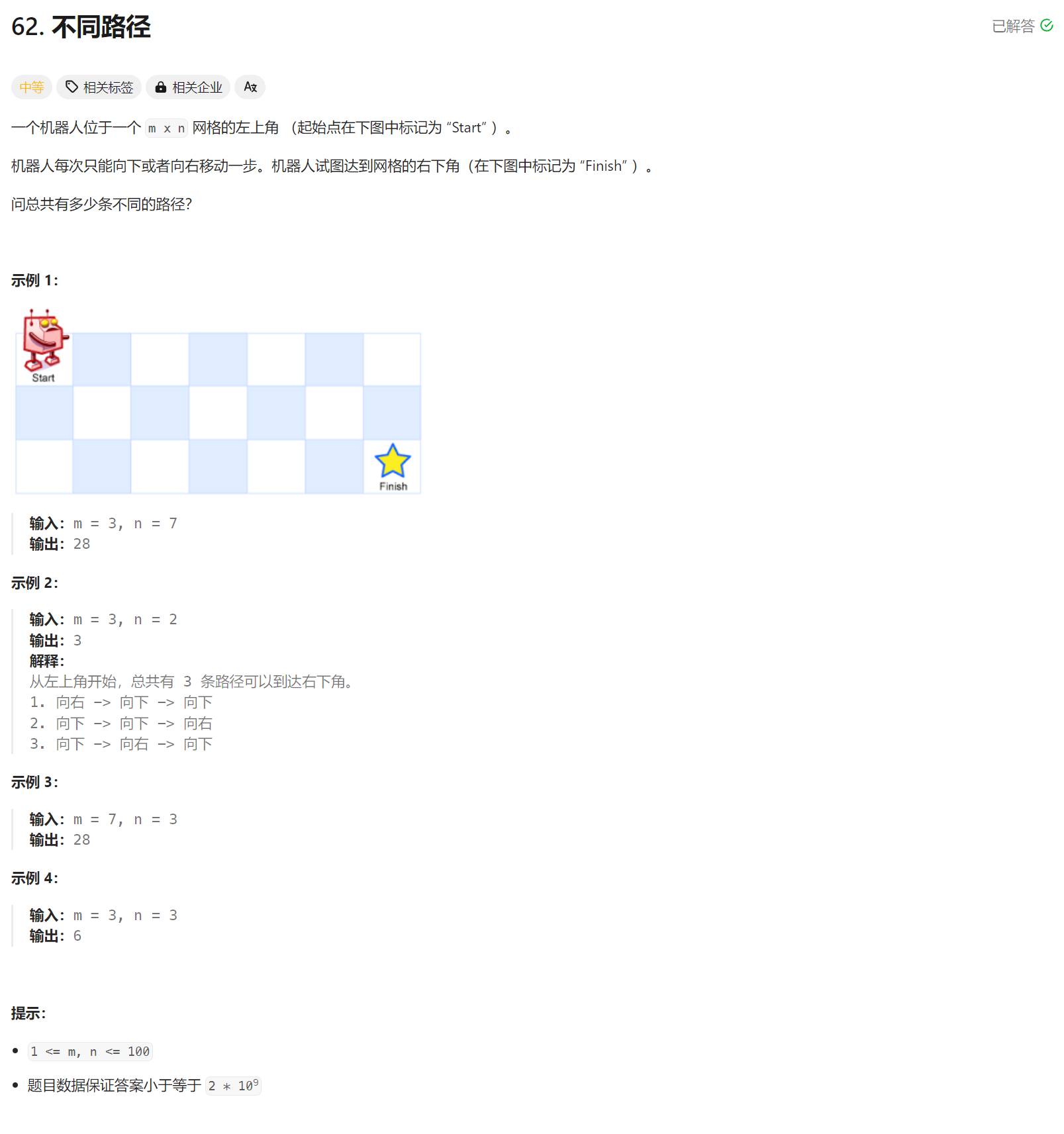

1. 前言

CRG(Clock and Reset Generation,时钟复位生成模块) 模块扮演着关键角色。这个模块负责为整个系统提供稳定可靠的时钟信号,同时在系统上电或出现故障时生成复位信号,确保各个模块按预期运行。简而言之,CRG模块就像是SoC系统的心脏,提供着整个系统需要的时钟和复位信号。

出于时钟复位结构规范设计和DFT可控的目的,一般会把相关电路放在一个集中的模块中管理,由专门的设计人员按需求进行设计与维护。对于时钟分频、MUX、切换、DFT测试结构埋入等等,均在模块内部实现。复位类似。

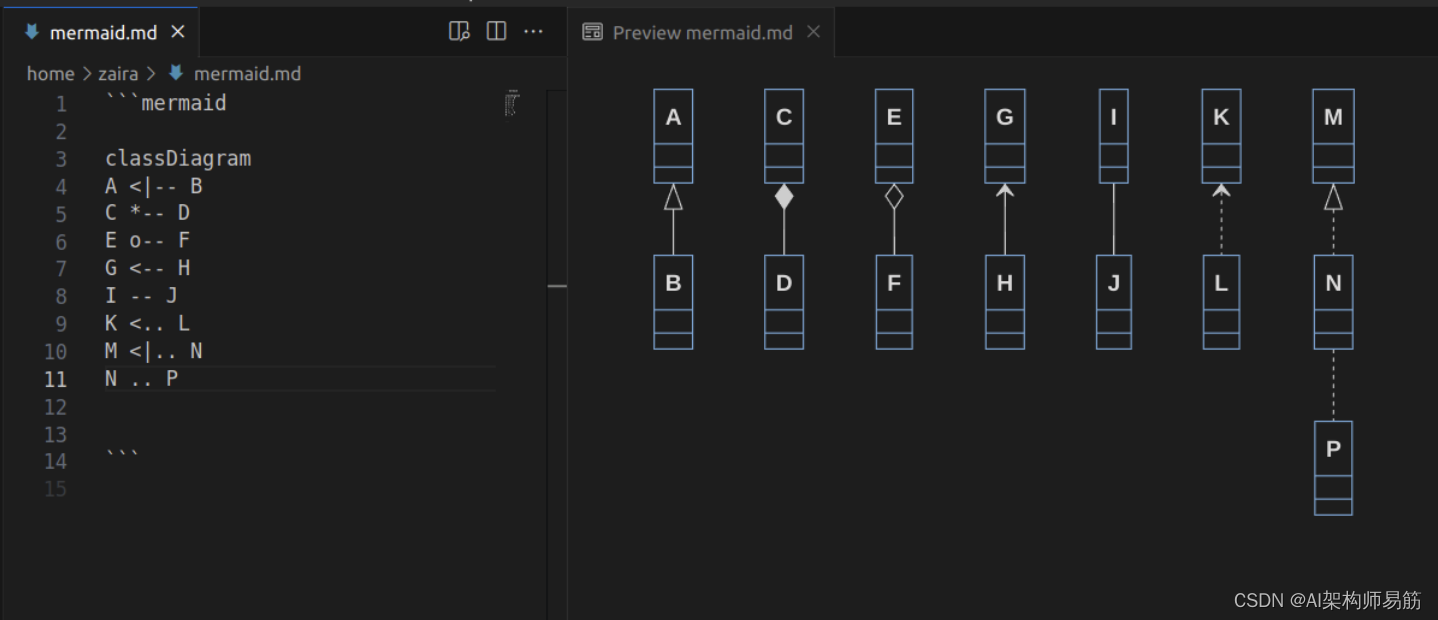

涉及到的主要技术:自动解复位,复位顺序,复位切频,时钟门控,亚稳态的恢复,异步复位同步释放,毛刺清除的技术细节。不用公司,不同芯片,因为场景不同,对于CRG的要求也不尽相同,但是具体的技术原理大同小异。CRG中主要包含这些东西:

2. 时钟基本概念

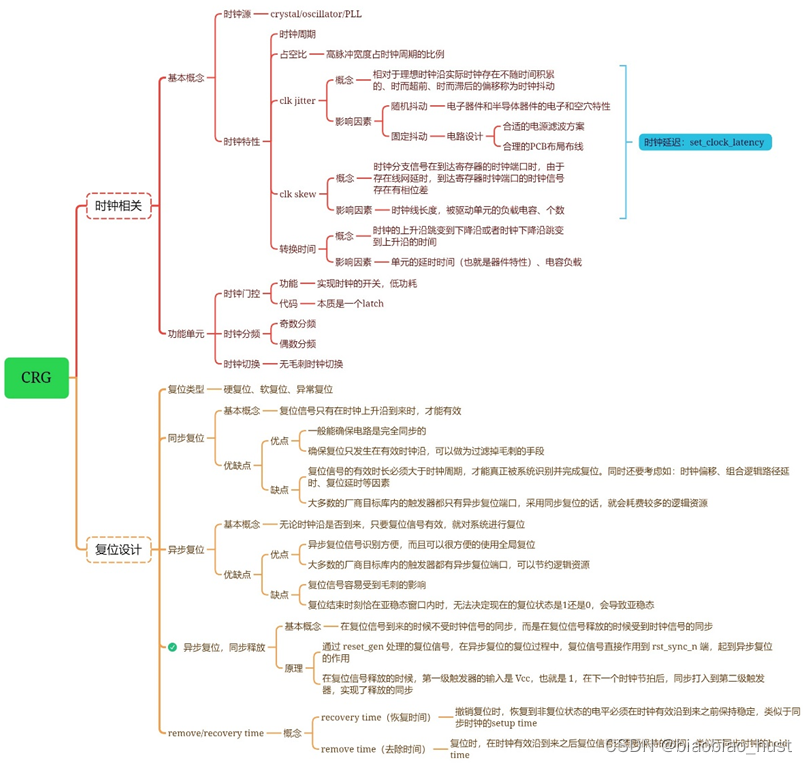

芯片的时钟源可以是外部晶振或是内部PLL,当然内部PLL也需要一个参考时钟,这个参考时钟一般是来自于片外的晶振。常见的外部时钟源有32.768KHz时钟和26MHz时钟(这个频率可变)。32.768KHz时钟用来提供给rtc模块或者timer模块等,用于产生系统时钟、时间戳或者进行计数等。26MHz时钟常用做PLL的参考时钟,或者其他需要慢速时钟的模块。

2.1 时钟源

用来产生时钟的器件,包括石英晶体,晶振等结构。

2.2 时钟结构

2.3 时钟属性

2.3.1 时钟周期

决定时钟频率

2.3.2 占空比

高脉冲占时钟周期的比例,常见为1/2

2.3.3 时钟抖动(clk jitter)

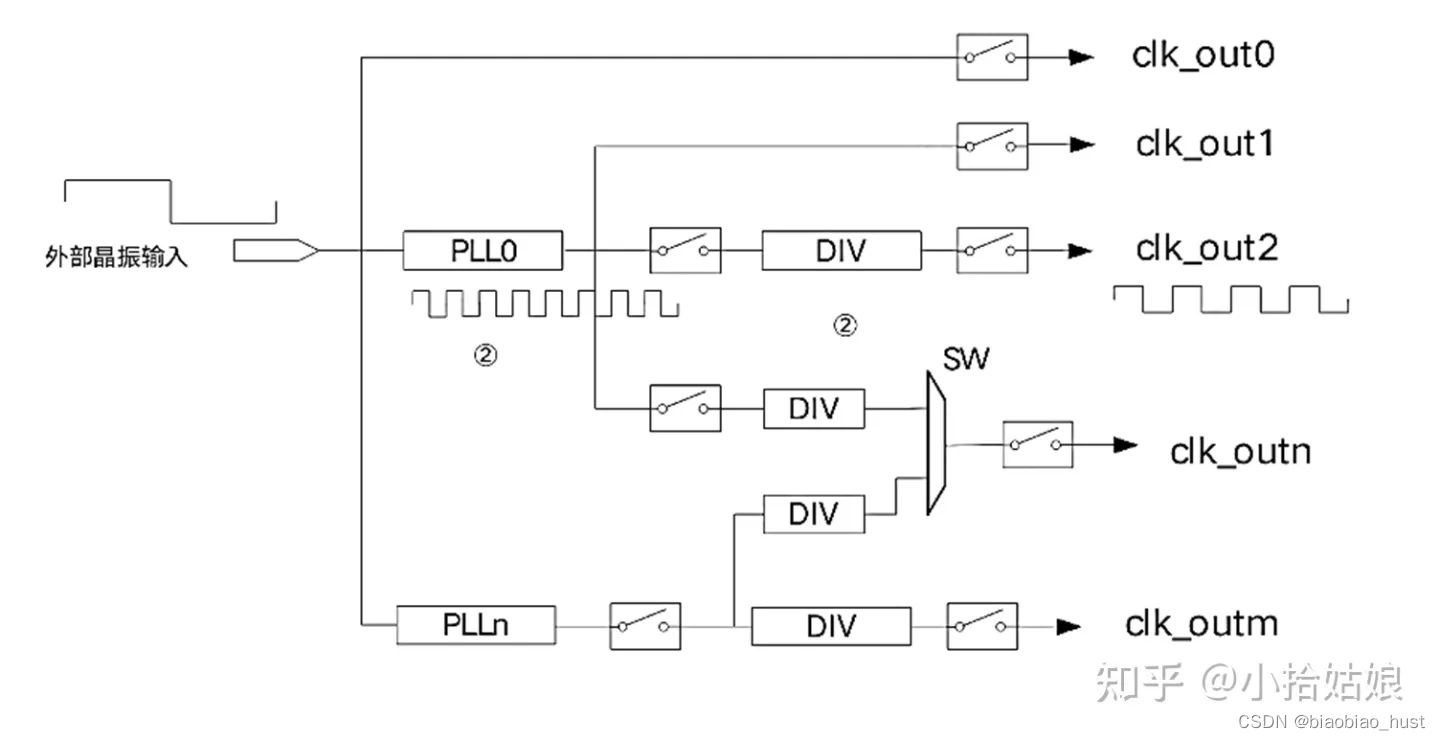

相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动,简称抖动,与时钟频率无关,如下图:

时钟的抖动可以分为随机抖动(Random Jitter,Rj)和固有抖动(Deterministic jitter):

- 随机抖动的来源为热噪声、Shot Noise 和Flick Noise,与电子器件和半导体器件的电子和空穴特性有关,比如ECL 工艺的PLL 比TTL 和CMOS工艺的PLL 有更小的随机抖动;

- 固定抖动的来源为:开关电源噪声、串扰、电磁干扰等等,与电路的设计有关,可以通过优化设计来改善,比如选择合适的电源滤波方案、合理的PCB 布局和布线。

2.3.4 时钟偏斜(clk skew)

时钟分支信号在到达寄存器的时钟端口过程中,都存在有线网等延时,由于延时,到达寄存器时钟端口的时钟信号存在有相位差,也就是不能保证每一个沿都对齐,这种差异称为时钟偏移(clock skew),也叫时钟偏斜。时钟的偏移如下图所示:

时钟skew 与时钟频率并没有直接关系,skew 与时钟线的长度及被时钟线驱动的时序单元的负载电容、个数有关。

时钟的偏移和时钟的抖动都影响着时钟网络分枝的延迟差异(相位差异),在Design Compiler 里面,我们用时钟的不确定性(uncertainty)来表示这两种情况的影响。使用set_clock_uncertainty 命令来设置。

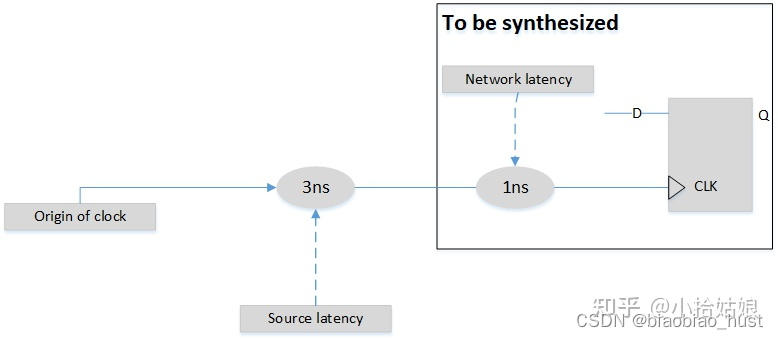

2.3.5 延时(latency)

时钟从时钟源(比如说晶振)出发到达触发器时钟端口的延时,称为时钟的延时,包含时钟源延迟(source latency)和时钟网络的延迟(networklatency),如下图所示:

时钟源延迟(clock source latency),也称为插入延迟(insertion delay),是时钟信号从其实际时钟原点到设计中时钟定义点(时钟的输入引脚)的传输时间,上图是3ns。

时钟网络的延迟( clock network latency)是时钟信号从其定义的点(端口或引脚)到寄存器时钟引脚的传输,经过缓冲器和连线产生的延迟(latency),上图是1ns。

2.3.6 转换时间

时钟的上升沿跳变到下降沿或者时钟下降沿跳变到上升沿的时间,这个时间并不是完全没有跳变时钟的,而是需要一定的转换时间。时钟的转换时间与与单元的延时时间(也就是器件特性)还有电容负载有关。

3. 功能单元

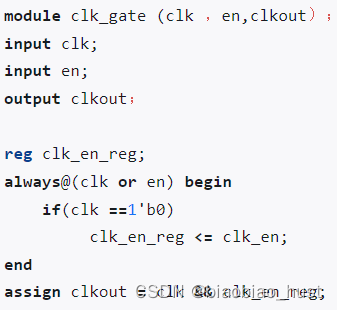

3.1 时钟门控

主要是为了降低芯片功耗,中后端在综合时可以自行插入。

3.2 时钟分频

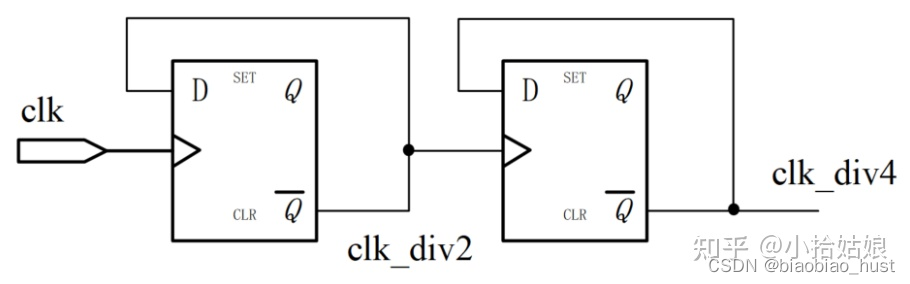

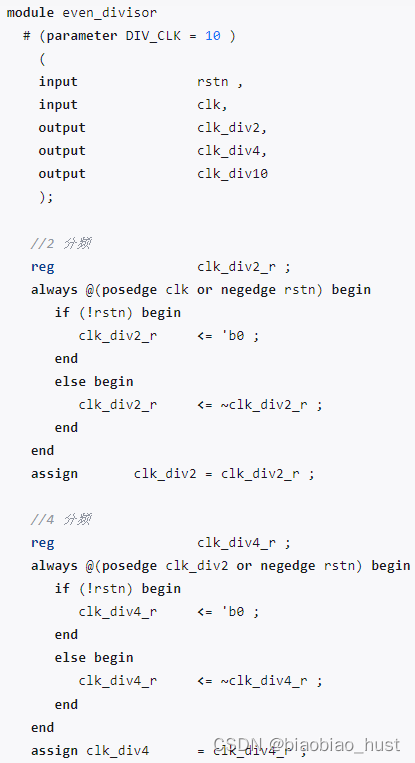

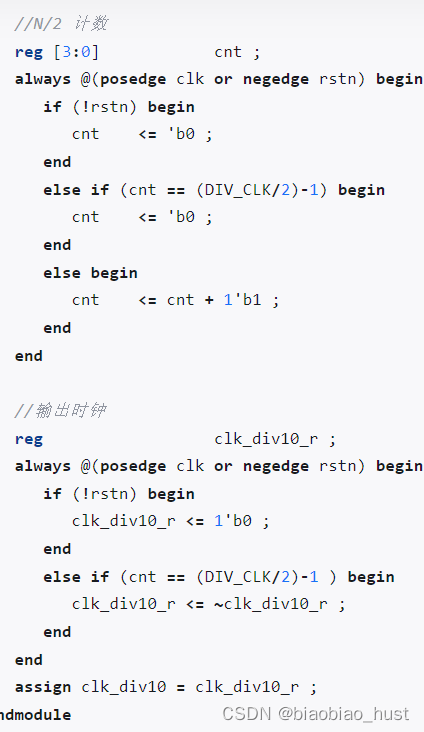

3.2.1 偶数分频——占空比为50%

采用触发器反向输出端连接到输入端的方式,可构成简单的 2 分频电路。以此为基础进行级联,可构成 4 分频,8 分频电路。电路实现如下图所示,用 Verilog 描述时只需使用简单的取反逻辑即可。

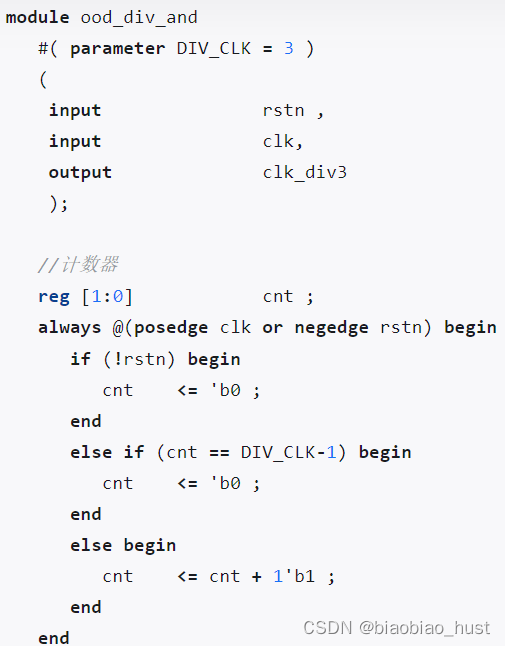

3.2.2 奇数分频

需要奇数分频如果不要求占空比为 50%,可按照偶数分频的方法进行分频。即计数器对分频系数 N 进行循环计算,然后根据计数值选择一定的占空比输出分频时钟。

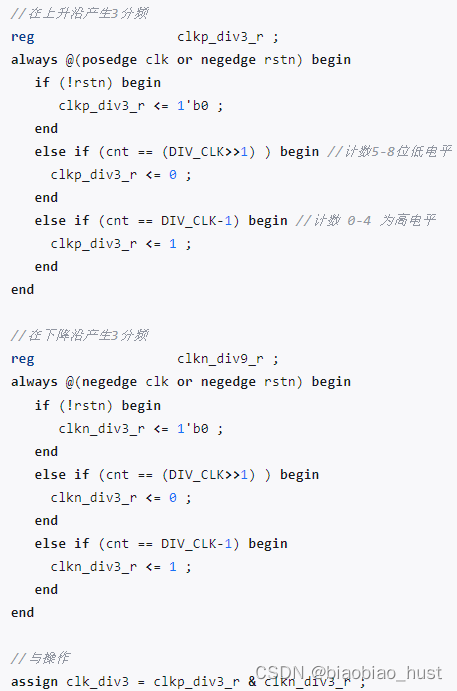

如果奇数分频输出时钟的高低电平只差一个 cycle ,则可以利用源时钟双边沿特性并采用"与操作"或"或操作"的方式将分频时钟占空比调整到 50%。采用"或操作"产生占空比为 50% 的 3 分频时钟。

利用源时钟上升沿分频出高电平为 1 个 cycle、低电平为 2 个 cycle 的 3 分频时钟。

利用源时钟下降沿分频出高电平为 1 个 cycle、低电平为 2 个 cycle 的 3 分拼时钟。

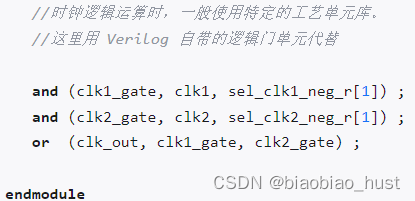

两个 3 分频时钟应该在计数器相同数值、不同边沿下产生,相位差为半个时钟周期。然后将 2 个时钟进行"或操作",便可以得到占空比为 50% 的 3 分频时钟。以3分频为例,对应的代码如下:

3.2.3 时钟切换

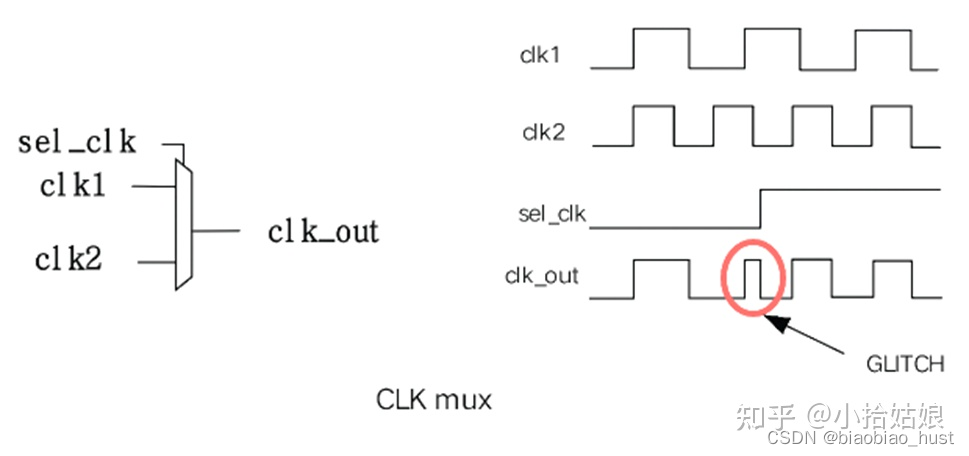

时钟mux:用于静态切换,动态切换会出现glitch。

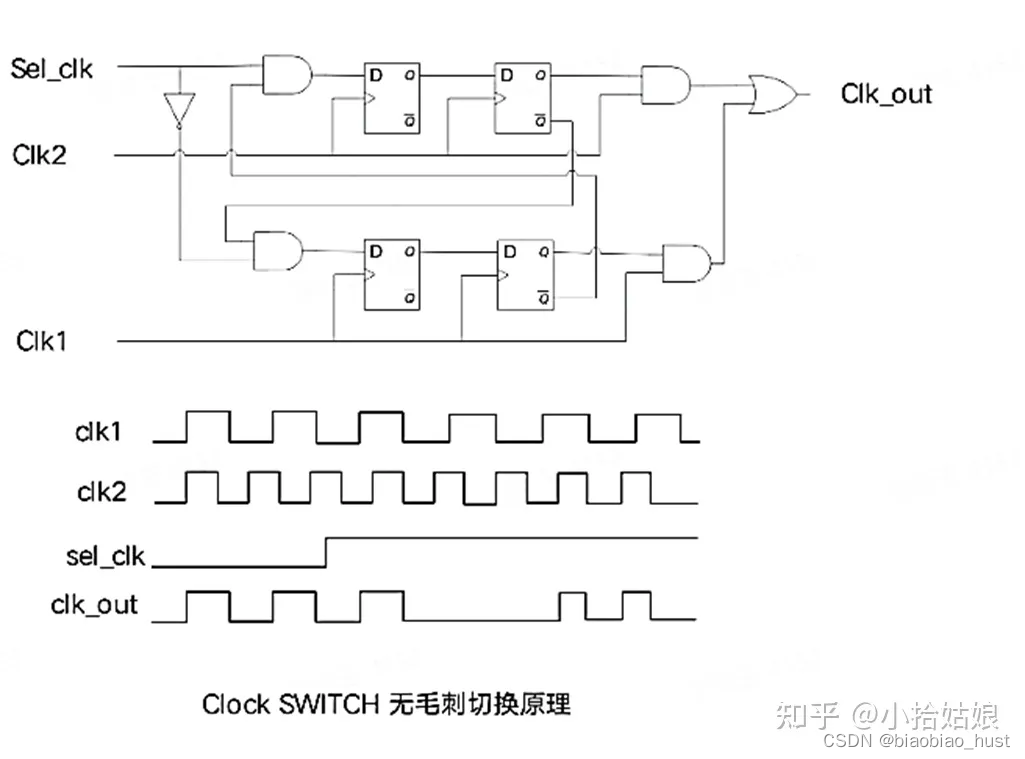

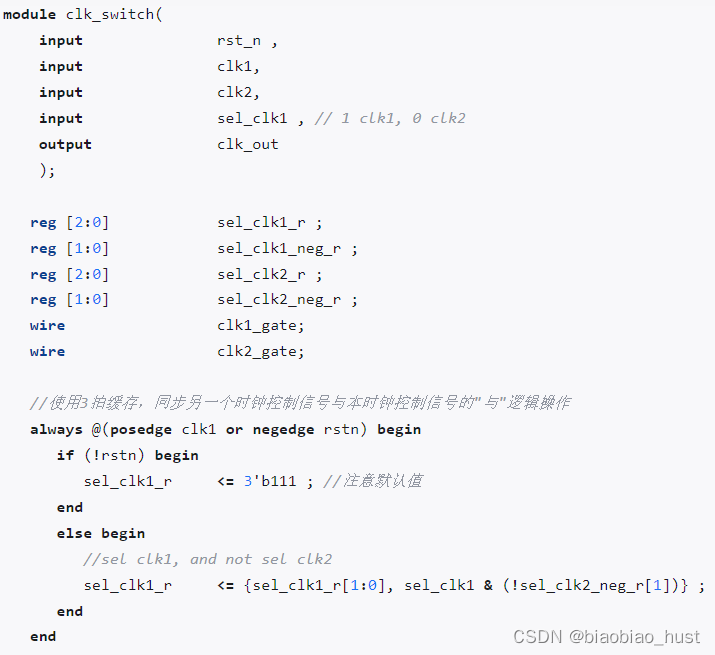

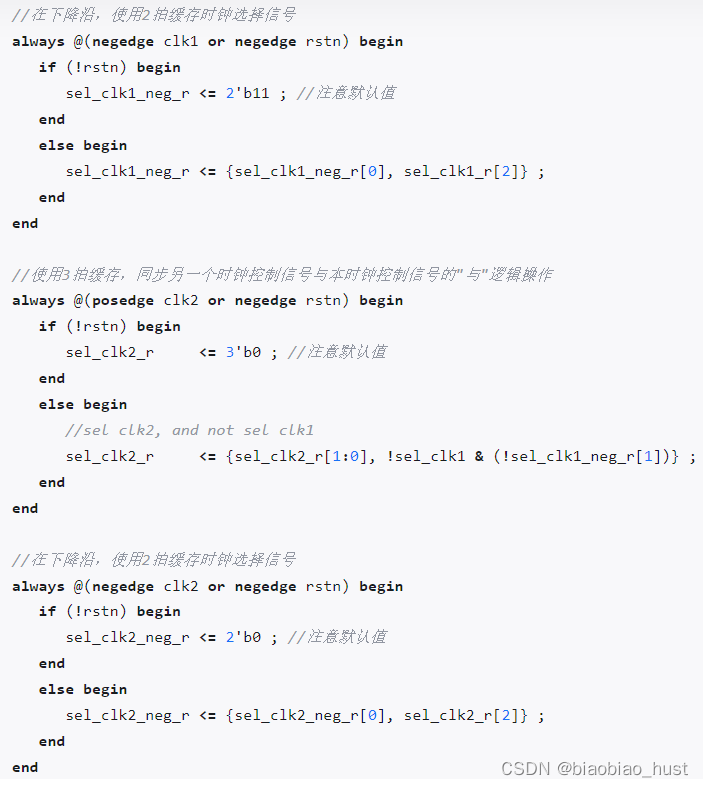

时钟switch:可用于动态切换,切换过程中会短时间内无时钟,在两个电平相反的时候切换时钟,肯定有毛刺;电平相同的时候,即使不产生毛刺,时钟切换后的第一个时钟的周期或占空比也不是理想的。所以,为避免毛刺的产生,需要在两个时钟都为低电平的时候进行时钟切换。一种典型的时钟切换电路如下所示。

该电路利用时钟下降沿对时钟选择信号 sel_clk 进行缓存。同时一个时钟选择信号对另一个时钟进行反馈控制,保证同一时刻只能有一路时钟有效。最后采用"或操作"将两路时钟合并,完成时钟切换的过程。

4. ICG

ICG模块的缩写是integrated Clock Gating的意思, 有些地方把这个东西叫isolate clock gating,应该是不对的。在较为先进的工艺库中一般会直接提供这个模块,不需要自己手动的搭建。但是需要知道其原理。

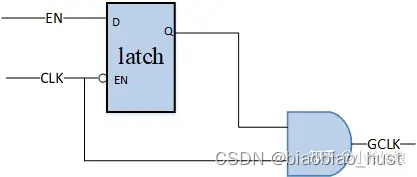

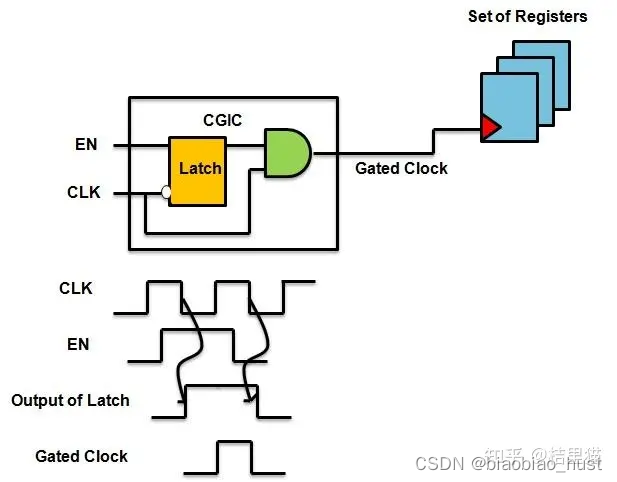

4.1 ICG原理

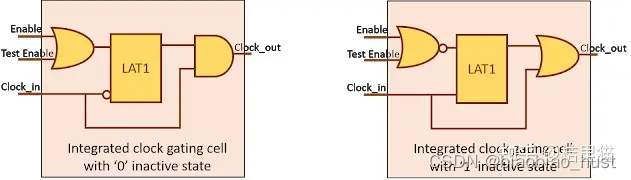

ICG模块一共有两种形式,或形式和与形式。其内部逻辑是用一个寄存器和两个与门组成的。

我们拿与门作为例子来讲。对于与门的ICG,只有clk为低电平也时EN信号才会通过ICG。保证了输出的第一个波形是上升沿。对于或类型的整好相反。可以类似分析。

ICG波形:

ICG在数字电路中有三个用途:

- 用于关断时钟,降低功耗

- 用于动态切换时钟时防止产生毛刺

- 用于时钟分频,后续讲

4.2 ICG要求

1.类型如何选:使用Or还是And ICG,可以自己手动搭建ICG么

答:这个比较简单,如果电路是上升沿触发的那么选and ICG,否则选Or ICG。原因是AND ICG第一个好的时钟是时钟上升沿。Or ICG相反。工艺库都提供,不建议手动搭建。主要原因是分立的搭建需要专门检查STA, 而ICG在库中写好了时序约束,避免很多错误。

2.En信号有什么要求

答:En不可以异步,En信号一定要同步。否则如果EN和时钟沿离得太近容易亚稳态。En一定不能是门控后的信号产生的,否则就死循环了。

3.ICG是手动加的还是自动加的

答:模块级的ICG手动加,寄存器级别的ICG综合工具自动加。

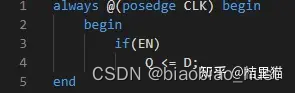

4.3 自动门控时钟

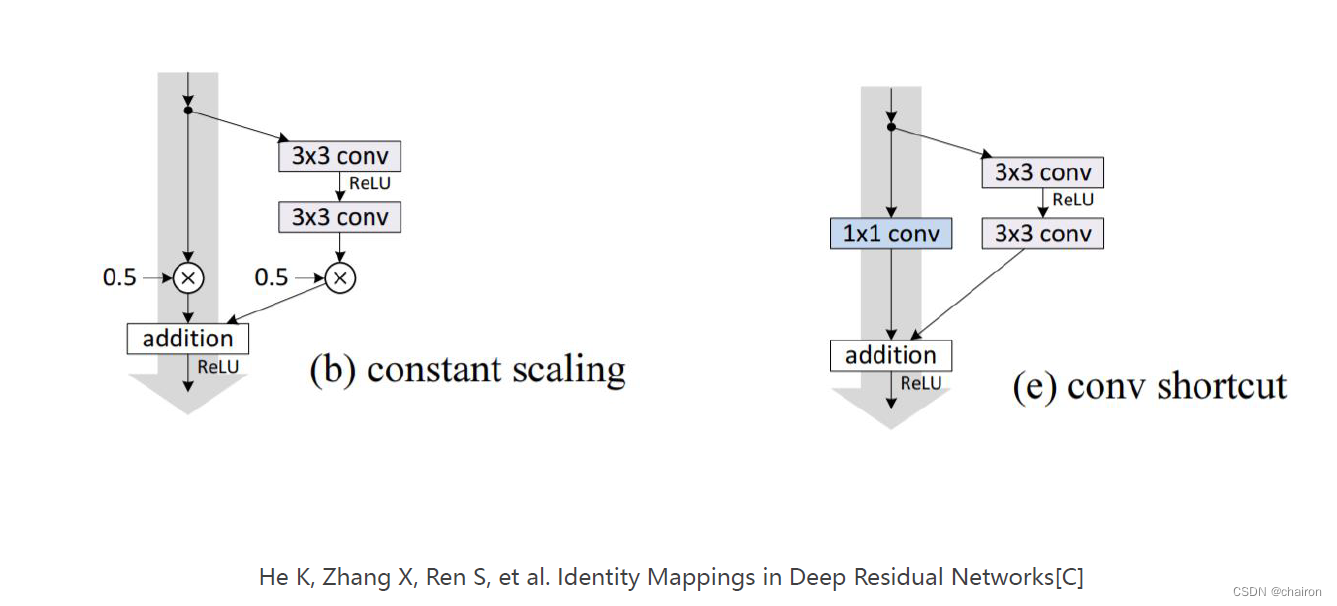

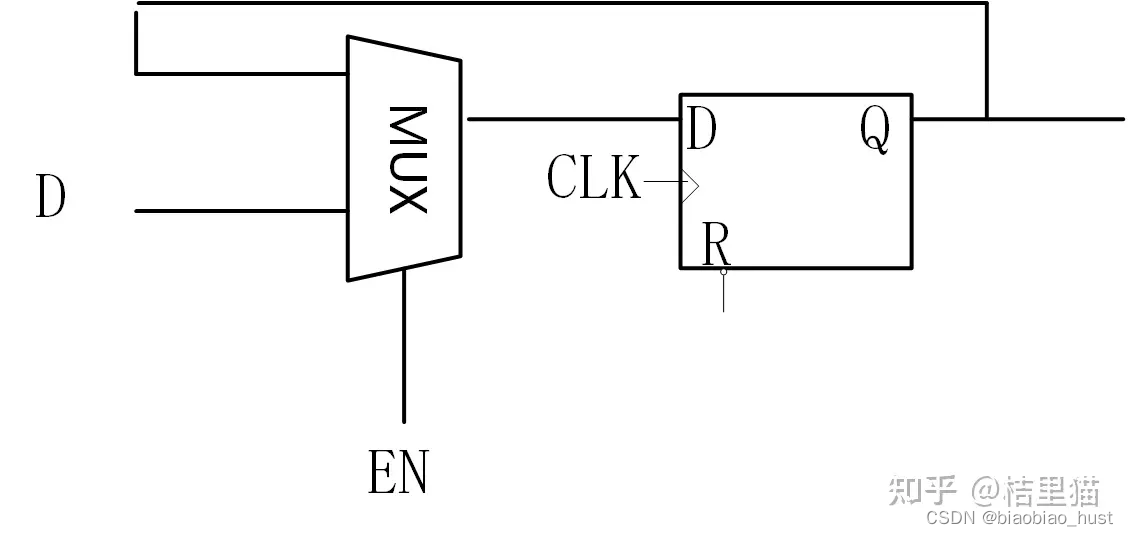

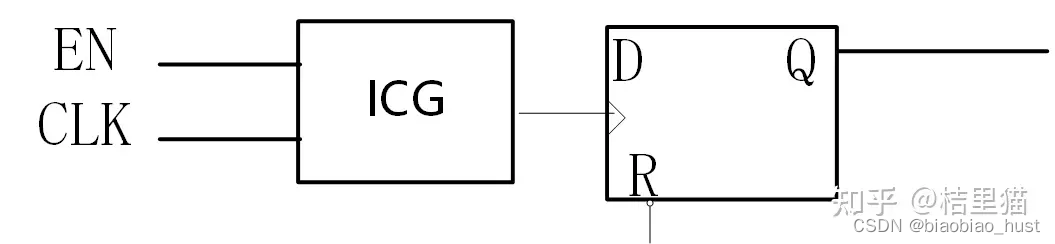

ICG模块有时是根据设计手动加入到电路里的,但对于寄存器级别的控制,其实综合工具可以直接帮忙加入。如下图所示,只要代码风格写的好,综合工具就能自动帮你门控。

如果不看低功耗的综合,综合出的电路是这样的:

如果开了低功耗的综合,综合出来就是这样的:

那么实际情况下怎么插入的?这个需要看综合策略。如果Q就1两个bit,那其实使用mux更省一些。如果Q比较宽,例如Q为32bit的话插入ICG就收益非常明显。既节省了功耗,1个ICG肯定是小于32个mux。

5. OCC

Delay Fault会影响芯片正常工作的频率,导致芯片的时序不能满足设计要求。因此Delay Fault成为影响芯片质量的主要因素之一。At-speed test已被证明是用来测试Delay Fault的有效方法,at-speed test就是让芯片在内部高速时钟上测试,但是该测试方法在fast capture mode下需要两个时钟脉冲,第一个时钟需要使得前一个scan flip-flop的值进行翻转来激活故障,第二个时钟需要使得前一个scan flip-flop的翻转值传播到后一个scan flip-flop,从而实现故障传播。这两个时钟来自于function clock,因此需要通过I/O pad提供这些at-speed clock脉冲,但是I/O pad可以支持的最大频率存在限制,OCC电路应运而生。

5.1 什么是OCC

片上时钟控制器(On-chip Clock Controllers ,OCC),也称为扫描时钟控制器(Scan Clock Controllers,SCC)。OCC 是插在SoC上的逻辑电路。用来做DFT测试,基本原理是在 scan shift 模式下, 选通慢速的ATE 时钟,load 或 unload 扫描链; 在 capture 模式下,对 free-running PLL clock 过滤筛选出 lauch 和 capture clock 进行at-speed 测试。在ATE(自动测试设备)上对芯片做ATPG测试时,OCC用于控制内部scan flip-flop时钟。

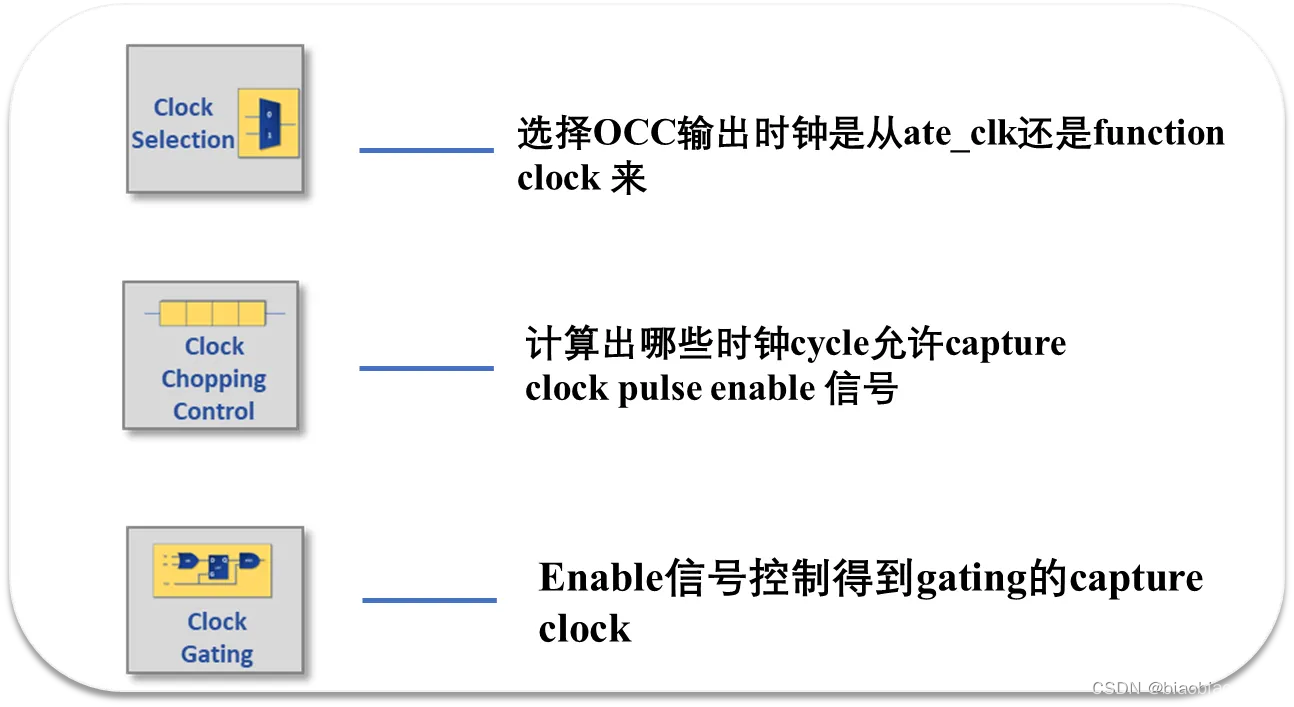

全速测试就是让芯片工作在自己高倍时钟频率上,这个频率往往是要高过ATE的时钟的。OCC就实现此功能。OCC电路可以实现ate clock和function clock之间的切换,并且控制在什么时刻跳转。所以standard的OCC在设计时需要拥有三个主要功能:clock selection, clock chopping control and clock gating。

5.2 OCC的架构及功能

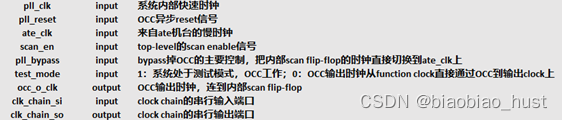

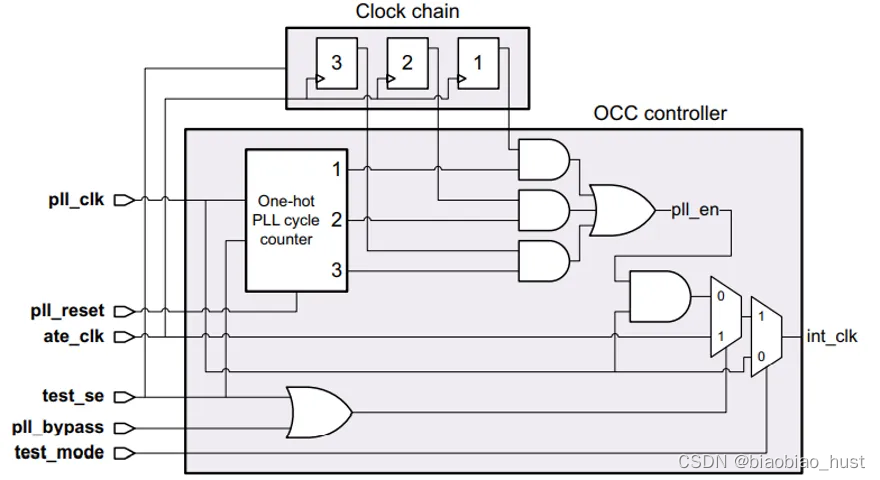

这里我们会介绍一下Synopsys的OCC 1.0 ,Synopsys的OCC定义了多个输入输出端口:

5.2.1 function mode

当OCC处于function mode时,test mode = 0,此时pll _clk选通,OCC会向内部 design输入function clock,此时可以将OCC电路视为transparent。

5.2.2 shift mode

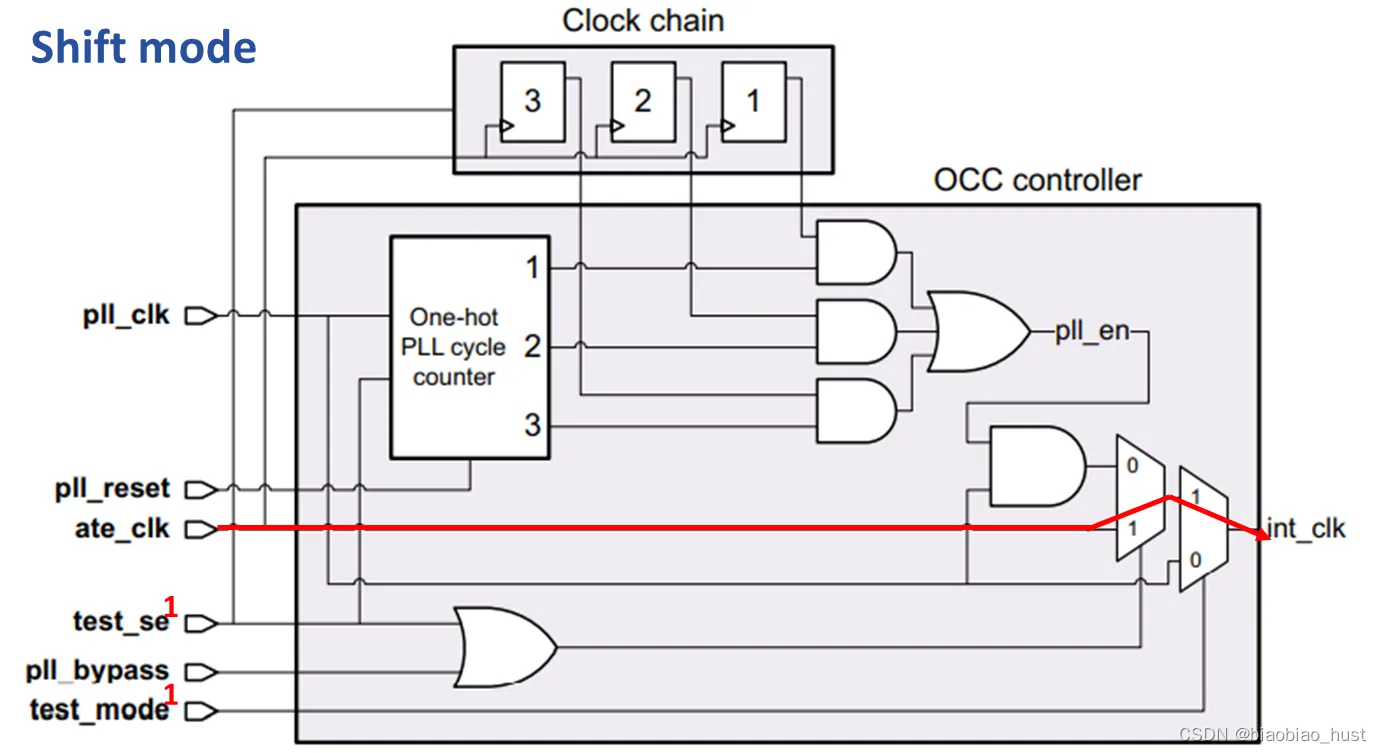

当OCC处于shift mode时,我们在ate clock的控制下将测试向量load进internal scan chain和clock chain内,所以test mode = 1,scan_en = 1,此时ate _clk选通,完成shift操作。

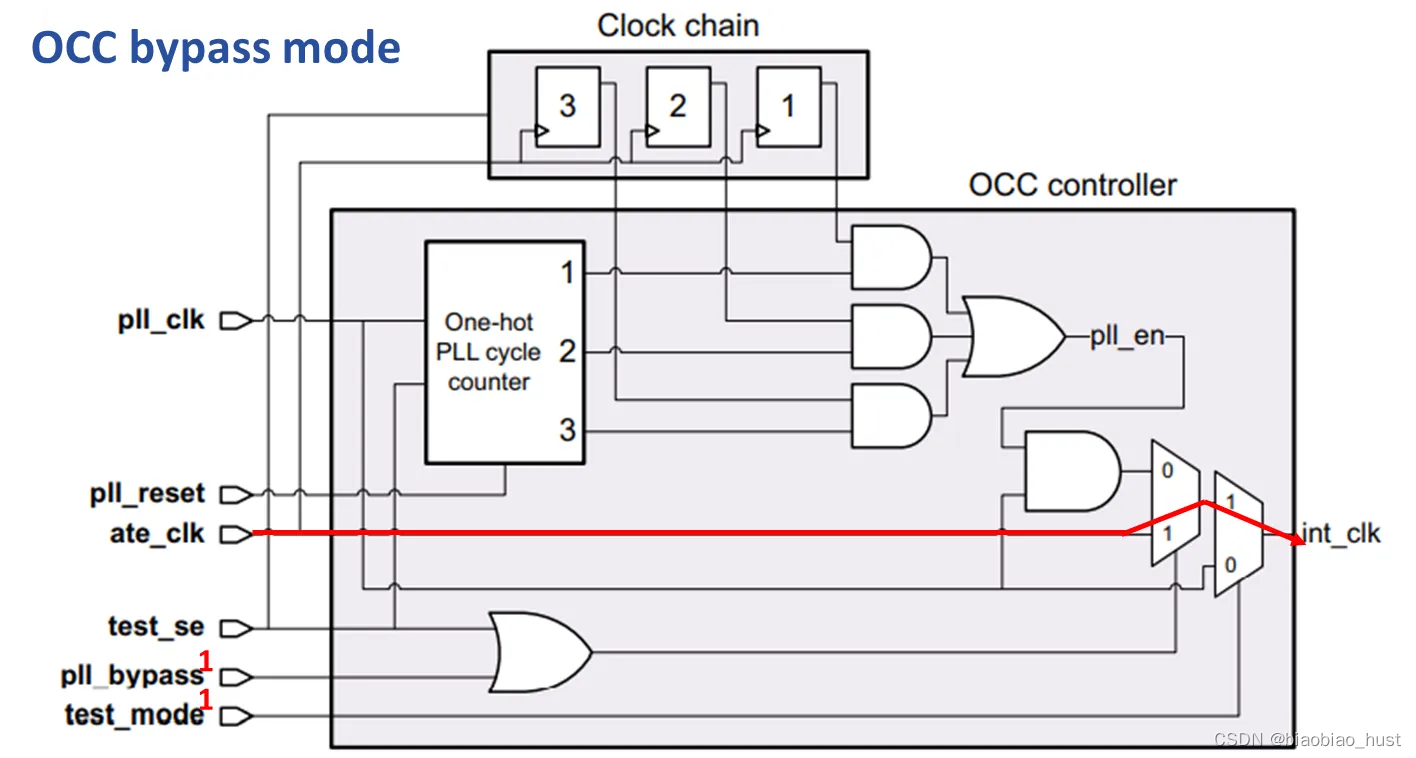

5.2.3 bypass mode

Synopsys的OCC 1.0 没有真正的slow capture mode,需要做stuck-at 测试时,可以直接从ATE机台提供OCC bypass mode capture clock。通过外部ATE机台对ate clock的pulse进行适当的控制就可以进行stuck-at测试,不需要clock chain的控制。此时test mode = 1,pll_bypass = 1。

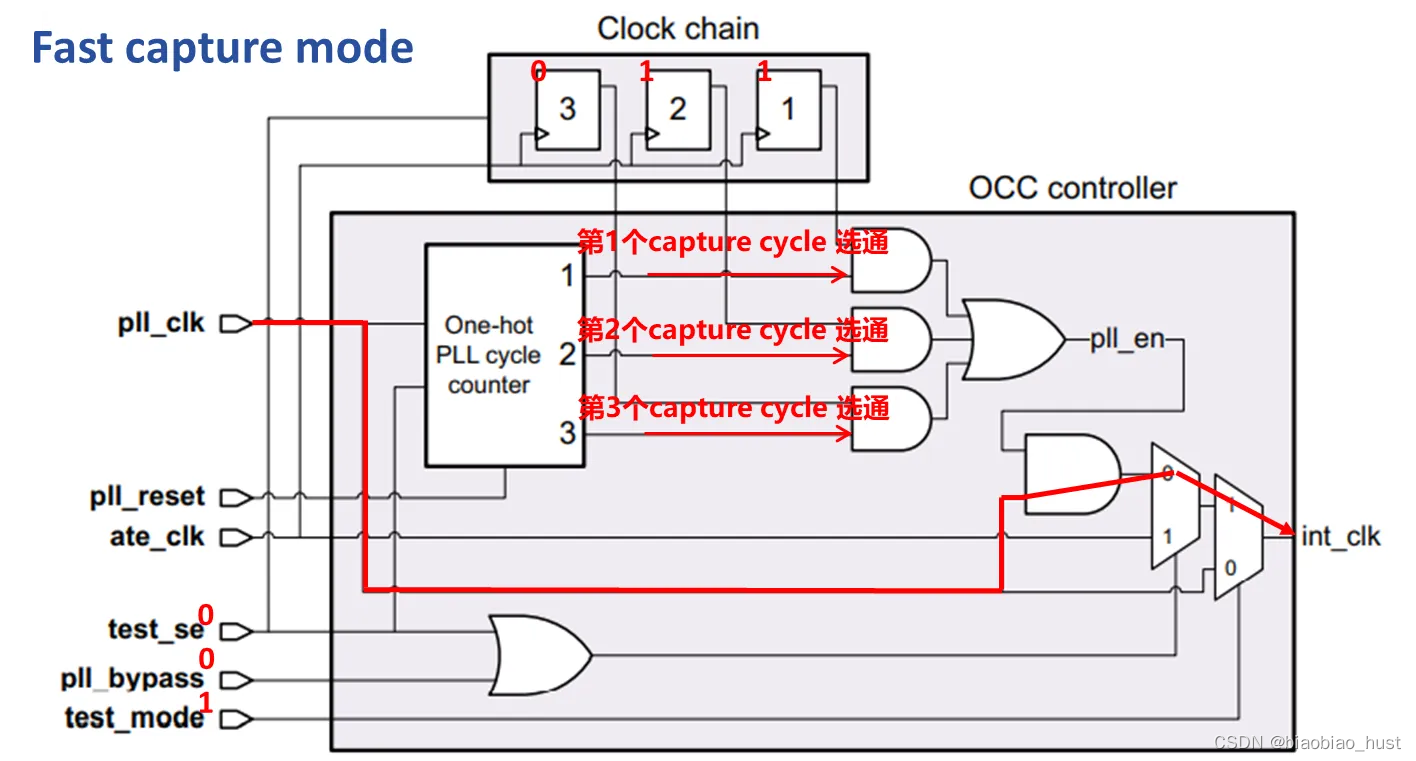

5.2.4 fast capture mode

当OCC处于fast capture mode时,期望在capture阶段生成两个function clock脉冲。所以test mode = 1,scan_en = 0,pll_bypass = 0,此时pll _clk选通,并且PLL cycle counter 和clock chain的输出经过ICG共同决定gating几个时钟脉冲,完成at-speed测试。

Fast capture mode的波形图如下图所示,下面我们来简单地分析一下。

当我们进行capture操作时,scan enable信号要从1变为0,为了保证得到的是稳定的0信号,我们需要先经过sync cell的3个synchronization cycles。

通过先前shift过程中load在clock chain里的test pattern(0110)以及PLL cycle counter的共同控制,在第2、3个cycle给出两个pulse,即launch和capture。

最后scan enable信号从0变为1,完成capture的操作,进入shift过程。

需要注意的是,对于Synopsys的OCC,Scan_en = 1后,ate clock在第二个pulse才出现 ,此过程被称为pre_shift 。

5.2.5 OCC的位置

OCC电路是一个IP,所以我们需要打断Design的一些节点,将其插入。如果external clock port直接驱动scan flip-flop, 测试机可以直接在clock port上加激励控制输入clock的频率和时间,ATPG可以产出这样的pattern。然而大部分design中flip-flop都是由倍频分频处理过的PLL clock驱动, 没法从外部去直接控制,所以需要OCC控制频率和什么时间出pulse。所以,OCC应插在PLL clock的output之后或是不能直接被primary input控制的clock处。

OCC电路的插入需要遵守一些规则:

- External clock可以不用OCC

- Internal clock必须插OCC

- OCC 插在PLL或者divider out clock后

- Internal clock和external clock可以混合插入OCC

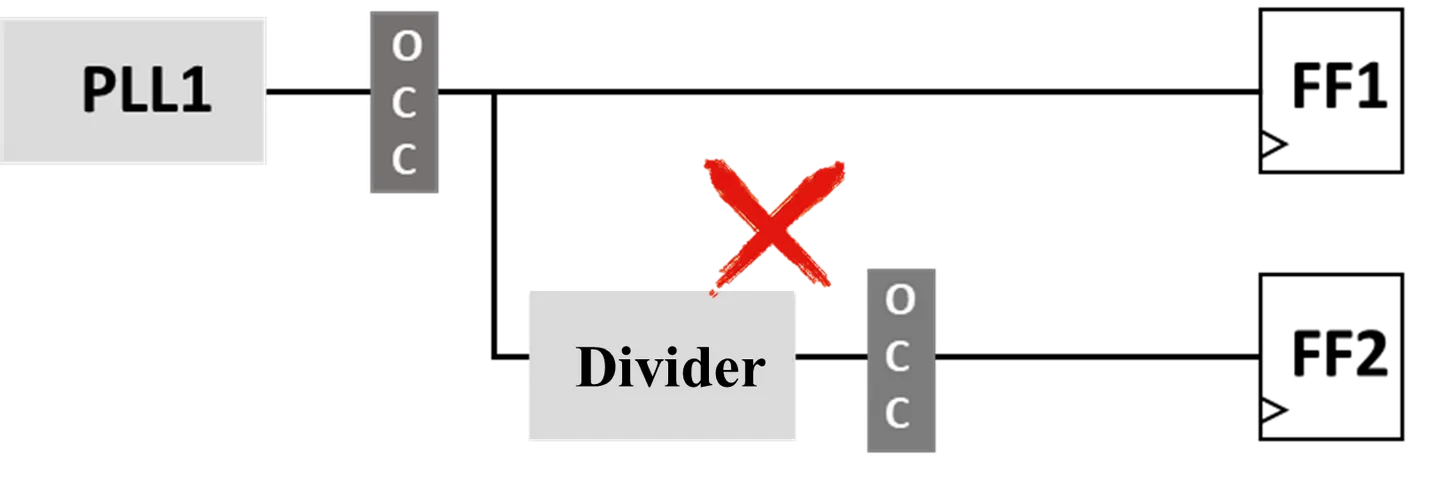

以多个插入DFT的OCC为例,可以看到下图是一个错误插入方法,原因是驱动divider的clock已经被OCC执行过chopping的动作,不再是free-runing的clock,这样就无法得到期待的clock。

图为OCC的正确插入方法,驱动divider的clock也是来自于PLL的free-running的clock。