数字量采集-2024年01月27日-二刷

文章目录

- 分析考虑一个波形的六要素:

- 项目需求分析:

- 高低电平数字量采集电路设计

- RS485

- 差分信号传输

- SP3485 芯片引脚

- RS485 转 TTL 电路

分析考虑一个波形的六要素:

高电平

低电平

上升时间

下降时间

频率/周期

占空比

正常的一个电平有 4 种状态:高电平、低电平、悬空态(NC)、高阻态(Z)

高阻态:若上拉/下拉,则属于高阻态,只提供初始状态

悬空态:也叫不确定态,任何芯片的所有管脚都不能处于悬空态,因为悬空态会增加设备出现错误的概率,应当避免这种状态!

项目需求分析:

波形是触发式的,可能信号来了会拉低,但是信号没了又变高了,所以没有周期性,也就没有占空比,因此只有高低电平需要考虑:

| 外部输入 | 单片机 | ||

|---|---|---|---|

| 高电平 | 10-14V | 高电平(0.7 倍 Umax) | 2.3V |

| 低电平 | 0-1V | 低电平(0.3 被 Umax) | 1V |

| 转换电路需要将左边的数据转为右边的数据 |

高低电平数字量采集电路设计

方法一:(仅思考,不可行)

:::tips

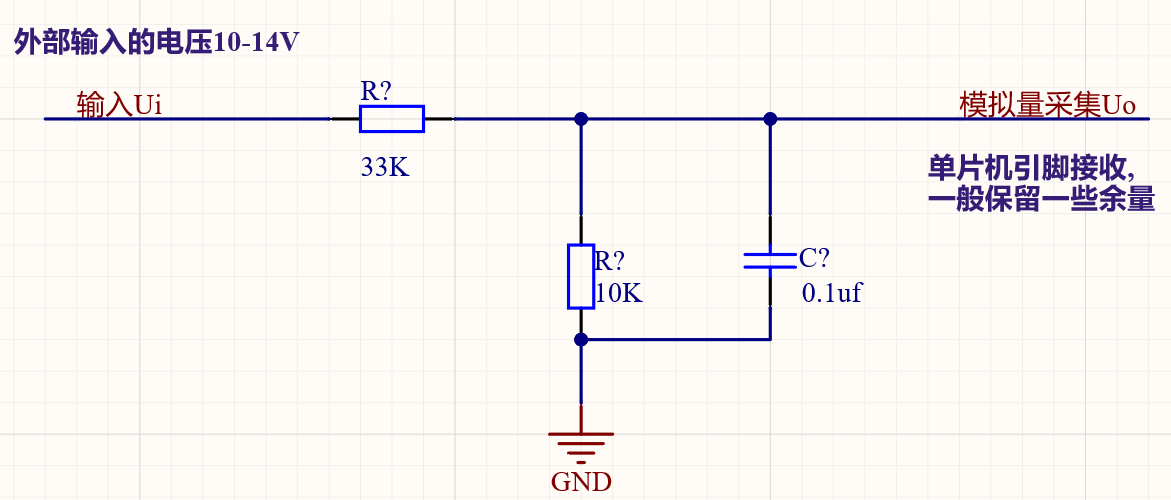

分析可得外部输入的 10V 对应着单片机的 2.3V,则应当用分压电路将其分压

分压比例系数

=

10

2.3

≈

4.5

分压比例系数=\frac{10}{2.3}≈4.5

分压比例系数=2.310≈4.5,由上一节电阻选型可知,我们应当选择 10K 级别的电阻作为参考电阻,那么初步假设此时的电路为:

10

k

45

k

≈

2.2

V

10

V

\frac{10k}{45k}≈\frac{2.2V}{10V}

45k10k≈10V2.2V

设计思考心路:

step1: 先根据 4.5 ,得出 10/45,然后得出分压电阻分别选 10K 和 45K,然后验证自己的选型是否满足能将 10V 电压分压至 2.2V。但是由于 2.2V 不满足单片机对高电平的定义(2.3V),因此将 35K 电阻变小一些,假设其为 33K(分母变小,分子不变,整体变大);

10

k

43

k

×

10

=

2.33

V

\frac{10k}{43k}×10=2.33V

43k10k×10=2.33V(满足条件了)

step2: 然再验证能不能把 14V 电压分压降至 3.3V 以内

10

k

43

k

×

14

=

3.25

V

<

3.3

V

\frac{10k}{43k}×14=3.25V < 3.3V

43k10k×14=3.25V<3.3V,因此满足条件。

但是这样设计存在一个问题:如果外部输入电压是 10-20V 呢,对于 20V 而言,这样的分压电路必然不能将电压降至 3.3V 以内

对于

3.3

V

而言:

10

k

43

k

×

20

=

4.65

V

<

3.3

V

对于3.3V而言:\frac{10k}{43k}×20=4.65V < 3.3V

对于3.3V而言:43k10k×20=4.65V<3.3V。远超 3.3V 因此不合适,若是打算增大分母也就是增大 33K,那么可能又出现一开始的无法将电压保持在 2.2V 以上

综上,采用这样的电路结构,很难设计出来。

:::

去补二极管的知识了

方法二:利用二极管

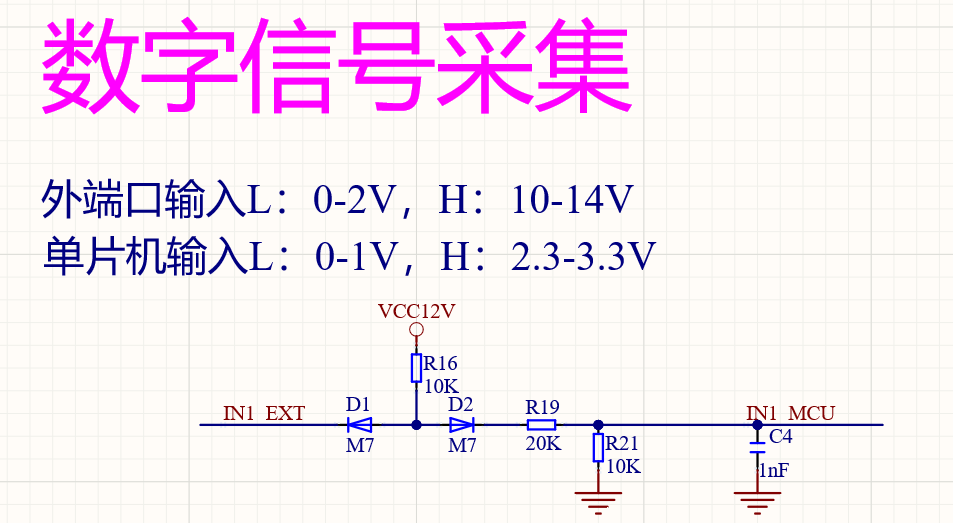

总电路图:

分析 1:当外部输入高电平时(H:10-14V)

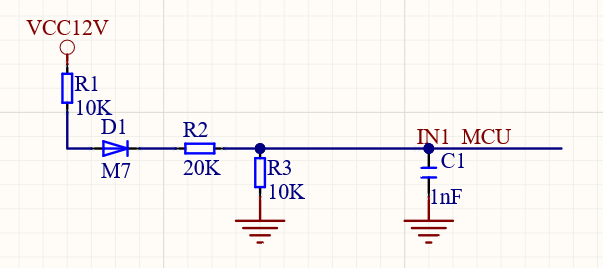

由于二极管的单向导电性,此时 IN1_EXT 无法进入,是 VCC12V 起作用让电路始终处于高电平的状态,可以将电路抽离出来如下图所示:

此时可以通过分压公式可得,IN1_MCU 的电压值为 R3 电阻上的电压,由分压计算可得是在单片机能检测到的高电平的范围之内的

U

I

=

R

3

R

1

+

R

2

+

R

3

∗

(

V

C

C

−

0.7

)

=

10

K

40

K

∗

(

12

V

−

0.7

V

)

=

2.8250

V

U_I=\frac{R3}{R1+R2+R3}*(VCC-0.7)=\frac{10K}{40K}*(12V-0.7V)=2.8250V

UI=R1+R2+R3R3∗(VCC−0.7)=40K10K∗(12V−0.7V)=2.8250V

2.3

<

U

I

<

3.3

2.3 < U_I < 3.3

2.3<UI<3.3

:::tips

为什么电压进不来?A:去看二极管的特性吧(单向导电性)

:::

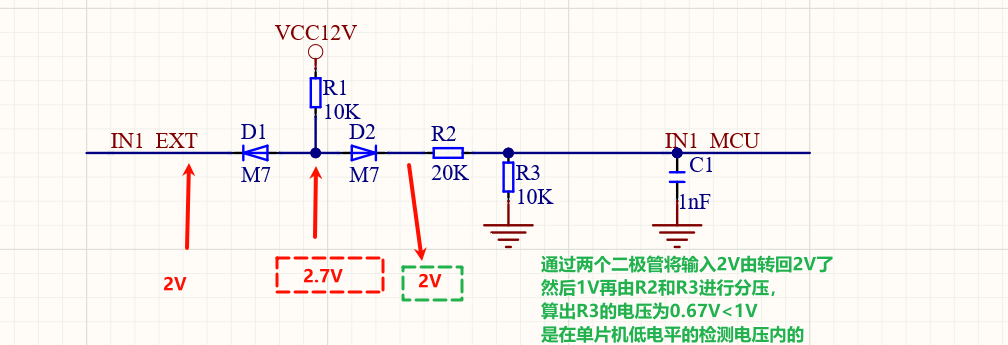

分析 2:当外部输入低电平时(H:10-14V)

重点在于理解 2.7V 的原因

RS485

485、422、232 等都是 UART(串口),但是表现出不同的电平协议:不同的电压范围触发高低电平

485 转 ttl 需要用到转换芯片将 485 中的高低电平转为 ttl 规则的高低电平

ttl 电平的 H 和 L:H(2.3-3.3v)、L(0-1v)

485 只有 AB 两个线判断差分信号 0 和 1,因此是半双工

422 由 ABYZ 四个线,因此 AB 和 YZ 同时进行差分信号传输,实现了全双工

串口有 RX 和 TX 是全双工的,同时收发

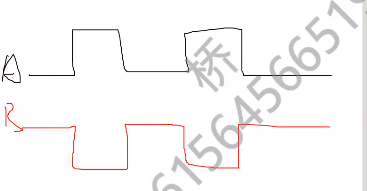

差分信号传输

RS485 通信采用差分信号传输,通常情况下只需要两根信号线就可以进行正常的通信。

在差分信号中,逻辑0和逻辑1是用两根信号线(A+和B-)的电压差来表示。

- 逻辑 1:两根信号线(A+和B-)的电压差在 +2V~+6V 之间。

- 逻辑 0:两根信号线(A+和B-)的电压差在 -2V~-6V 之间。

差分和单端

单端是指参考地

差分是不参考地,A 与 B 两个线之间互相参考

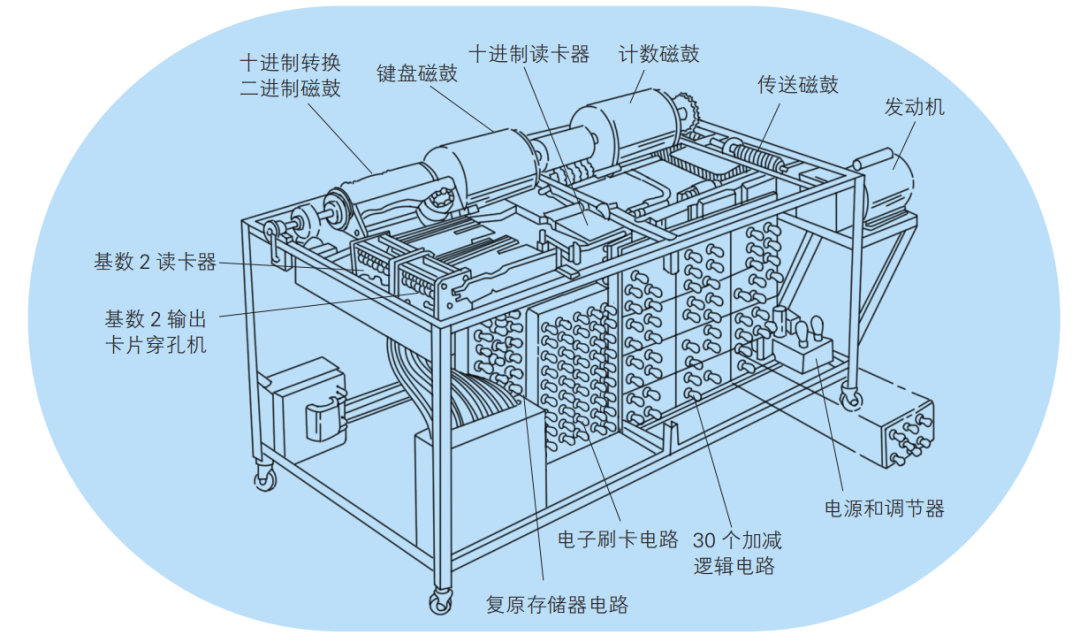

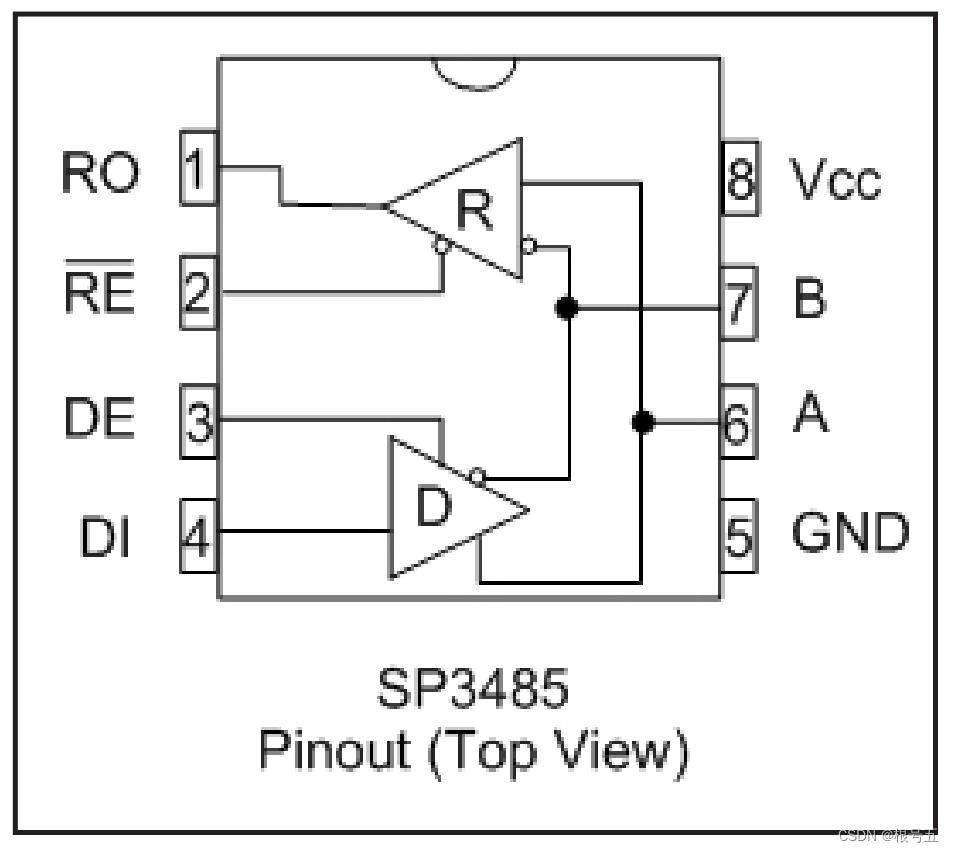

SP3485 芯片引脚

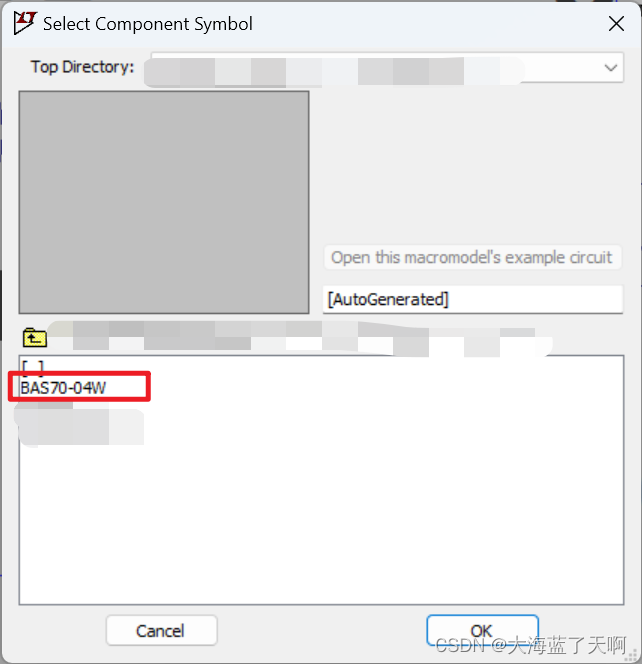

选用 SP3-485 转换芯片(差分转单端)

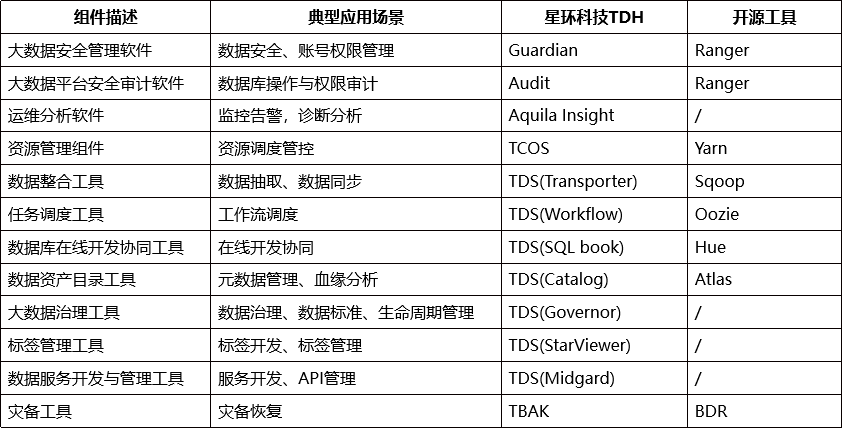

| 引脚 | 名称 | 功能 |

|---|---|---|

| 1 | RO | 接收器输出----接RX |

| 2 | RE | 接收器输出使能(低电平-MCU接收使能) |

| 3 | DE | 驱动器输出使能(高电平-MCU发送使能) |

| 4 | DI | 驱动器输入----接TX |

| 5 | GND | 接地 |

| 6 | A | 驱动器输出/接收器输入(同相) |

| 7 | B | 驱动器输出/接收器输入(反相) |

| 8 | VCC | 芯片供电+3.3V |

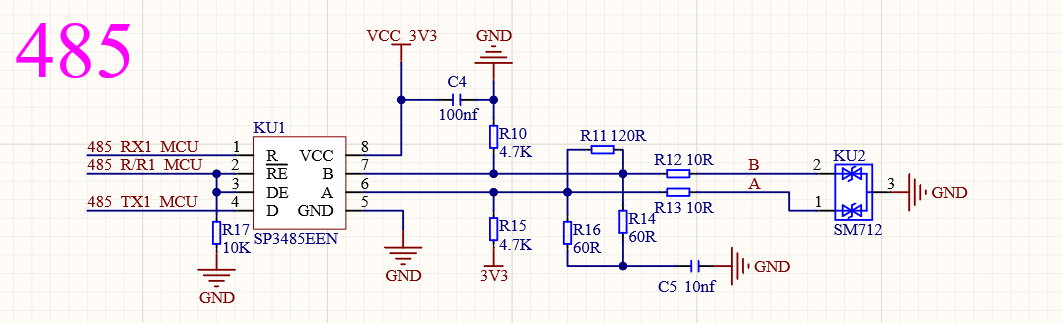

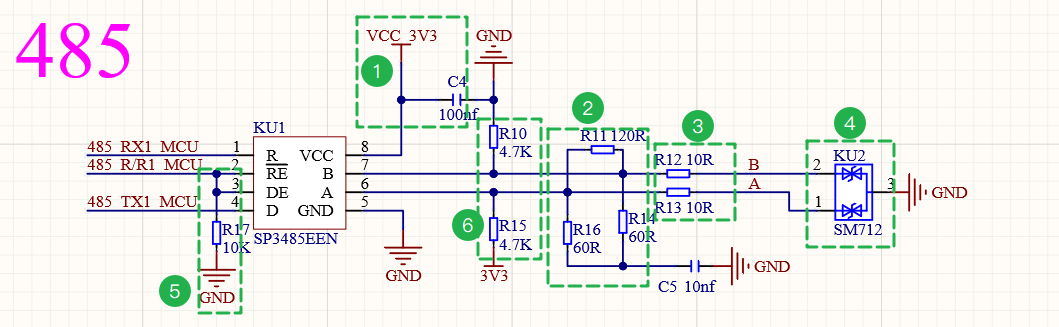

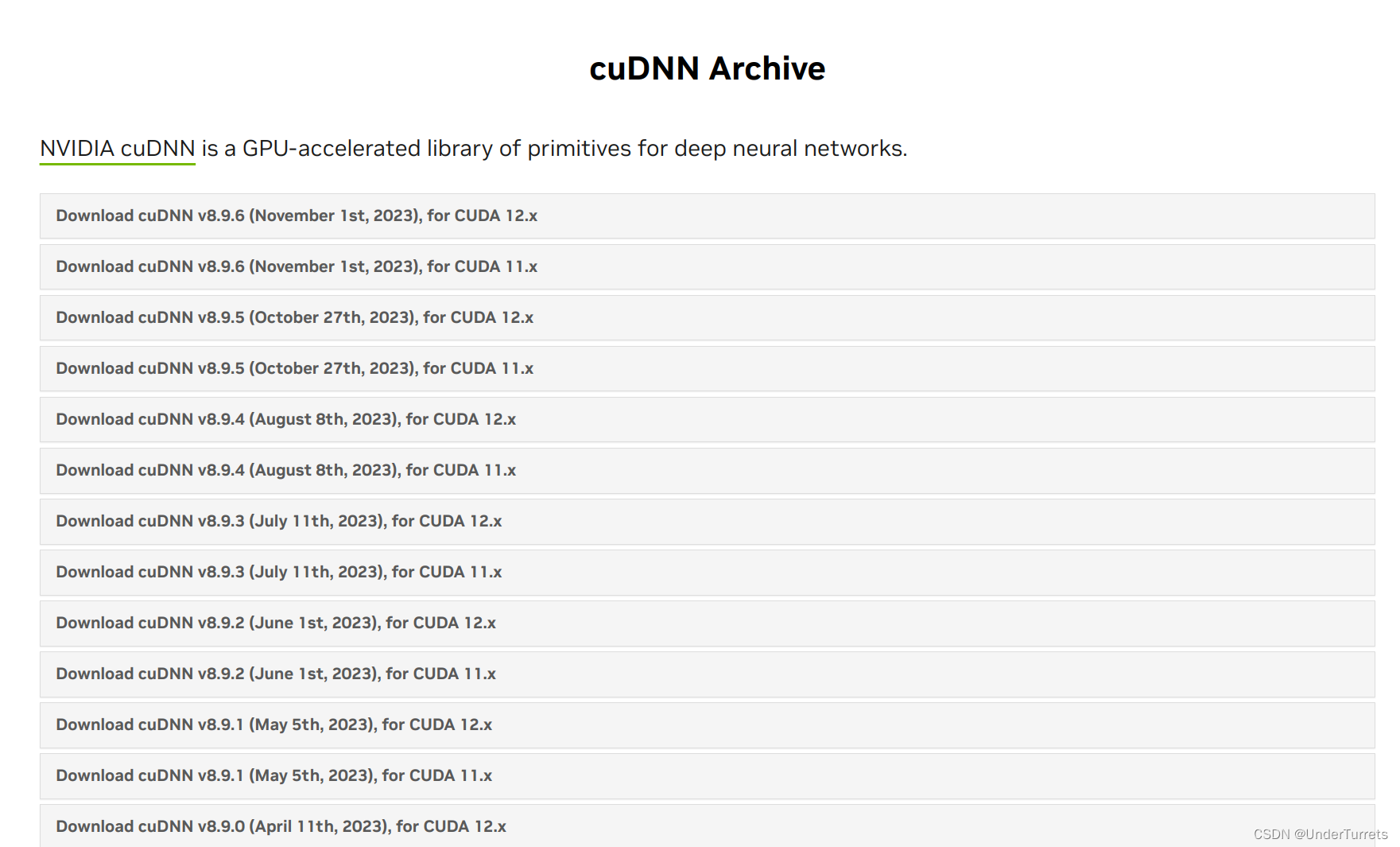

RS485 转 TTL 电路

下面进行一些解释:

① 电源端接 VCC,芯片功率不大的情况下电源的滤波电容取 0.1uf/100nf

② 一般的总线都是要加终端电阻的,但是也有可能不加,这终端电阻作用是什么呢?它是防止反射的,这个反射是在高频下进行说明的,就是终端匹配啊(一般电阻就是取 120R)

③ 保护电阻

④ 静电管,防止静电带来的不必要的干扰(一般是手拔插时带的静电)

⑤ 给引脚加一个下拉电阻,让其默认处于低电平状态(默认处于单片机接收初态)

![[BJDCTF 2020]Easy](https://img-blog.csdnimg.cn/direct/26bb607deff243c2b5c47ac06d6b9fb1.png)

![[UI5 常用控件] 03.Icon, Avatar,Image](https://img-blog.csdnimg.cn/direct/54738f73de1744bc99b1e9a3dc79b489.png)