信号名 | 方向 | 描述 |

TxData | IN | 并行数据输入总线 |

TxDataValid | IN | 1:表示cycle数据有效; 0:表示cycle数据无效 |

RxData | OUT | 并行数据输出总线 |

RxValid | OUT | 1:表示符号锁及当RxDataValid有效时,数据有效 |

|

|

|

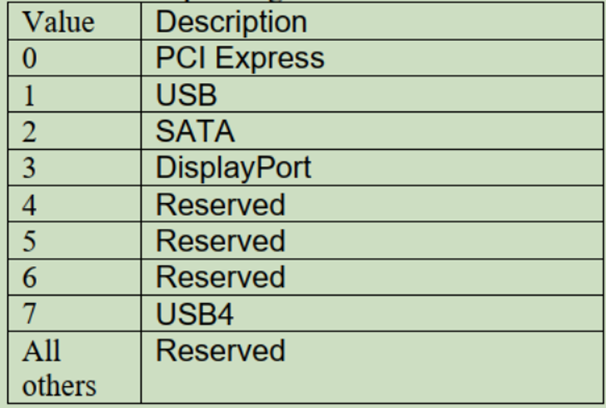

PHY MODE | IN |

|

PHY STATUS | OUT |

|

SerDesArch | IN | 该信号表示是否使能Serdes架构; |

SRISEnable | IN | 配置PHY是否为了PCIe支持SRIS; |

TxDetectRx/ Loopback | IN | 表示PHY开始接收器检测操作或开始环回; |

TxElecIdle | IN | 除了环回模式,强制Tx输出电空闲 |

Reset | IN | 复位发送器和接收器;该信号为异步信号 |

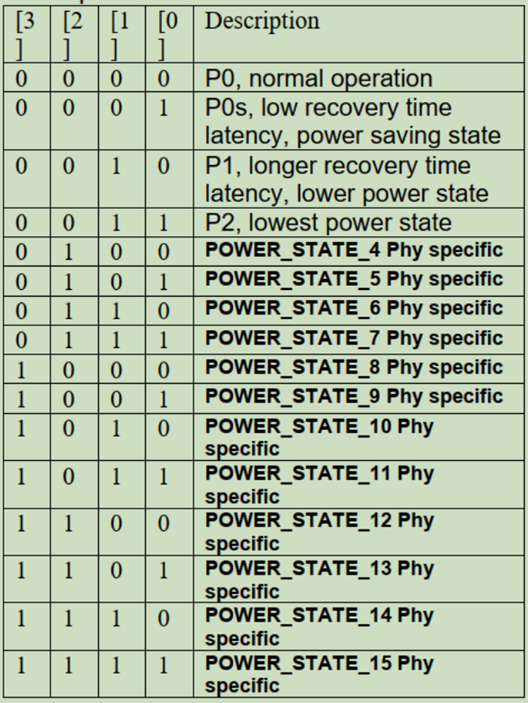

PowerDown | IN |

|

RxElDetectDisable | IN | 1:表示关闭接收端电空闲逻辑 |

TxCommonModeDisable | IN | 1:表示关闭发送端DC共模逻辑 |

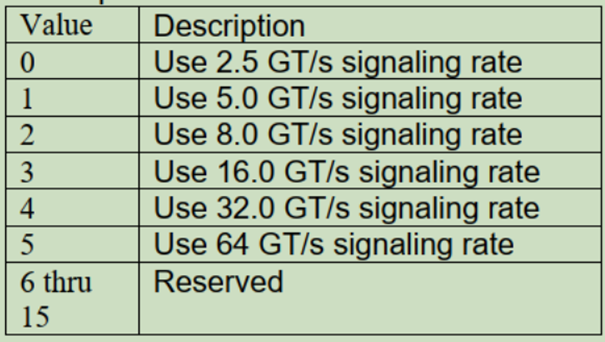

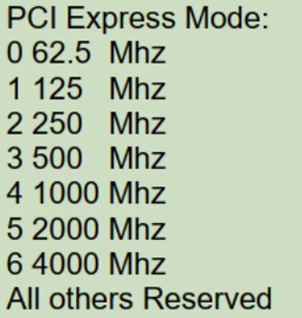

Rate | IN |

|

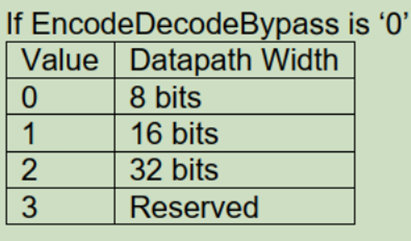

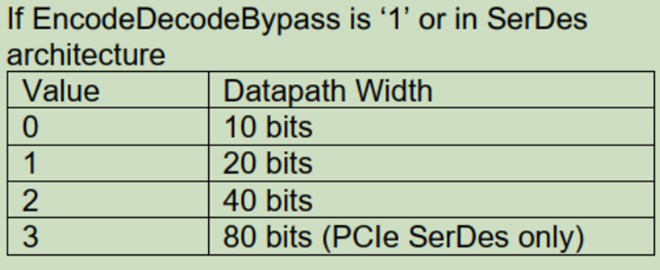

Width | IN |

|

PCLK Rate | IN |

|

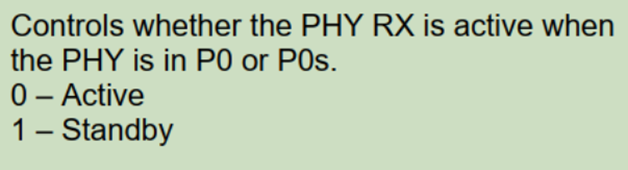

RxStandby | IN |

|

RefClkRequired | IN | 1:表示低功耗模式下可以安全的移除参考时钟 |

|

|

|

PIPE接口基本描述

news2026/2/15 20:08:42

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/139707.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

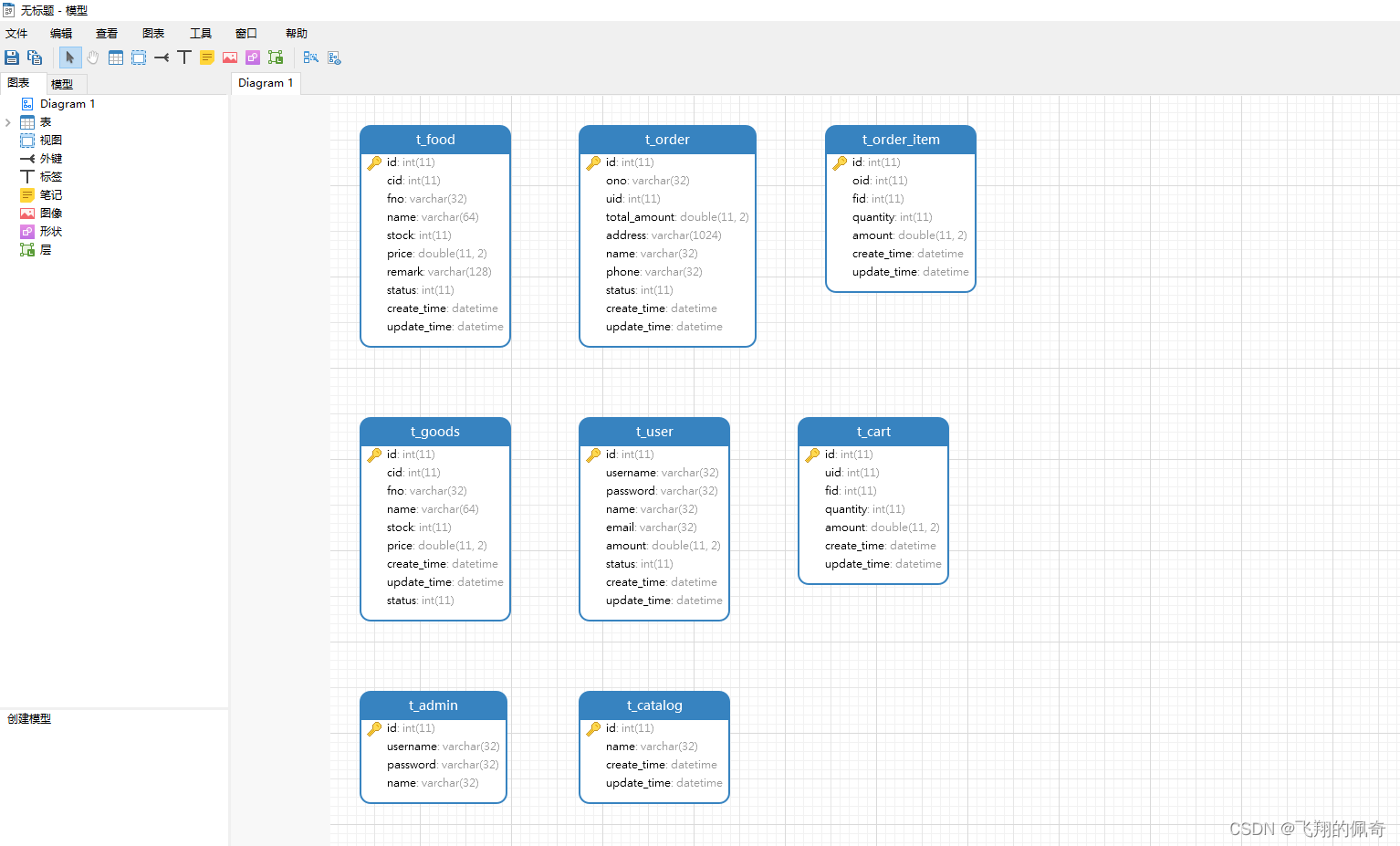

java swing电子商务系统

一、项目简介

本项目是一套基于java swing的电子商务系统,主要针对计算机相关专业的正在做毕设的学生与需要项目实战练习的Java学习者。 包含:项目源码、数据库脚本等,该项目附带全部源码可作为毕设使用。 项目都经过严格调试,ec…

opencv案例实战——银行卡模式匹配识别

系列文章目录

1.图像读取及其通道与灰度 2.图像填充与图像融合 3.图像滤波 4.图像阈值 5.腐蚀与膨胀 6.图像梯度 7.边缘检测 8.轮廓与轮廓特征 银行卡模式匹配识别系列文章目录前言案例介绍划分模板1.思路2.获取边缘3.获取外接矩形图像预处理切割礼帽操作分割数字块sobel算子膨…

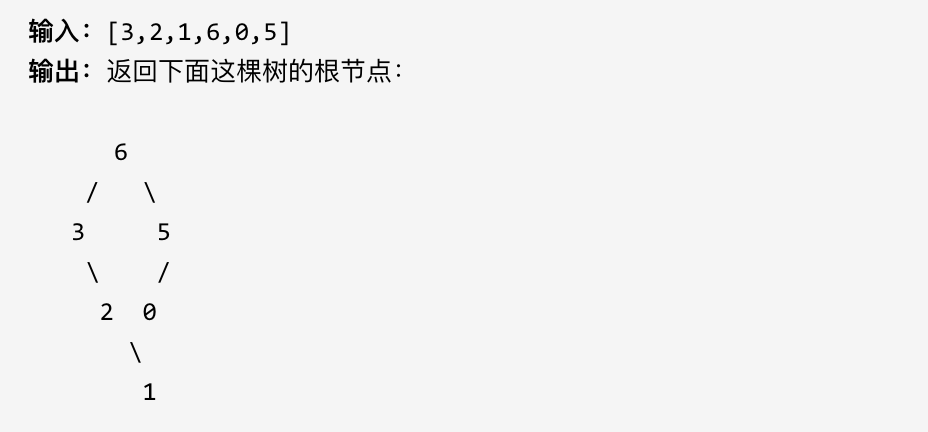

LeetCode题解 二叉树(十):654 最大二叉树;617合并二叉树

654 最大二叉树 medium

给定一个不含重复元素的整数数组。一个以此数组构建的最大二叉树定义如下:

二叉树的根是数组中的最大元素。左子树是通过数组中最大值左边部分构造出的最大二叉树。右子树是通过数组中最大值右边部分构造出的最大二叉树。

通过给定的数组构…

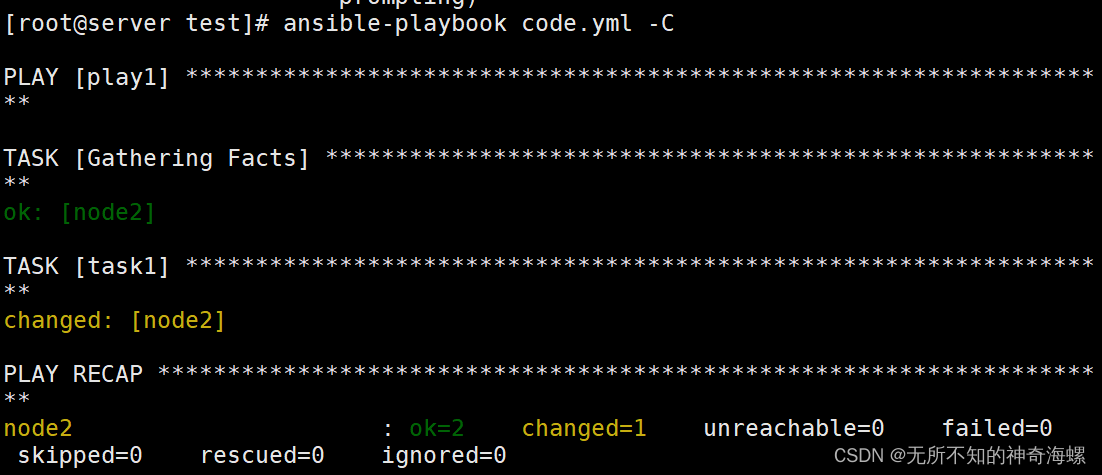

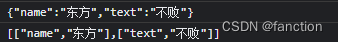

RHCEansible 编写playbook---yaml

YAML 语言特性 YAML的可读性好 YAML和脚本语言的交互性好 YAML使用实现语言的数据类型 YAML有一个一致的信息模型 YAML易于实现 YAML可以基于流来处理 YAML表达能力强,扩展性好YAML的三种数据结构 对象: 键值对的集合,又称为映射、哈希、字典…

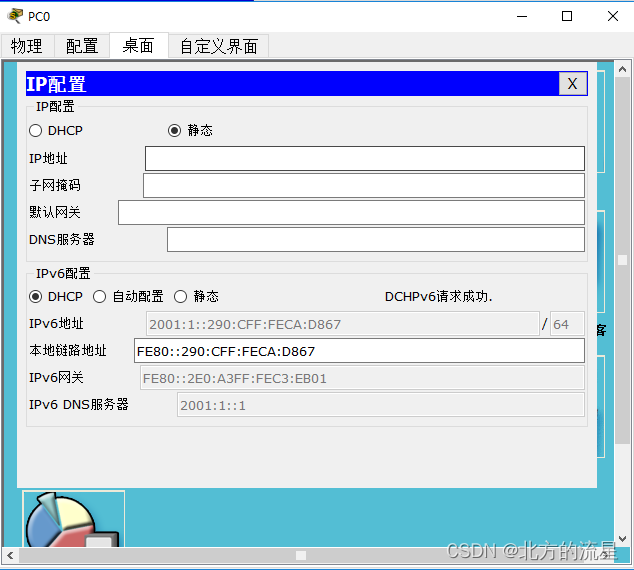

思科路由器DHCPv6服务配置

配置如下

Router>ena

Router#conf t

Router(config)#host R1

R1(config)#ipv6 unicast-routing

R1(config)#int g0/0

R1(config-if)#ipv6 add 2001:1::1/64

R1(config-if)#no sh

R1(config-if)#exit

R1(config)#service dhcp

R1(config)#ipv6 local pool v6pool …

CTF中的PHP特性函数(中)

前言

上篇文章给大家带来了PHP中最基本的特性,不知道大家学习的怎样了,回顾上文,我们讲了MD5强弱碰撞以及正则匹配的绕过,总体来看还是很简单的,下面给大家带来新的PHP特性讲解,会稍微比上一篇难一些。

i…

开源工作流引擎如何支撑企业级 Serverless 架构?

作者:董天欣(雾雾)

Serverless 应用引擎(SAE)是一款底层基于 Kubernetes,实现了 Serverless 架构与微服务架构结合的云产品。作为一款不断迭代的云产品,在快速发展的过程中也遇到了许多挑战。如…

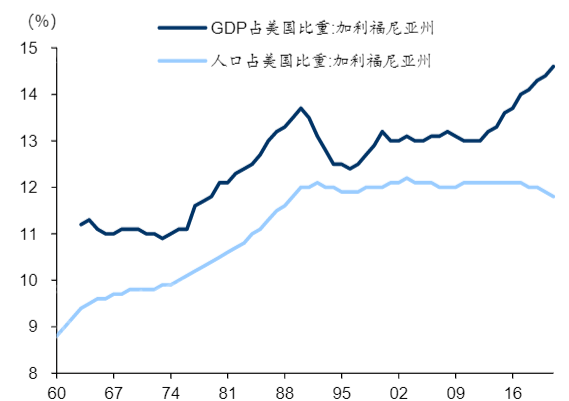

2022年统一大市场研究报告

第一章 行业概况

国内统一大市场指的是在全国范围内,在充分竞争以及由此形成的社会分工基础上,各地区市场间、各专业市场间形成了相互依存、相互补充、相互开放、相互协调的有机的市场体系。在这种市场体系下,商品和要素能够按照价格体系的调…

干货 | 在Docker 上搭建持续集成平台 Jenkins

Docker是一个开源的应用容器引擎,基于 Go 语言开发,Docker 可以让开发者打包他们的应用以及依赖包到一个轻量级、可移植的容器中,然后发布到任何流行的系统。Docker 是世界领先的软件容器平台,Docker 官方的口号是”调试你的应用&…

Three.js学习(二)three.js的一些基本操作

文章目录1.鼠标操作三维场景旋转、移动和缩放2.场景中添加新的三维图形3.设置材质效果4.光源效果1.鼠标操作三维场景旋转、移动和缩放 使用THREE的OrbitControls控件,可以实现鼠标控制三维图形的操作。主要是通过监听鼠标操作,控制相机的三维参数。

imp…

python数据分析-matplotlib、numpy、pandas

数据分析概述数据分析就是用适当的方法对收集来的大量数据进行分析,帮助人们在一处判断,以便采取适当行动数据分析流程jupyter notebook说明matplotlib:Matplotlib — Visualization with Python基本要点能将数据进行可视化,更直观…

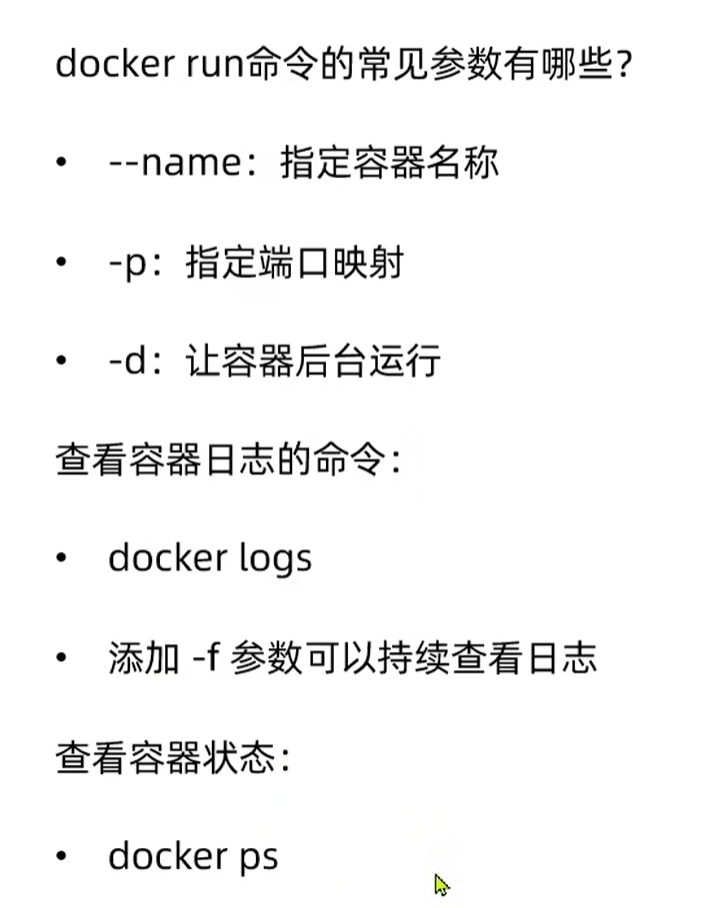

docker基本命令演示

docker拉取redis镜像演示首先前往:https://hub.docker.com找到需要的redis镜像然后 点击之后使用命令 docker pull redis 拉取redis 成功之后使用命令 docker images 查看本地的镜像使用命令导出镜像到指定文件 docker save -o redis.tar redis:latestdocker save…

Android13适配

遇到的一些问题

1.WebChromeClient的 API onReachedMaxAppCacheSize 没了

onReachedMaxAppCacheSize overrides nothing // 扩充缓存的容量override fun onReachedMaxAppCacheSize(spaceNeeded: Long, totalUsedQuota: Long, quotaUpdater: QuotaUpdater) {quotaUpdater.upda…

数据库,计算机网络、操作系统刷题笔记24

数据库,计算机网络、操作系统刷题笔记24

2022找工作是学历、能力和运气的超强结合体,遇到寒冬,大厂不招人,可能很多算法学生都得去找开发,测开 测开的话,你就得学数据库,sql,oracle…

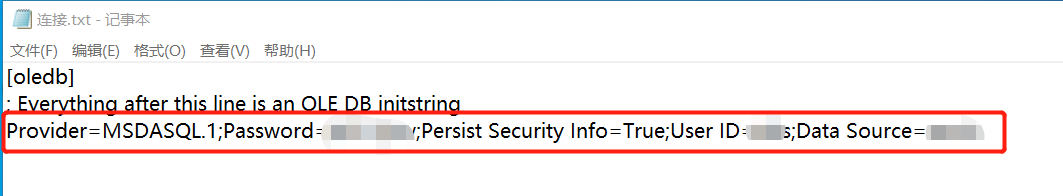

c++下 ADO+配置数据源连接oracle数据库

测试环境:在本地局域网内远程连接服务器端的oracle数据库,VS2013、ADO方式。2、本地安装oracle数据库客户端,具体是安装32位还是64位的数据库客户端,取决于我们编译的程序是32位的还是64位的(和计算机的系统位数没有关…

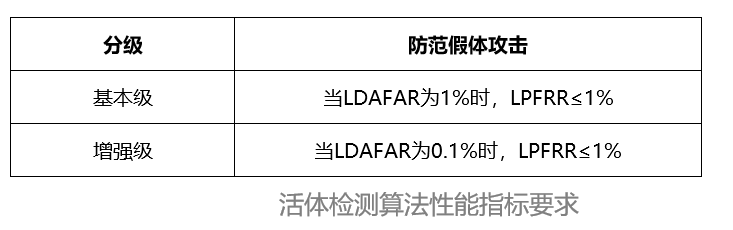

首款通过! 机器学习服务活体检测算法荣获CFCA权威安全认证

随着人脸识别技术在金融、医疗等多个领域的加速落地,网络安全、信息泄露等问题愈为突出,用户对应用稳定性和安全性的要求也更为严格。为保障各行业高效稳定的开展业务,提前发现和应对潜在安全风险,华为 HMS Core 机器学习服务&…

【回答问题】ChatGPT上线了!给我推荐20个比较流行的图神经网络模型

给我推荐20个比较流行的图神经网络模型

很高兴为您推荐流行的图神经网络模型。这里是我的推荐列表:

卷积神经网络 (CNN) 递归神经网络 (RNN) 自注意力机制 (Transformer) 双向递归神经网络 (BRNN) 门控循环单元 (GRU) 长短期记忆网络 (LSTM) 双流图神经网络 (Bi-D…

鲁大师2022牛角尖颁奖盛典落幕,年度最强产品揭晓!

1月4日,鲁大师2022年度牛角尖颁奖晚会在湖北襄阳成功举办。鲁大师的”牛角尖”奖是由过去一年上亿用户通过鲁大师测试得到的真实数据,以及鲁大师实验室通过专业的测试规范共同缔造的硬件奖项。颁发给的都是各大PC、手机、电动车领域最优秀、最顶尖的产品…