目录

一、时序例外约束

1.1 为什么需要时序例外约束

1.2 时序例外约束分类

二、多周期约束

2.1 多周期约束语法

2.2 同频同相时钟的多周期约束

2.3 同频异相时钟的多周期约束

2.4 慢时钟域到快时钟域的多周期约束

2.5 快时钟域到慢时钟域的多周期约束

三、虚假路径约束

四、最大/最小延时约束

一、时序例外约束

1.1 为什么需要时序例外约束

在STA中时序分析工具默认的时序检查方式可能与实际情况不吻合,此时就需要额外增加一些约束命令,用于调整时序检查方式,添加的这些额外的时序约束称为时序例外约束。

如以下情况就可以通过时序例外约束改善系统时序:

- 某些逻辑的时序单元不是每个时钟周期都进行数据采样传输,可以使用多周期约束;

- 对时序路径施加更紧的约束以获得更大的时序余量,可以使用最大最小约束;

- 某些路径组合是静态的或并不需要进行时序约束,可以使用虚假路径忽略。

因此对一些可以放宽时序要求的路径添加时序例外约束,以减少对布局布线的占用、释放资源给时序要求高的路径,确保系统更好的收敛。

1.2 时序例外约束分类

时序例外约束主要包括多周期约束、虚假路径约束和最大最小延时约束。

| 命令 | 功能 |

| set_multicycle_path | 多周期约束,指定从起始时钟沿到目标时钟沿所需的时钟周期数。常用于放宽某些时序路径的时序要求,以指导设计工具实现更合理的布局布线资源分配。 |

| set_false_path | 虚假路径约束,指定在设计中不做分析的时序路径,即在布局布线中作为最低优先级的路径。 |

| set_max_delay set_min_delay | 最大延时约束和最小延时约束。该约束将会覆盖设计默认的(已约束或系统默认)用于建立和保持时间分析的最大或最小路径延时时间,即用延时时间对特定时序路径添加的约束。 |

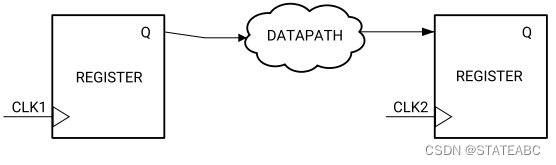

二、多周期约束

2.1 多周期约束语法

默认情况下,时序工具以单周期为单位进行时序路径分析。多周期约束可以调整建立时间和保持时间检查的起始时钟沿到目标时钟沿所需的时钟周期数,多周期约束可以设置在单个路径上,多个路径上,甚至两个时钟之间,使用set_multicycle_path命令实现。

set_multicycle_path <path_multiplier> [-setup|-hold] [-start|-end] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

- <path_multiplier> 用于设置修改约束路径分析的时钟周期数,取值必须是正整数。一般情况下setup/recovery分析是<path_multiplier>默认为1,hold/removal分析时<path_multiplier>默认为0,因此进行多周期约束就是改变<path_multiplier>默认参数;

- -setup和-hold用于指定约束命令所针对的是路径的建立时间分析(-setup)还是保持时间分析(-hold);

- -start和-end用于指定约束命令的<path_multiplier>参数是以源时钟(-start)还是以目标时钟(-end)作为参考时钟;

- -from指定约束路径的起始节点<startpoints>,可与to同时指定,若只指定form则表示覆盖所有从起始节点开始的路径;

- -to指定约束路径的终止节点<endpoints>,可与form同时指定,若只指定to则表示覆盖所有到终止节点结束的路径;

- -through指定约束路径所经过的节点<pins|cells|nets>,可选项。

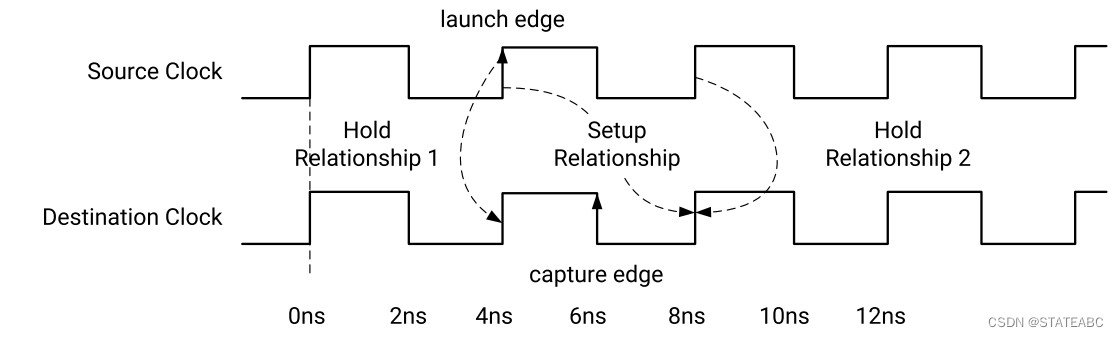

单周期约束就是按照单周期关系来分析数据路径,即数据的发起沿和捕获沿是最邻近的一对时钟沿,如下图所示。

- 建立时间关系:以第一个发送沿为基准,再向后寻找距此发送沿最近的一个捕获沿,并将两者的setup定为1个周期;

- 保持时间关系:确保当前发送沿推出的数据不被上一个捕获沿给捕获,即hold1(Source clock中的4ns发射的数据不能被Destination clock中的4ns处捕获);确保下一个发送沿推出的数据不被当前捕获沿给捕获,即hold2(Source clock中的8ns发射的数据不能被Destination clock中的8ns处为捕获)。

- 因此previous capture与current launch 构成一组检查;current capture与next launch 构成一组检查。对于两条保持时间的检查,时序报告最终只会给出裕量最小的一条。一旦确定建立时间路径,保持时间路径会自动根据规则做调整。

保持(hold)时间关与建立(setup)时间关系可通过如下公式进行换算:

保持时间时钟周期数=建立时间<path_multiplier>参数 —1 — 保持时间<path_multiplier>参数

由于建立时间的默认<path_multiplier>参数为1,保持时间的默认<path_multiplier>参数为0,则默认的保持时间的时钟周期数就是1-1-0=0.

总结 -end 和 -start 选项如何影响有效的启动和捕获边沿:

| 分析路径 | 源时钟(start) 时钟发射沿移动方向 | 目标时钟(end) 时钟发射沿移动方向 |

| 建立时间 | 向左移动 | 向右移动(默认) |

| 保持时间 | 向右移动(默认) | 向左移动 |

对于源时钟和目标时钟同频同相的时序路径分析,可以不指定-start和-end;对于非同频同相的源时钟和目标时钟,则需要指定-start和-end。set_multicycle_path命令的-setup选项不仅修改建立时间关系,也会影响保持时间关系。如果要将hold关系恢复到原来的位置,则需要使用-hold进行额外的设置。

2.2 同频同相时钟的多周期约束

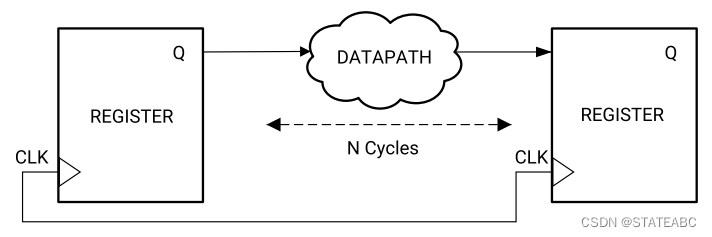

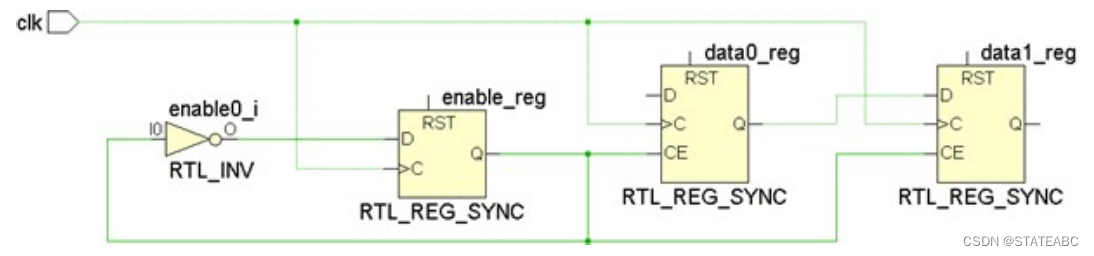

同频同相时希望第一个发送沿推出数据,经过N各周期才被被第二个寄存器的捕获沿给捕获。最常见的就是,时钟使能控制数据捕获的情形。

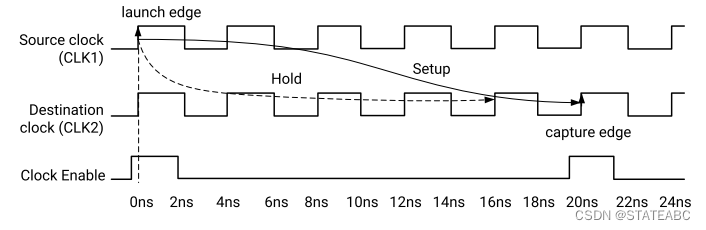

静态时序分析 (STA) 工具解析的默认建立和保持关系如下图

2.2.1 setup=2、hold相应移动

下图表明目标时钟的第一个边沿是无效的,只有目标时钟的第二个边沿将捕获一个新数据,即 将建立时间关系的时钟沿从默认的时钟发射沿后的第一个时钟周期,修改为时钟发射沿后的第二个时钟周期。

set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]当修改建立时间关系时,保持时间关系也会随着发射沿和捕获沿的变化而修改。 将建立检查移至第二个捕获沿后,保持检查会自动移至第一个捕获沿(即建立检查之前的一个时钟周期)。

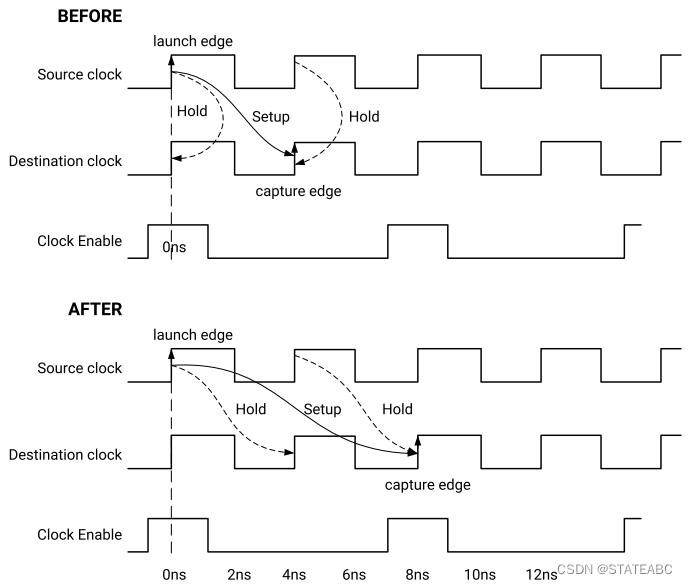

2.2.2 setup=2、hold=1

在上一个例子中进行多周期约束后保持时间的时钟启动沿和捕获沿为了满足一个时钟周期差的关系而随之调整,而实际上保持时间关系通常维持多周期约束前的默认状态即可。为了达到一个时钟周期差的保持时间要求可能会造成过约束,因此可以使用-hold值为1的多周期约束语句将保持时间的捕获时钟调整回默认状态。

set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

2.2.3 setup=5、hold相应移动

将时钟使能信号每5个时钟周期拉高一次,即setup路径乘数被设置为5

set_multicycle_path 5 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

多周期约束后,建立时间的时钟沿从CLK1的第一个时钟周期调整到了第五个时钟周期,保存时间的锁存沿也从CLK2向右移动了4个时钟周期。

2.2.4 setup=5、hold=4

在setup=5、hold相应移动基础上调整保持时间的捕获沿回到默认的与时钟启动沿对齐的位置,同时使用使用-setup、-hold语句:

set_multicycle_path 5 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path 4 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

将hold的值设定为4,保持时间的启动沿和锁存沿又保持对其,由于时钟波形的对称性,这两条多周期约束最终所实现的保持时间关系也等效与下图波形。

因此对于启动时钟和捕获时钟为相同时钟或时钟波形相对固定的情况,如果想要多周期约束后保持时间关系仍然维持默认状态,-setup的多周期约束设定值为N, 则-hold的多周期约束设定值为N-1,即

set_multicycle_path N -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path N-1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

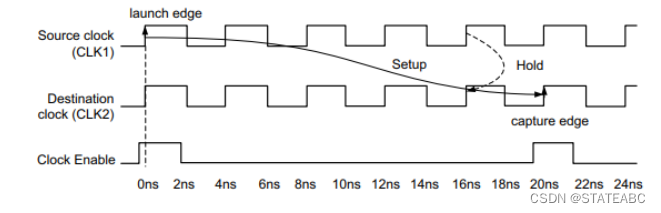

2.3 同频异相时钟的多周期约束

同频异相就是值时序分析中的源时钟和目标时钟的频率相同,但存在一定的相位差。

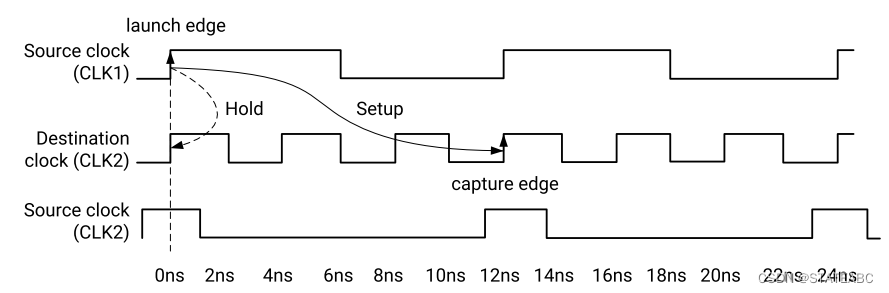

如上图,假设CLK1和CLK2相同频率,CLK2相对CLK1有一定的相移(0.3ns)。在以CLK1为源时钟,CLK2为目标时钟的时序路径分析中,默认情况下时序工具会寻找与CLK1相邻最近的CLK2时钟上升沿,并以CLK1与CLK2相对时间最短(时序要求最高,即最坏情况)的一组时钟沿的时序路径进行分析。

默认情况下时序工具解析的建立时间和保持时间关系如下图,保持时间-3.7ns,建立时间0.3ns。

建立时间无法达到时序收敛,保持时间过于宽松,因此需要进行多周期约束。

set_multicycle_path 2 -setup -from [get_clock CLK1] -to [get_clock CLK2]

2.4 慢时钟域到快时钟域的多周期约束

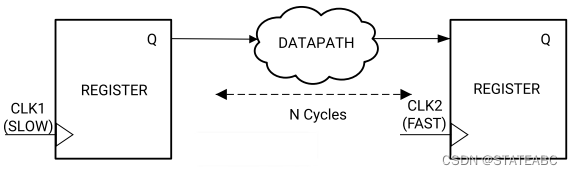

源时钟CLK1是慢时钟,目标时钟CLK2是快时钟。

假设目标时钟CLK2是源时钟CLK1的三倍频,且目的寄存器对应的使能信号每隔3个时钟周期拉高一次,此时的时序约束过紧。

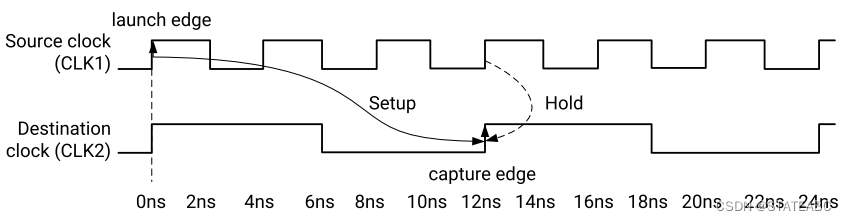

可以设置setup为3个时钟周期,这里的时钟周期移动是相对于目标时钟(快时钟),所以约束必须指定-end。

set_multicycle_path 3 -setup -end -from [get_clock CLK1] -to [get_clock CLK2]多周期约束后的建立时间关系的发射沿和保存时间关系的捕获沿都右移了两个时钟周期。

而实际上保持时间的捕获沿并不需要右移两个时钟周期,这可能会倒是过约束,因此让保持时间的捕获沿退到默认的与时钟启动沿对其的位置。

而实际上保持时间的捕获沿并不需要右移两个时钟周期,这可能会倒是过约束,因此让保持时间的捕获沿退到默认的与时钟启动沿对其的位置。

set_multicycle_path 3 -setup -end -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path 2 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

综上,在慢时钟域到快时钟域且包含时钟使能的多周期约束中,若希望多周期约束后保持时间仍为默认状态,带-setup的多周期约束值设为N时,则带-hold的多周期约束值设为N-1。

set_multicycle_path N -setup -end -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

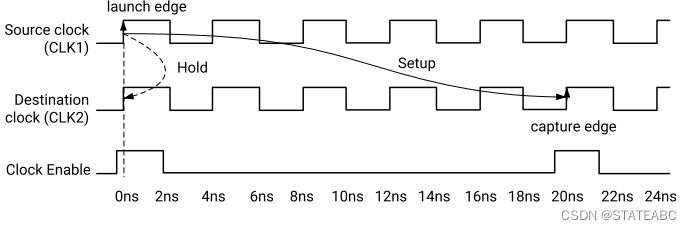

2.5 快时钟域到慢时钟域的多周期约束

源时钟CLK1是快时钟,目标时钟CLK2是慢时钟。

假设目标时钟CLK2是源时钟CLK1的三倍频,且目的寄存器对应的使能信号每隔3个时钟周期拉高一次,此时的时序约束过紧。

进行多周期约束,由于时钟周期移动所针对的是源时钟,因此使用-start选项。

set_multicycle_path 3 -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path 2 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]

综上,在快时钟域到慢时钟域的多周期约束中,若希望多周期约束后保持时间仍为默认状态,带-setup的多周期约束值设为N时,则带-hold的多周期约束值设为N-1。

综上,在快时钟域到慢时钟域的多周期约束中,若希望多周期约束后保持时间仍为默认状态,带-setup的多周期约束值设为N时,则带-hold的多周期约束值设为N-1。

set_multicycle_path N -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]

无论是使用-setup -start还是-setup -end进行约束,都是<path_mutiplier>参数值越大,建立时间关系的时钟启动沿和捕获沿的距离相隔就越远(时序要求更松); <path_mutiplier>参数值越小,建立时间关系的时钟启动沿和捕获沿的距离相隔就越近(时序要求更紧); 使用-hold -start还是-hold -end进行约束与此类似。

三、虚假路径约束

虚假路径指该路径是非功能路径或没有任何时序要求的路径。

虚假路径约束后,时序工具将不再为被约束路径做时序分析;而多周期约束后,时序工具仍会在放宽时序要求的前提下进行时序努力和分析。

虚假路径约束的语法为:

set_false_path [-setup] [-hold] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

- -setup和-hold用于指定约束命令所针对的是路径的建立时间分析还是保持时间分析;

- -from指定约束路径的起始节点<startpoints>,可与to同时指定,若只指定form、to、through的一个则表示覆盖所有经过指定节点的路径都为虚假路径;

- -to指定约束路径的终止节点<endpoints>;

- through指定约束路径所经过的节点<pins|cells|nets>,可选项,可同时使用多个through但有先后顺序。

常见的虚假路径包括:

- 已经做过同步处理的跨时钟域路径;

- 上电后只做一次初始化写入的寄存器路径;

- 复位或测试逻辑的路径;

- 实际不存在的时序路径 。

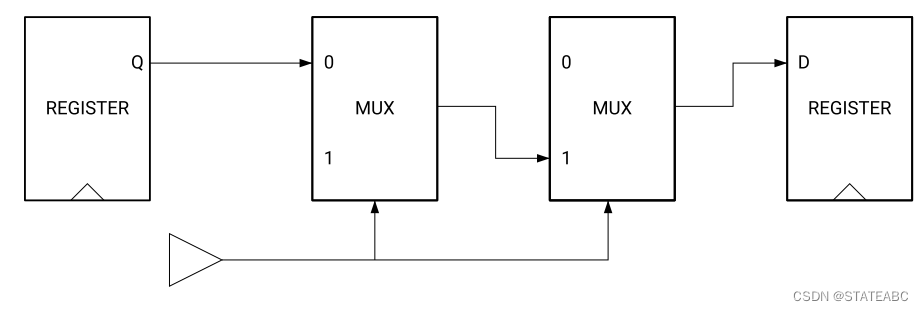

下图为非功能路径,由于两个多路复用器均由相同的选择信号驱动,因此从Q到D的路径不存在,应定义为错误路径。

将覆盖到所有以reset信号起始的路径约束为虚假路径:

set_false_path -from [get_port reset] -to [all_registers]

将两个异步时钟域之间的时序路径约束为虚假路径:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]这个约束仅覆盖从CLKA到CLKB的所有时序路径,但不包含CLKB到CLKA的时序路径,要包含所有的时序路径需要在两个时钟方向都进行约束:

set_false_path -from [get_clocks CLKA] -to [get_clocks CLKB]

set_false_path -from [get_clocks CLKB] -to [get_clocks CLKA]这种情况个更适合用set_clock_groups约束对两个或多个互斥时钟进行约束,以忽略它们之间的时序路径:

set_clock_groups -group CLKA -group -CLKB四、最大/最小延时约束

最大延时约束将覆盖默认的建立时间分析的最大路径延时值;最小延时约束将覆盖默认的保持时间分析的最小路径延时值。

最大延时约束和最小延时约束通常不建议用于约束输入或输出引脚与内部寄存器之间(pin2reg、reg2pin)的路径延时,而对于一些异步信号之间的路径,可以使用最大延时约束和最小延时约束。

最大延时约束和最小延时约束命令如下:

set_max_delay <delay> [-datapath_only] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

set_min_delay <delay> [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

- -from指定约束路径的起始节点<startpoints>

- -to指定约束路径的终止节点<endpoints>

- -through指定约束路径所经过的节点<pins|cells|nets>

默认情况下,时序裕量的计算包含时钟偏斜(Clock Skew)。如果不希望包含时钟偏斜,可以使用-datapath_only选项将其移除。只有set_max_delay命令支持-datapath_only选项,并且需要-from选项。

带或不带 -datapath_only选项 的 set_max_delay 的路径延迟计算的常见行为:

- 当路径在输入端口上启动并且在端口上指定了set_input_delay时,输入延迟将包含在路径延迟计算中;

- 当路径在输出端口上结束并且在端口上指定了set_output_delay时,输出延迟包括在路径延迟计算中;

- 当路径结束于时序单元的数据引脚上时,该数据引脚setup时间包括在该路径延迟计算中。

参考文献:

《FPGA时序约束与分析》

《正点原子FPGA静态时序分析与时序约束》

《Intel Quartus Prime Standard Edition用户指南: Timing Analyzer》

《Vivado Design Suite User Guide: Using Constraints(UG903)》

《Vivado Design Suite 用户指南: 设计分析与收敛技巧 (UG906)》