033 - STM32学习笔记 - TIM定时器(一) - 高级定时器

上节内容学习了基本定时器,其功能比较简单,配置和使用也比较容易,今天在基本定时器的基础上学习一下高级控制定时器的内容。

在F429上一共有两个高级控制定时器和12个通用定时器,这两种定时器实在基本定时器的基础上引入了外部引脚,具有输入捕获和输出比较功能。高级控制定时器比通用定时器增加了可编程死区互补输出、重复计数器以及断路功能,这些功能是针对于工业电机控制方面的。

高级控制定时器时基单元包含一个16位可编程预分频器PSC,预分频器时钟源可选位内部时钟或者外部时钟,同时还有一个8位的重复计数器RCR,可以实现40位可编程定时。

上面说到,在高级控制定时器和通用定时器可以引入外部引脚,器引脚IO分配如下表:

| CH1 | CH1N | CH2 | CH2N | CH3 | CH3N | CH4 | ETR | BKIN | |

|---|---|---|---|---|---|---|---|---|---|

| TIM1 | PA8/PE9/ PC9 | PA7/PE8/ PB13 | PE11/PA9 | PB0/PE10/ PB14 | PE13/PA10 | PB1/PE12/ PB15 | PE14/PA11 | PE7/PA12 | PA6/PE15/ PB12 |

| TIM2 | PA0/PA5/ PA15 | / | PA1/PB3 | / | PA2/PB1 | / | PA3/PB11 | / | / |

| TIM3 | PA6/PC6/ PB4 | / | PA7/PC7/ PB5 | / | PB0/PC8 | / | PB1/PC9 | PD2 | / |

| TIM4 | PD12/PB6 | / | PD13/PB7 | / | PD14/ PB8 | / | PD15/PB9 | PE0 | / |

| TIM5 | PA0/PH10 | / | PA1/PH11 | / | PA2/PH12 | / | PA3/PI0 | PA0/PA5/ PA15 | / |

| TIM8 | PC6/PI5 | PA5/PA7/ PH13 | PC7/PI6 | PB0/PB14/ PH14 | PC8/PI7 | PB1/PB15/ PH15 | PC9/PI2 | PA0/PI3 | PA6/PI4 |

| TIM9 | PE5/PA2 | / | PE6/PA3 | / | / | / | / | / | |

| TIM10 | PF6/PB8 | / | / | / | / | / | / | / | |

| TIM11 | PF7/PB9 | / | / | / | / | / | / | / | |

| TIM12 | PH6/PB14 | / | / | / | / | / | / | / | |

| TIM13 | PF8/PA6 | / | / | / | / | / | / | / | |

| TIM14 | PF9/PA7 | / | / | / | / | / | / | / |

上表中红色为高级控制定时器,绿色为通用定时器,CHx和CHxN是每个通道成对的,假如定时器作用于一个电机控制用,CHx和CHxN用于驱动上下两个Mos管,意味着CHx和CHxN为反相位,作用是为了防止上下Mos管同时导通。而ETR是外部触发输入管教,BKIN是故障信号,用来关闭TIMx的输出。

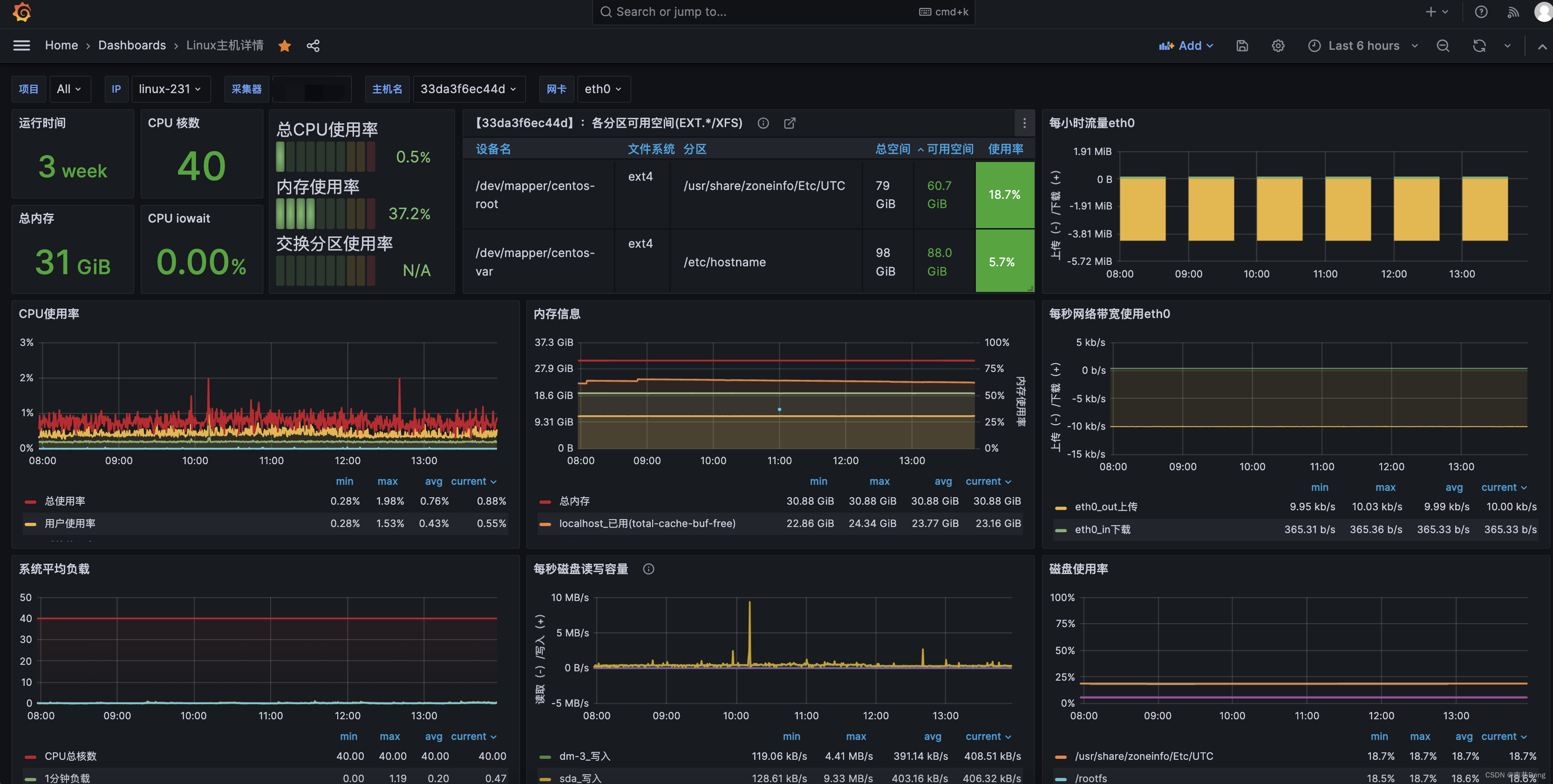

下来再看一下高级控制定时器的功能框图,如下图:

高级控制定时器结构主要分为7个部分,分别为:①时钟源、②控制器、③时基单元、④输入捕获、⑤输出比较、⑥断路功能,在输入捕获与输出比较之间还有一部分为两者公用,这里对于这几个部分逐个学习一下:

1、①时钟源

在高级控制定时器中,共有四个时钟源可选:

- 内部时钟源、

- 外部时钟模式1、

- 外部时钟模式2、

- 内部触发模式(外部触发输入IRTx)

内部时钟源CK_INT:内部时钟源由芯片内部提供,其频率为180MHz,没有特殊需求的情况下,基本都是使用内部时钟,可以通过模式控制寄存器TIMx_SMCR的SMS位控制,此位配置为000时,则使用内部时钟。

外部时钟模式1:

外部时钟模式1共有4个输入通道,分别为T1/2/3/4,由TIM_CCMx的CCxS[1:0]位进行控制,CCM1控制TI1/2,CCM2控制TI3/4。

当外部时钟信号的频率过高或者混杂着高频干扰信号,就需要使用滤波器对ETRP信号重新采样,从而降频或者去除高频干扰,具体由TIMx_CCMRx的ICx_F[3:0]进行配置。

触发信号前,需要进行边沿检测,以确保是上升沿有效还是下降沿有效,其信号来自于前端滤波器的输出,控制位位TIMx_CCER的位CCxP和CCxNP来进行选择。

当使用外部时钟模式1时,触发源有两个,分别位滤波后的FI1FP1(定时器输入1)和FI2FP2(定时器输入2),具体由TIMxSMCR的位TS[2:0]进行控制。

确定触发源信号后,需要将信号连接到TRGI引脚,使得触发信号成为外部时钟模式1的输入,驱动CNT计数,由TIMx_SMCR的SMS[2:0]位控制,选择为000时,为禁止从模式控制器,配置为111时,为外部时钟模式1。

以上内容处理完后,就可以使能计数器进行计数(由TIMx_CR1的位CEN配置),外部时钟模式1的配置完成。

外部时钟模式2:

使用外部时钟模式2时,时钟信号来源于定时器的TIMx_ETR,此引脚有且只有一个。

与外部时钟模式1一样,输入信号可以选择上升沿或下降沿有效,具体通过TIMx_SMCR的ETP位进行配置。

ETRP信号不能超过TIMx_CLK的1/4,即低于45MHz,因此当触发信号超过45MHz时,需要通过分频器进行降频,通过TIMx_SMCR的ETPS[1:0]位进行配置。

分频后,输入的ETRP信号可能存在频率较高或者高频干扰,需要通过滤波器对其进行重新采样,由TIMx_SMCR的ETF[3:0]进行控制,其中fDTS由内部时钟CK_INT分频而来,通过TIMx_CR1的CKD[1:0]进行控制。

与外部模式寄存器1的配置相同,如果选择从模式,这里则需要将触发信号换成ETRF输入,最终输出CK_PSC,再通过计数器CNT计数,具体配置TIMx_SMCR的ECE设置位1,选择为外部时钟模式2。

以上配置完成后,通过TIMx_CR1的CEN位使能计数器开始工作。

内部触发输入:

这里我查看了一下STM32F4xx中文参考手册,发现官方的参考手册上对此部分描述为外部触发输入IRTx,野火的教程中为什么叫内部触发输入我猜大概是因为此时钟源模式是输入时使用一个定时器作为另一个定时器的预分频器。硬件上高级控制定时器和通用定时器在内部相连,可实现定时器同步或者级联。两个定时器一个作为主模式定时器,另外一个作为从模式定时器,主模式定时器可以对从模式定时器进行复位、启动、停止、提供时钟的控制,高级控制定时器和部分通用定时器(TIM2~TIM5)可设置为主模式或者从模式,TIM9和TIM10可设置从模式。如下图中,就是将TIM1作为TIM2的预分频器。

在TIM1中,,将TIM1配置为主模式,此时每次发生更新事件UEV时,都会输出一个周期性触发信号,在TIM1_CR2寄存器中写入MMS=010(MMS为主模式选择,010为更新,选择更新事件作为触发输出,具体参见官方参考手册),那么每次更新事件时,TRGO1都会输出上升沿。

此时需要将TRGO1连接到TIM2,并且TIM2需要配置为从模式,选择使用ITR0作为内部触发,在TIM2_SMCR寄存器中将TS位配置为000。将TIM2模式控制器设置为外部时钟1模式(TIM2_SMCR寄存器SMS配置为111)。

在以上配置完成后,需要将TIM1和TIM2的TIMx_CR1寄存器的CEN位置1,以同时使能这两个定时器。除了将两个定时器的CEN位置1外,还可以使用一个定时器来使能另外一个定时器,这个等学习到了在进行梳理。

2、②控制器

在高级控制定时器中,控制器部分包括触发控制器、从模式控制器以及编码器接口。触发控制器用来针对片内外设输出控制信号,比如为其他定时器提供时钟和触发DAC/ADC转换等功能。编码器接口是专门针对编码器计数而设计。从模式控制器可控制计数器复位、启动、递增/递减以及计数。

3、③时基单元

时基单元主要空能包括如下:

计时功能:可以通过对输入的脉冲信号进行计数,从而测量时间间隔或者脉冲宽度,通过调整预分频系数和计数器的预设值实现对不同时间间隔或脉冲宽度的精准测量。

定时功能:用于产生定时信号或者定时中断,通过设置预分频系数和计数器的预设值,可以确定定时信号的周期或者中断请求的时间间隔。

延时功能:时基单元可以用于产生延时信号或者延时中断。将输入脉冲信号作为触发条件,可以设置一定时间的延迟,从而使输出信号或者中断请求在输入脉冲信号产生之后的一定时间后再产生。

时基单元主要包括四个寄存器,分别为:

- 计数器寄存器CNT

- 预分频器寄存器PSC

- 自动重载寄存器ARR

- 重复计数器寄存器RCR

以上四个寄存器中,重复计数器寄存器RCR是高级定时器独有,通用定时器和基本定时器没有,另外三个寄存器为16位有效,而RCR寄存器为8位有效。

计数器寄存器CNT

高级控制定时器的计数器有三种计数模式,分别位递增计数模式、递减计数模式和中心对齐(递增/递减)计数模式。

- 递增计数模式下,计数器从0开始计数,每产生一个CK_CNT脉冲,计数器就累加1,当计数器值与自动重载计数器ARR值相等,计数器重复从0开始计数,并且会生成计数器上溢事件,计数器依次循环计数。如果禁用重复计数器,每次计数器生成上溢事件时,都会马上生成更新事件UEV;如果使能重复计数器,那么每生成一次上溢事件,重复计数器内容就减1,当重复计数器内容减到0时,则会生成更新事件。

- 递减计数模式下,基本与递增计数模式类似,只不过计数开始是由自动重载寄存器ARR的值开始递减,计数器值为0时产生一次下溢事件。重复计数器作用也一样,区别在于递增使用上溢事件,而递减使用下溢事件。

- 中心对齐模式下,计数器从0开始递增计数,直到计数器值等于ARR-1时,生成计数器上溢事件,然后再从ARR值开始递减计数,直到递减到1时,生成计数器下溢事件。然后再从0开始,依次往复,每次发生计数器上溢和下溢事件时,都会发生更新事件。

预分频器寄存器PSC

预分频器寄存器有一个输入时钟CK_PSC,来源于时钟源的输出。输出时钟CK_CNT,用来驱动计数器CNT计数,通过设置预分频器PSC的值可以得到不同的CK_CNT值,计算公式如下:

f

C

K

_

C

N

T

=

f

C

K

_

P

S

C

/

(

P

S

C

[

15

:

0

]

+

1

)

f_{CK\_CNT} = f_{CK\_PSC}/(PSC[15:0]+1)

fCK_CNT=fCK_PSC/(PSC[15:0]+1)

自动重载寄存器ARR

自动重载寄存器ARR在基本定时器中已经说过了,这里简单回顾一下,自动重载寄存器用来存放与计数器CNT比较的值,如果两个值相等就递减重复寄存器。通过TIMx_CR1寄存器的ARPE位控制自动重载影子寄存器,如果ARPE位置置1,那么自动重载影子寄存器有效,当事件更新的时候,才会把TIMx_ARR的值赋给影子寄存器,如果ARPE为0,则修改TIMx_ARR的值马上生效。

重复计数器RCR

在基本/通用定时器发生上/下溢事件时,会直接生成更新事件,但是高级控制定时器因为硬件结构上多出了重复计数器,在定时器发生上/下溢事件时,只是递减重复计数器的值,当重复计数器为0时,才会生成更新事件,而具体产生多少个上/下溢事件才会产生更新事件,取决于RCR(N+1)的值。

4、④输入捕获

输入捕获是对输入的信号上升沿、下降沿或者上升/下降沿进行捕获,常用于测量输入信号的额脉宽和测量PWM输入信号的频率及占空比。原理是当捕获到的信号的边沿变化时,把计数器CNT的值所存到捕获寄存器CCR中,把前后两次捕获到的CCR寄存器中的值相减,可以计算出脉宽或者频率。如果捕获的脉宽事件长度超出预设的捕获定时器的周期,则会产生溢出,此时就需要特殊处理一下。

输入通道

输入通道时需要测量的信号进入的外部引脚,即上图中的TIMx_CH1/2/3/4,后面我们简称为TI1/2/3/4。

输入滤波和边沿检测器

输入滤波是为了滤除输入信号的高频干扰,即为重新采样。采样时,采样的频率必须大于等于两倍的输入信号,例如,输入信号为1M时,可能存在高频的信号干扰,为了滤除干扰,就需要将采样频率设置为2M,这样就可以把高于2M的高频干扰过滤掉,同时又能保证有效信号的采集。滤波器的配置通过CR1寄存器的CKD[1:0]和CCMR1/2的位ICxF[3:0]控制,可以看一下ICxF的描述:

可以看到采样频率fSAMPLE由fCK_INT或者fDTS分频后的时钟提供,fCK_INT是内部时钟,fDTS是通过fCK_INT进行分频后得到的频率,分频因子可以通过CKD[1:0]决定,可以选择不分频、2分频或者4分频。

边沿检测用来确定信号捕获的边沿状态,可以为上升沿、下降沿或者上升/下降沿。通过CCER寄存器的CCxP和CCxNP进行配置。

捕获通道

捕获通道是图中的IC1/2/3/4,每个捕获通道都有对应的捕获寄存器CCR1/2/3/4,当发生捕获时,计数器CNT的值会所存到捕获寄存器中。

捕获通道和输入通道的区别在于,输入通道用于接收输入信号,而捕获通道则用来捕获输入信号的通道,一个输入通道的信号可以同时经由两个捕获通道输入,例如,输入通道TI1的信号经过滤波边沿检测器后,TI1FP1和TI1FP2可以输入到捕获通道IC1和IC2。后面在学习到PWM时会用到这块的知识。

预分频器

这里的预分频器与上面讲的预分频器是两回事,这里的预分频器,用于决定发生多少个事件时进行依次捕获,通过寄存器CCMRx的ICxPSC进行配置,如果想捕获信号的每个边沿,则不需要分频。

捕获寄存器

经过预分频器的信号ICxPS是最终的捕获信号,当发生首次捕获时,计数器的值CNT会被锁存到捕获寄存器CCR中,同时产生CCxI中断,对应的SR寄存器的中断位CCxIF会被置位,通过软件或者读取CCR中的值可以将CCxIF清0。当发生第二次捕获时(重复捕获),CCR寄存器中在第一次捕获到计数器值,且CCxIF标志已经置1了,此时重复捕获后溢出标志位CCxOF会被置位,并且CCxOF只能通过软件清零。

5、⑤输出比较

输出比较是通过定时器的外部引脚对外输出控制信号,共有8种模式,通过CCMRx的OCxM[2:0]进行配置:

- 冻结

- 将通道1/2/3/4设置为匹配时输出有效电平

- 将通道1/2/3/4设置为匹配时输出无效电平

- 翻转

- 强制变为无效电平

- 强制变为有效电平

- PWM1

- PWM2

比较寄存器:

当计数器CNT与比较寄存器CCR的值对比相等时,输出参考信号OCxREF的信号极性会发生改变,当OCxREF=1(高电平,有效电平)时,OCxREF=0(低电平,无效电平),并且会产生比较中断CCxI,相应的标志位CCxIF会置位,然后OCxREF经过控制后会输出信号OCx/OCxN。

死区发生器:

死区(Dead Time)是为了保护电路并且确保电机控制的平稳运行的延迟时间,在上半桥关断后,延迟一段时间再打开下班桥,或者下班桥关断后,延迟一段时间再打开上班桥,避免上下班桥同时打开造成功率原件烧毁。在死区时,上下半桥状态均为关断状态。

再生成参考波形OCxREF的基础上,可以插入死区时间,用于生成两路互补的输出信号OCx和OCxN,死区时间的大小通过BDTR的DTG[7:0]配置,其大小必须根据输出信号相连接的期间及其特性进行调整,如以下半桥驱动电路:

在此电路中有两个MOS管Q1、Q2,Q1导通,Q2截止,如果想让Q1截止,Q2导通,就需要先关闭Q1,延迟一段时间后,再导通Q2,否则可能会出现Q1未关断时,Q2就打开,导致MOS管烧毁,这段延迟时间就是死区时间。而这个死区时间取决于Q1从导通到完全关断的时间,主要取决与MOS管的工艺,相关数据可以根据MOS管的数据手册确定。

输出控制:

输出比较的输出控制中,参考信号OCxREF再经过死区发生器后,会产生两路带死区的互补信号OCx_DT和OCxN_DT(通道1~3有互补信号,通道4没有)这两路带死区的互补信号随后就进入输出控制电路,如果没有加入死区控制,那么进入输出控制电路的信号就是OCxREF。

进入输出控制电路的信号会被分成两路,一路原始信号,一路反向信号,具体由寄存器CCER的CCxP和CCxNP控制。通过极性选择的信号是否由OCx引脚输出到外部引脚CHx/CHxN取决于寄存器CCER的CxE和CxNE配置。

如果假如断路功能,则断路和死区寄存器BDTR的MOE、OSSI和OSSR这三个位会共同影响输出的信号。

输出引脚:

输出比较的输出信号最终是通过定时器的外部IO来输出,分别为CH1/2/3/4,前三个通道还有互补的输出通道CH1/2/3N。

6、⑥断路功能

上面提到的断路功能,指的是电机控制的刹车功能,当时能断路功能时,根据相关控制位状态修改输出信号电平。在任何情况下OCx和OCxN输出都不能同时为有效电平,这关系导电剂控制常用的H桥电路结构。

断路源可以是时钟故障事件,由内部复位时钟控制器的时钟安全系统CCS生成,也可以是外部断路输入IO,两者是或运算关系。

系统复位启动都是默认关闭断路功能,将断路和死区寄存器TIMx_BDTR的BKE置1,使能断路功能,可通过TIMx_BDTR寄存器的BKP位设置断路输入引脚的有效电平,设置位1时输入BRK位高电平有效,否则低电平有效。

当发送断路时,会产生效果:

- TIMx_BDTR 寄存器中主输出模式使能(MOE)位被清零,输出处于无效、空闲或复位状态;

- 根据相关控制位状态控制输出通道引脚电平;当使能通道互补输出时,会根据情况自动控制输出通道电平;

- 将 TIMx_SR 寄存器中的 BIF 位置 1,并可产生中断和 DMA 传输请求。

- 如果 TIMx_BDTR 寄存器中的 自动输出使能(AOE)位置 1,则 MOE 位会在发生下一个 UEV 事件时自动再次置 1。

OK,关于高级控制定时器的内容今天就先学习到这里,最近这段时间工作比较忙,每天回来只能总结一点,后面尽可能提高点速度。本节内容较多,各位学习过程中如果发现总结内容有疏漏或者错误的地方,欢迎指出,大家一起进步!