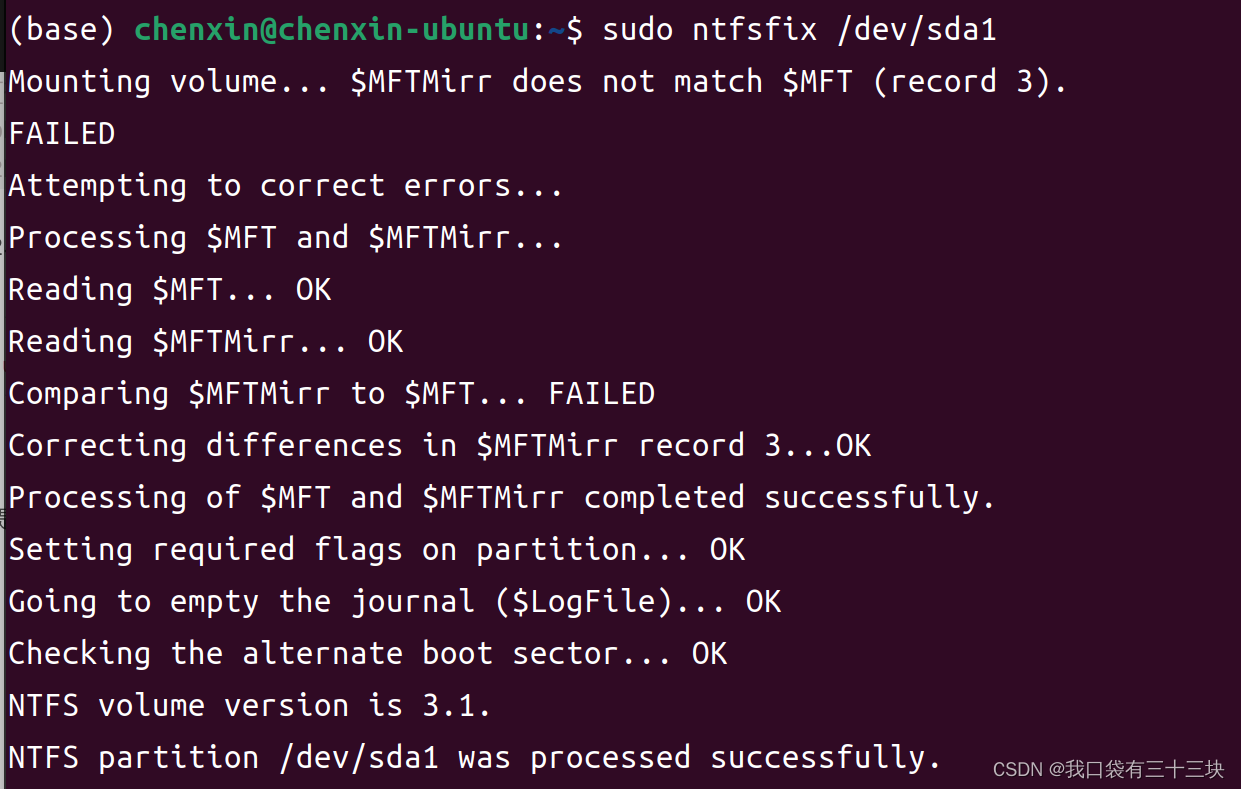

接前一篇文章:《PCI Express体系结构导读》随记 —— 第I篇 第2章 PCI总线的桥与配置(5)

2.2 HOST主桥

本节以MPC8548处理器为例,说明HOST主桥在PowerPC处理器中的实现机制,并简要介绍x86处理器系统使用的HOST主桥。

MPC8548是基于Freescale(飞思卡尔)的PowerPC架构的PowerQuicc III处理器,同时兼容MPC8548E,MPC8547E、MPC8545E、MPC8543E系列处理器,其强大的处理能力特别适合于高速低时延的处理。

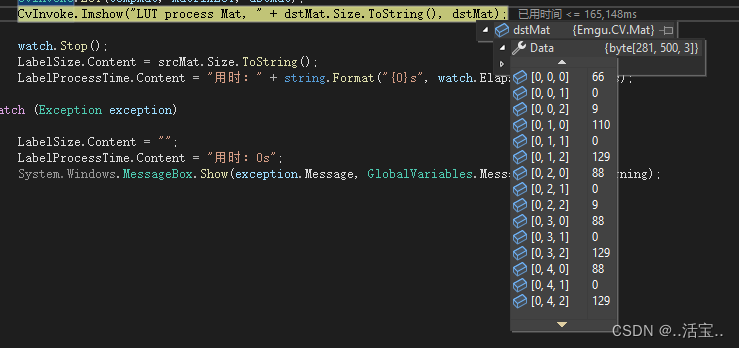

MPC8548处理器基于E500 V2内核,在其中集成了DDR控制器、多个eTSEC(Enhanced Three-Speed Ethernet Controller)、PCI/PCI-X和PCIe总线控制器等一系列接口。

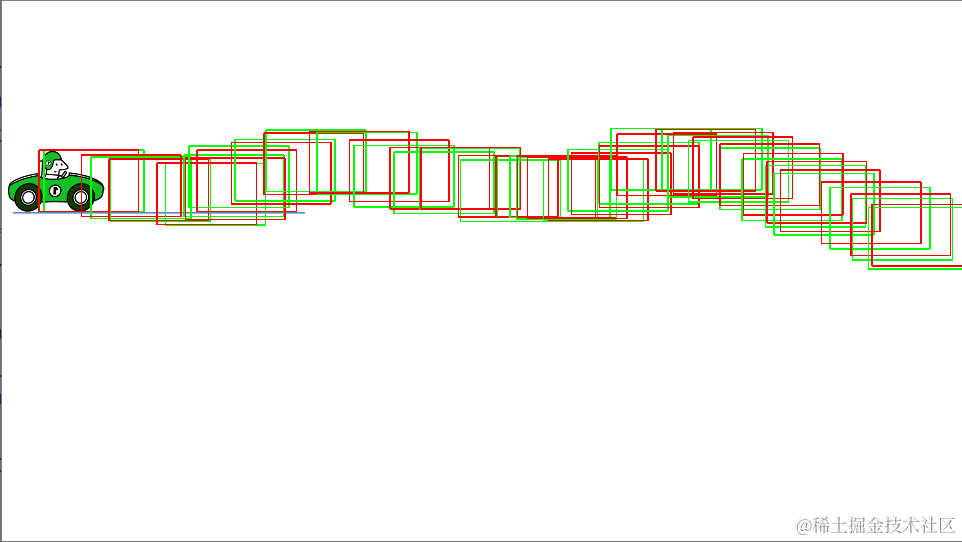

MPC8548处理器的拓扑结构如图2-2所示:

由上图可见,MPC8548处理器的L1 Cache在E500 V2内核中,而L2 Cache与FSB(MPC8548也将FSB称为CCB,即Core Complex Bus)直接相连,并不属于E500内核。值得注意的是,有些高端PowerPC处理器的L2 Cache也在CPU中,而L3 Cache与CCB总线直接相连。

在MPC8548处理器中,所有外部设备,如以太网控制器、DDR控制器和OCeaN连接的总线控制器都与SoC平台总线直接连接。而SoC平台总线通过Cache共享一致性模块与FSB连接。

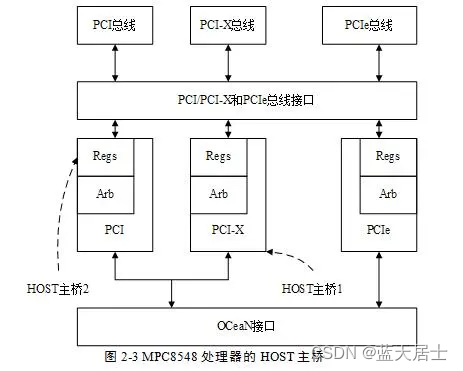

在MPC8548处理器中,具有一个32位的PCI总线控制器、一个64位的PCI/PCI-X总线控制器,还有多个PCIe总线控制器。MPC8548处理器使用OCeaN连接这些PCI、PCI-X和PCIe总线控制器。在MPC8548处理器系统中,PCI设备进行DMA操作时,首先通过OCeaN,之后经过SoC平台总线到达DDR控制器。

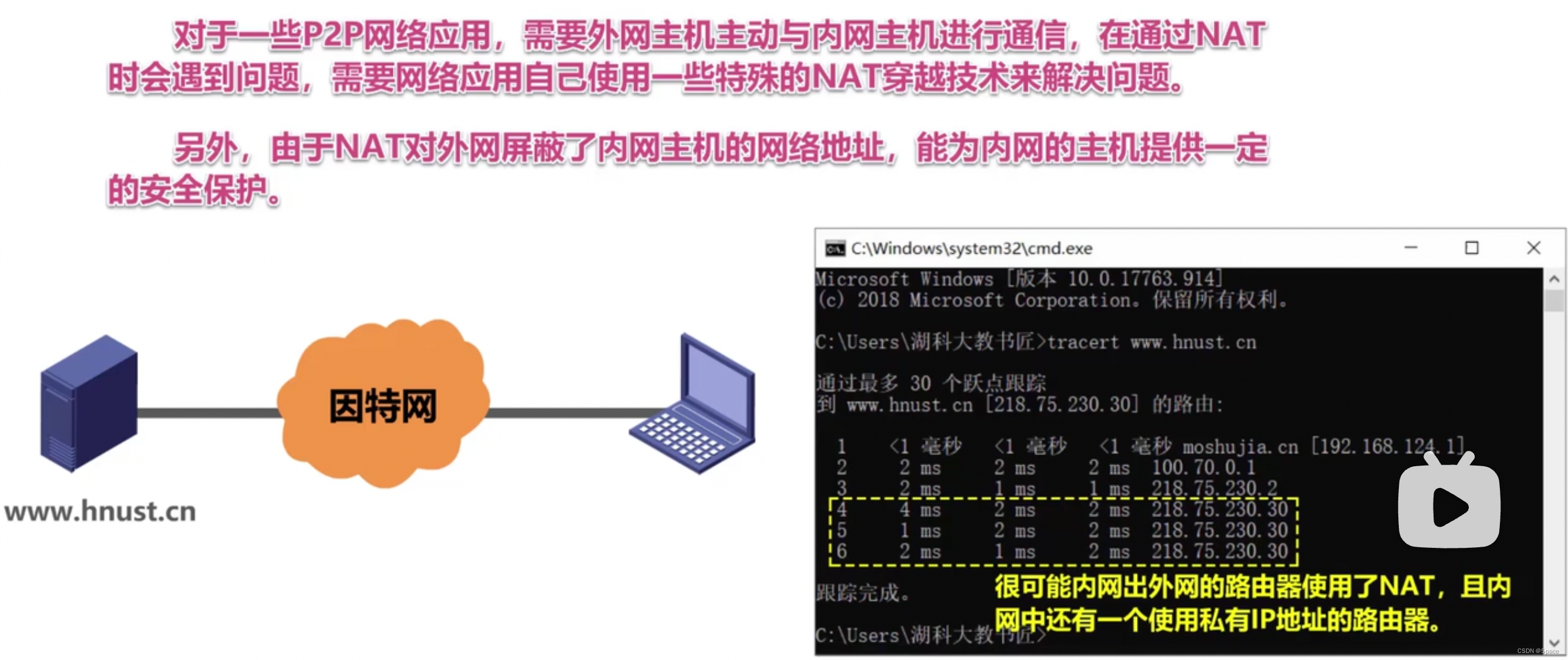

OCeaN是MPC8548处理器中连接快速外设使用的交叉互连总线,不仅可以连接PCI、PCI-X和PCIe总线控制器,而且可以连接RapidIO总线控制器。使用OCeaN进行互连的总线控制器可以直接通信,而不需要通过SoC平台总线。如来自HOST主桥1的数据报文可以通过OCeaN直接发向HOST主桥2,而不需要将数据通过SoC平台总线再进行转发,从而减轻了SoC平台总线的负担。

OCeaN部件的拓扑结构如图2-3所示。

在MPC8548处理器中,有两个HOST主桥,分别是HOST主桥1和HOST主桥2。其中,HOST主桥1可以支持PCI-X总线,而HOST主桥2只能支持PCI总线。此外,该处理器还含有多个PCIe总线控制器。

本节仅介绍HOST主桥,即MPC8548处理中的PCI总线控制器,而不介绍该处理器的PCIe总线控制器。因为从软件层面上看,MPC8548处理器的PCIe总线控制器与PCI/PCI-X总线控制器功能类似。

MPC8548处理器既可以作为PCI总线的HOST处理器,也可以作为PCI总线的从设备。本节仅讲述MPC8548处理器如何作为PCI总线的HOST处理器管理PCI总线树,而并不关心MPC8548处理器作为从设备的情况。

在MPC8548处理器的HOST主桥中,定义了一系列与系统软件相关的寄存器。本节将通过介绍这些寄存器,说明此HOST主桥的功能。囿于篇幅,本节仅介绍HOST主桥1相关的寄存器,HOST主桥2使用的寄存器与HOST主桥1使用的寄存器类似。

更多内容请看下回。