目录

MOS管:

CMOS组成的常见门电路

反相器(非门):

与非门 或非门

OD门

三态门

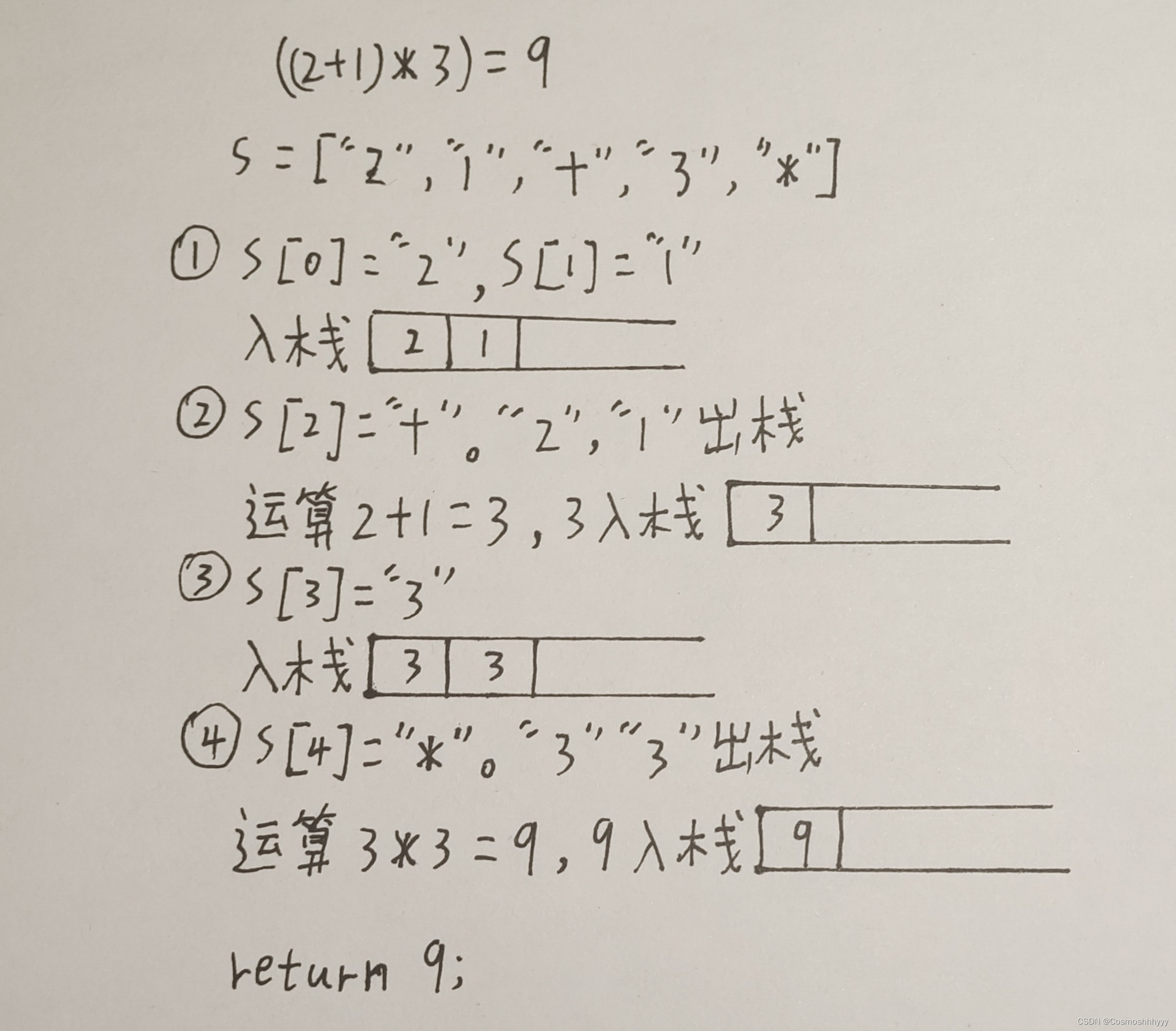

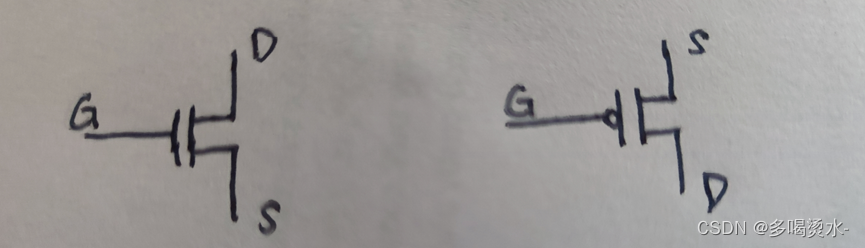

MOS管简介:

> NMOS: 漏极(D)入,源极(S)出,栅极(G)加正电压导通

> PMOS:源极入漏极出,加低电压导通

NMOS(左) PMOS(右)

详细知识看这个链接:

半导体器件(三) 场效应管 FET_多喝烫水-的博客-CSDN博客_fet场效应管

CMOS组成的常见门电路

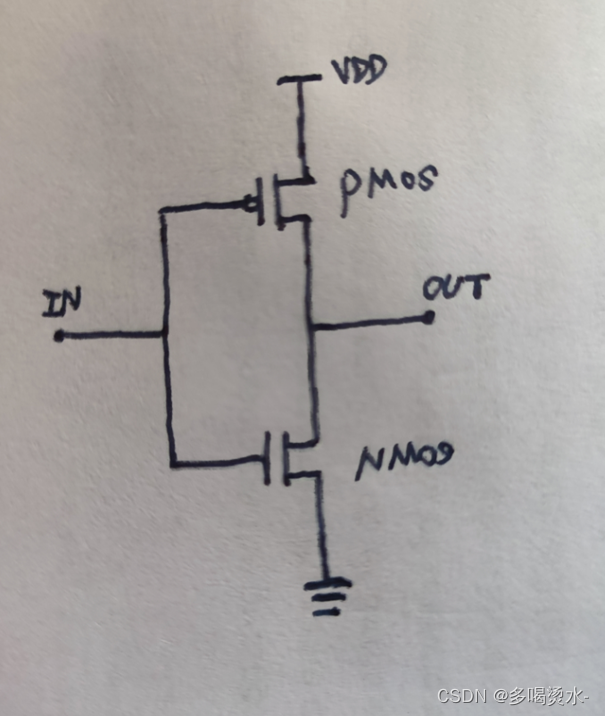

反相器(非门):

非门的设计思路:上下拉逻辑,上拉用PMOS,下拉用NMOS

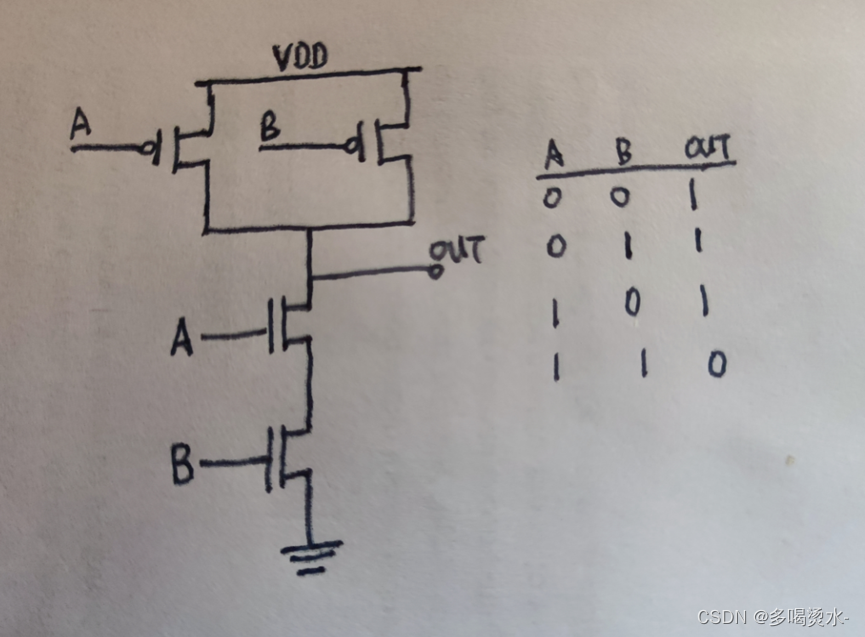

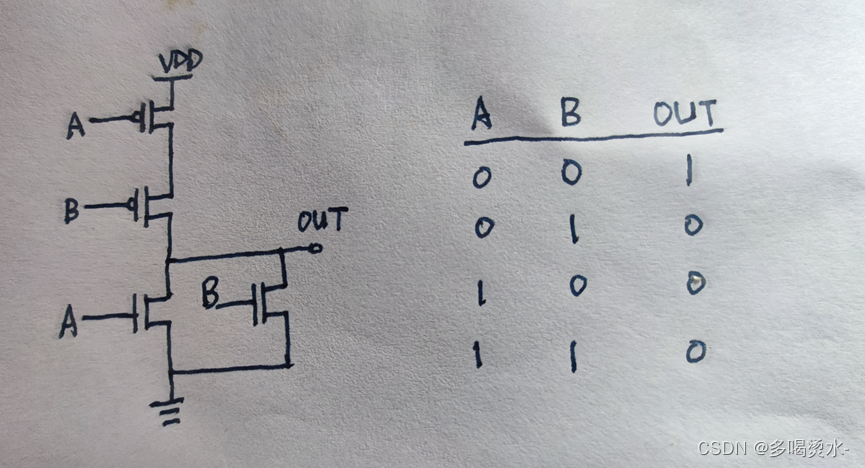

与非门 或非门

不管是与非门还是或非门,只要是非门的设计就一定有PMOS上拉,NMOS下拉,与非就是PMOS并联,或非就是Pmos串联

与非门(左)或非门(右)

OD门

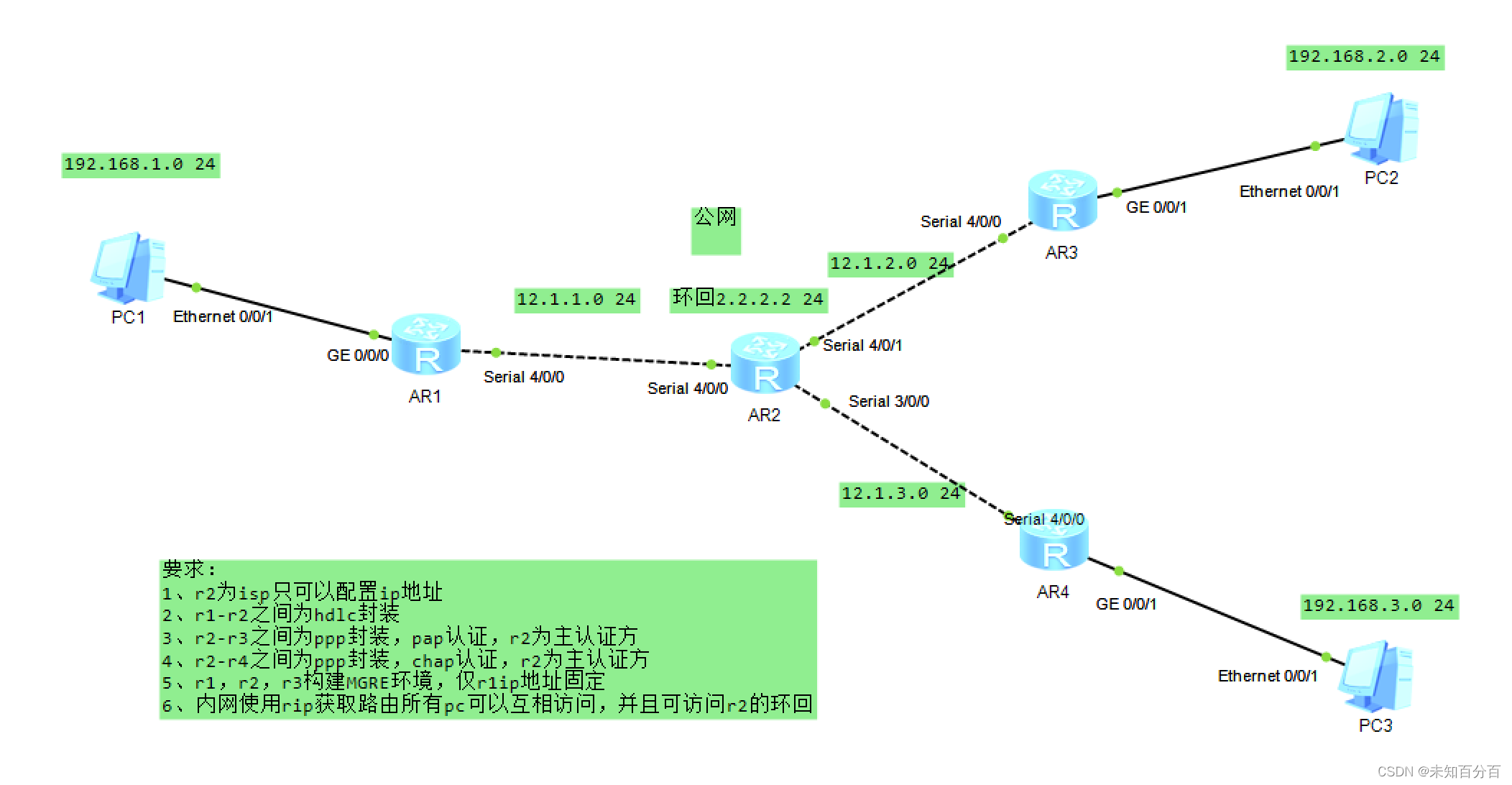

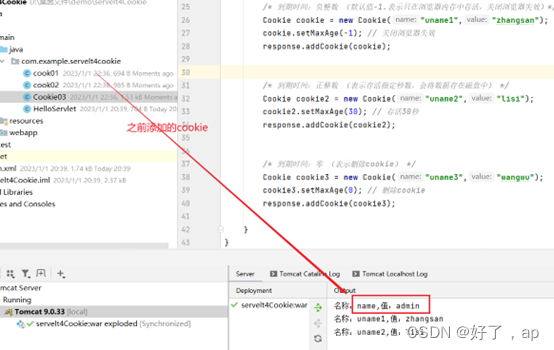

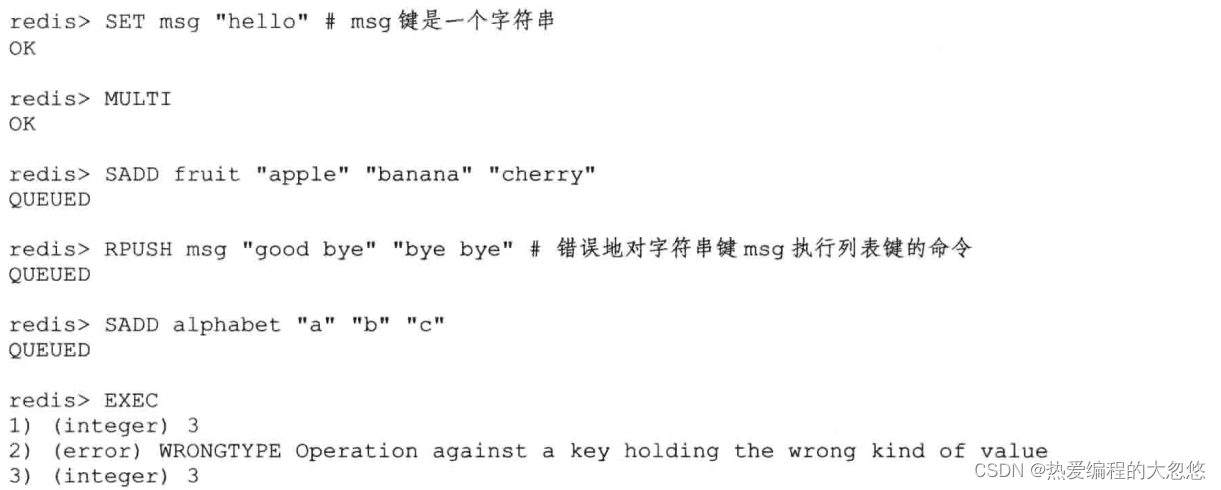

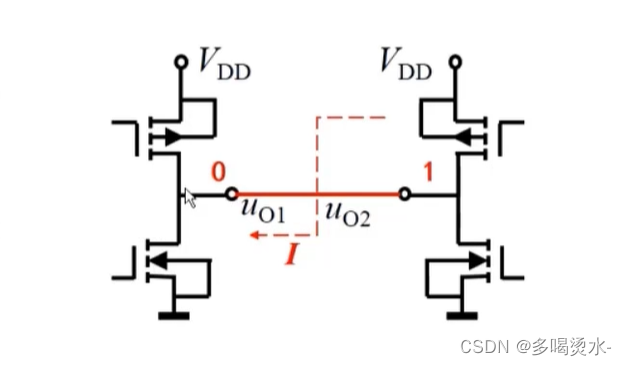

OD(Open Drain)门又叫漏极开路门,主要针对的是MOS管(从上往下依次是漏极、栅极、源极)线与逻辑指的是两个输出端直接互联就可以实现“AND”的功能,如下图

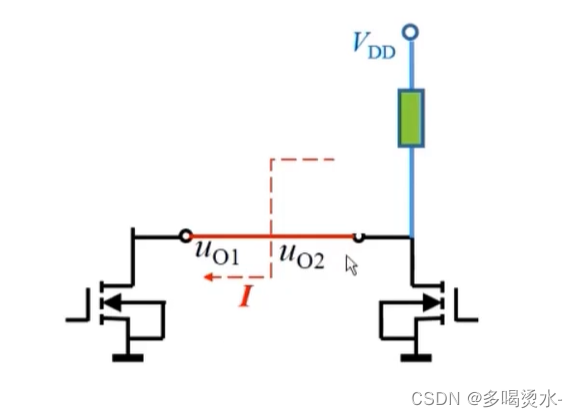

如果按照该图的做法直接互联的话,会导致形成阻值低的通道,产生大电流,电路会出现问题的

那么这个时候就用到了OD门

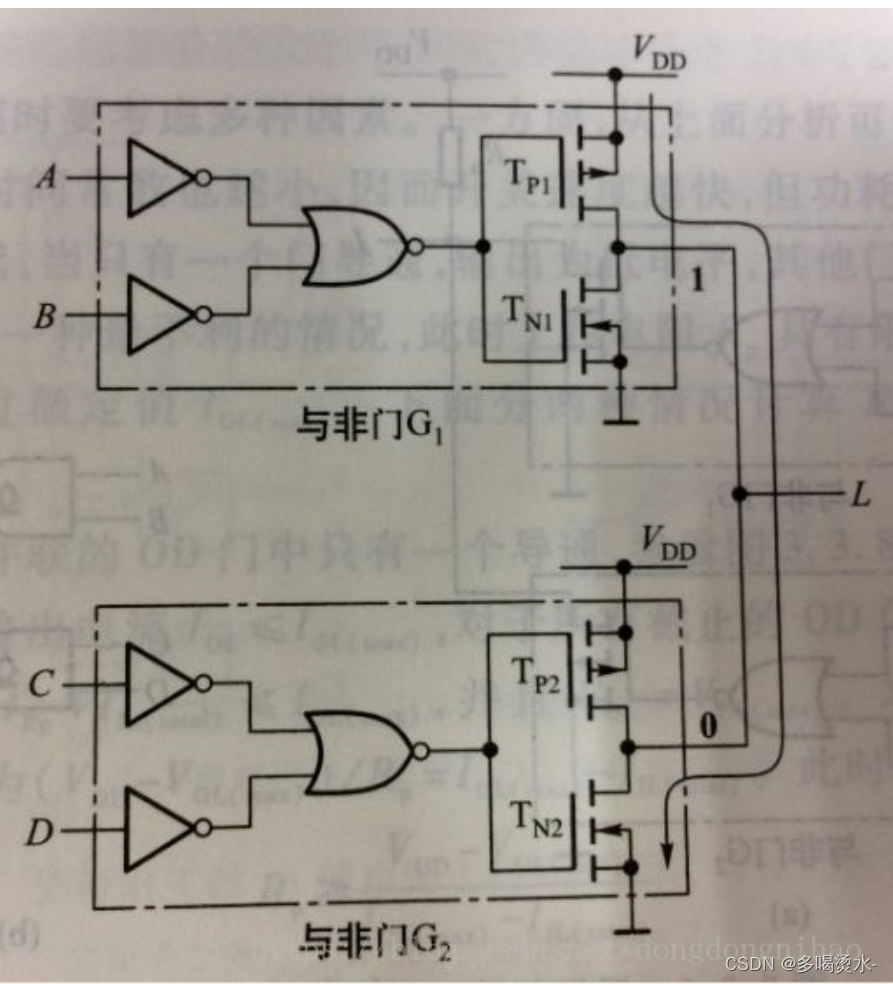

通常CMOS门电路都有反相器作为输出缓冲电路,如上图所示,如果将两个CMOS与非门G1和G2的输出端连接在一起,并设G1的输出处于高电平,TN1截止,TP1导通;而G2的输出处于低电平,TN2导通,TP2截止,这样从G1的TP1端到G2的TN2端将形成一低阻通路,从而产生很大的电流,很有可能导致器件的损毁。

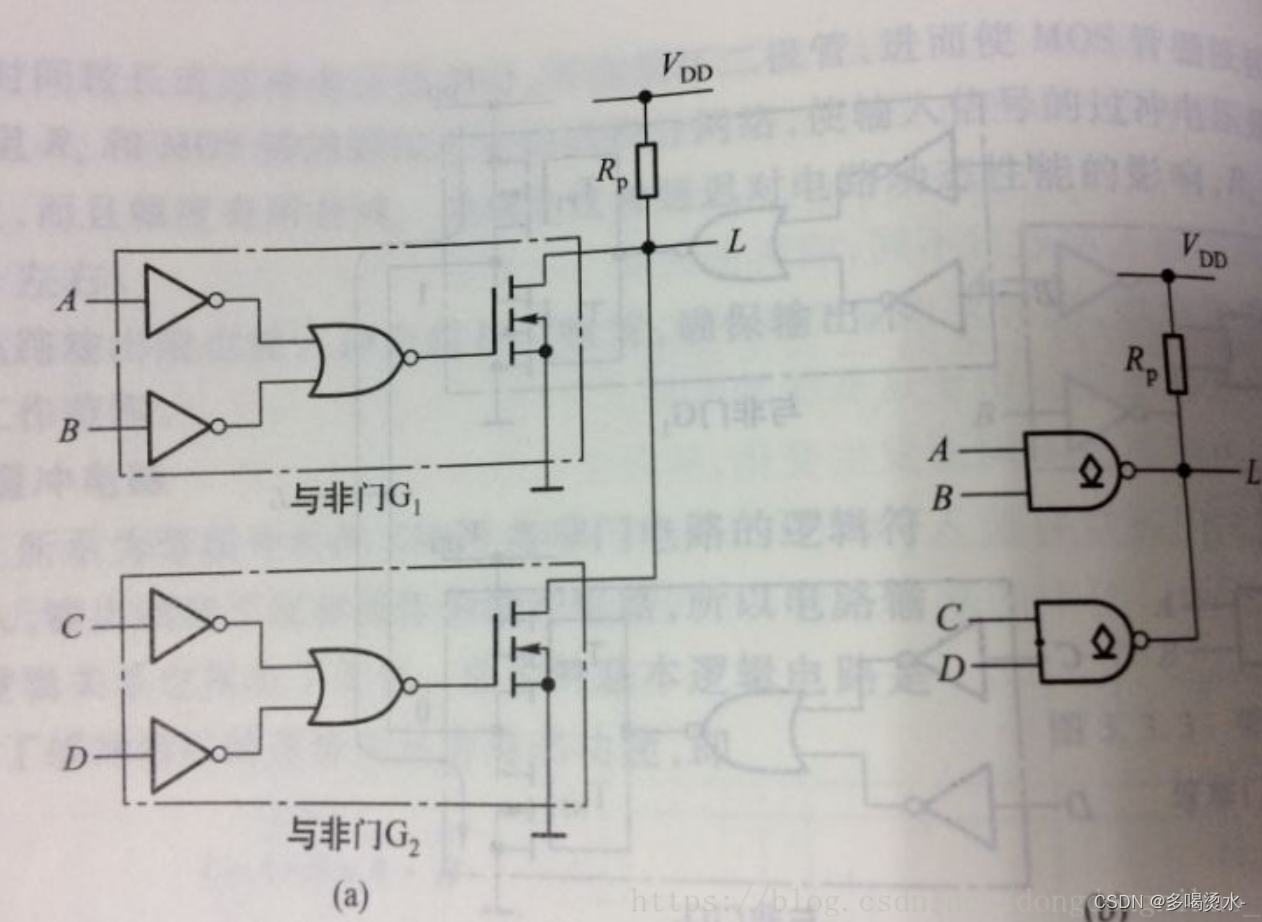

那么,我们就需要寻找一种新的方式实现线与逻辑,即OD门。所谓漏极开路门(OD门)是指CMOS门电路的输出只有NMOS管,并且它的漏极是开路的。使用OD门时必须在漏极和电源VDD之间外接一个上拉电阻(pull-up resister)RP。如图2所示为两个OD与非门实现线与,将两个门电路输出端接在一起,通过上拉电阻接电源。

可以看出,OD门就是将反相器的上面的pmos管拿掉了而已。

当两个与非门的输出全为1时,输出为1;只要其中一个输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)'(CD)'。

线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。

用OD门就可以实现总线的功能,2个门电路可以直接相连

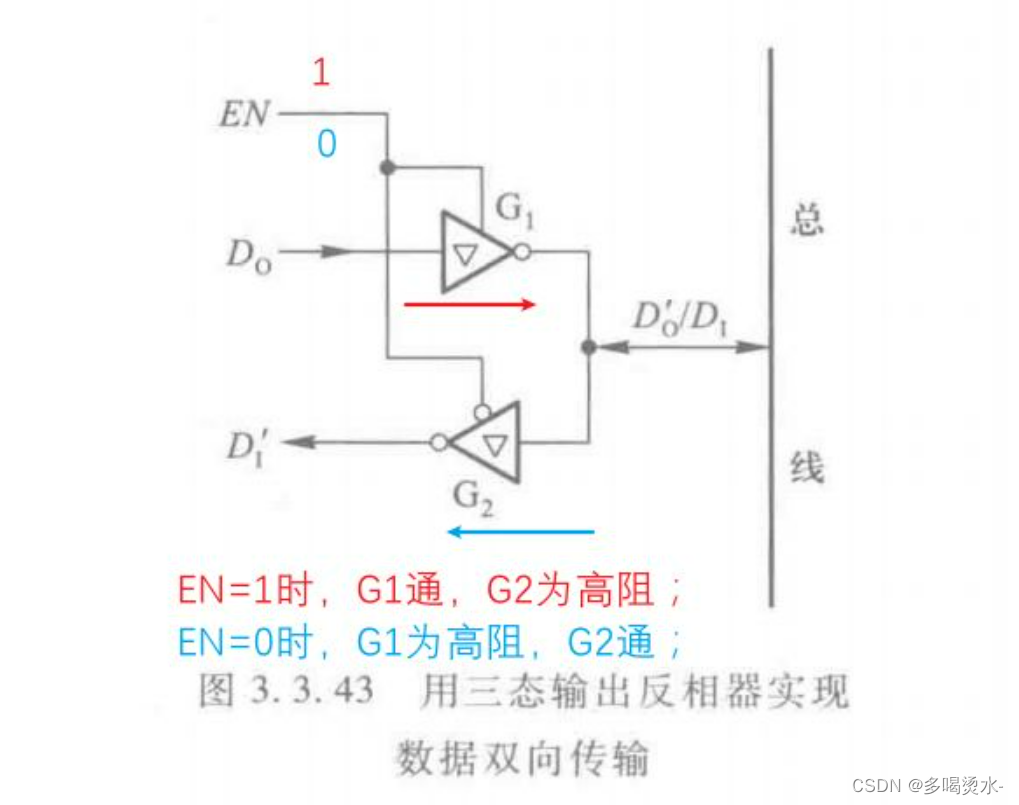

三态门

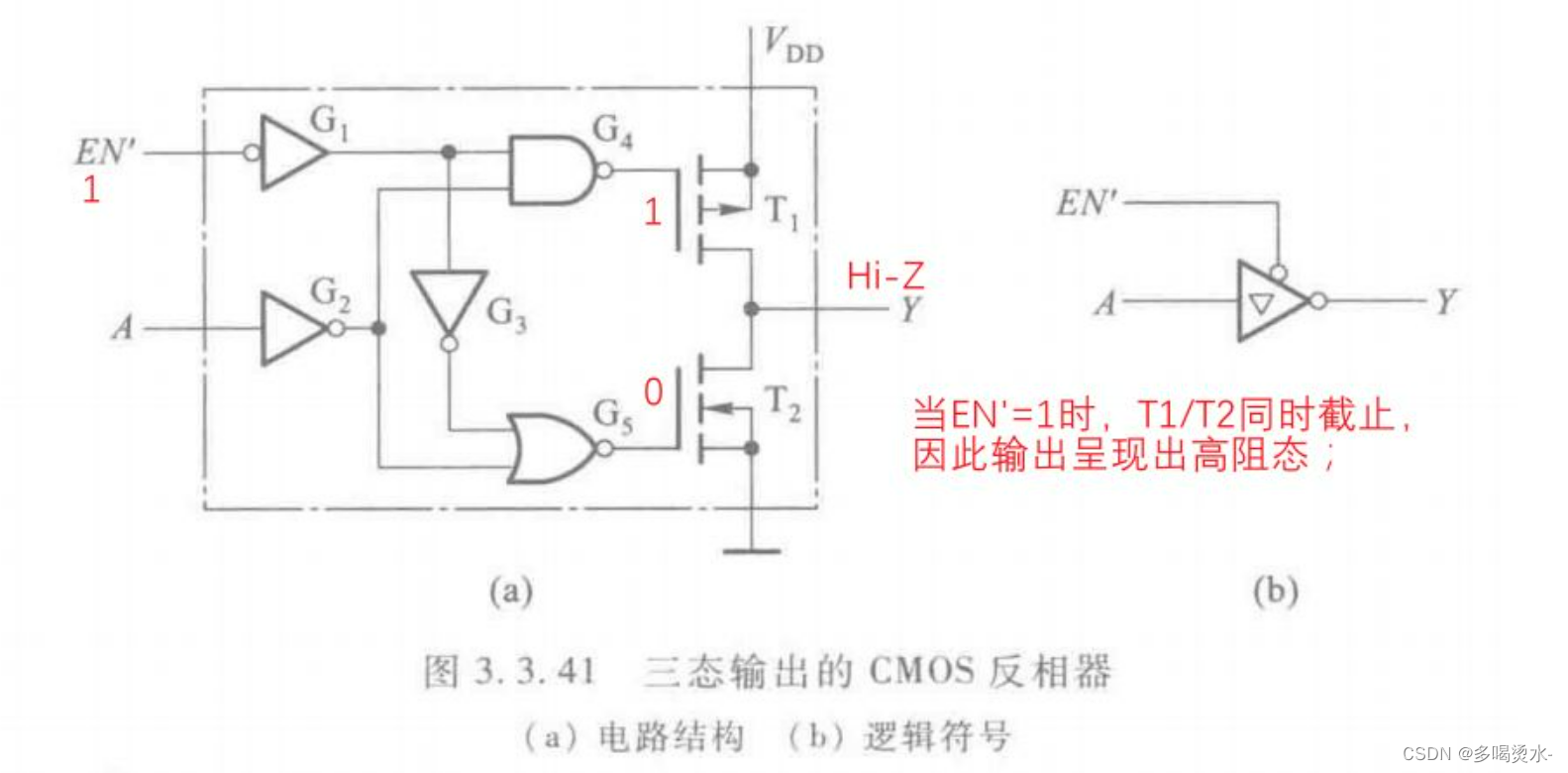

三态门输出电路除了有高低电平两个状态之外,还有第三个状态--Hi-Z高阻态;

在verilog我们使用inout的端口时,常常会使用这样的语句:assing out = en ? out_tmp : 1'bz;其含义是当en=1时,输出接口输出具体电平out_tmp,en=0时则当作输入接口使用,赋值为Hi-Z态,允许外部信号的拉低或者拉高;