【一】FPGA实现SPI协议之SPI协议介绍

一、spi协议解析

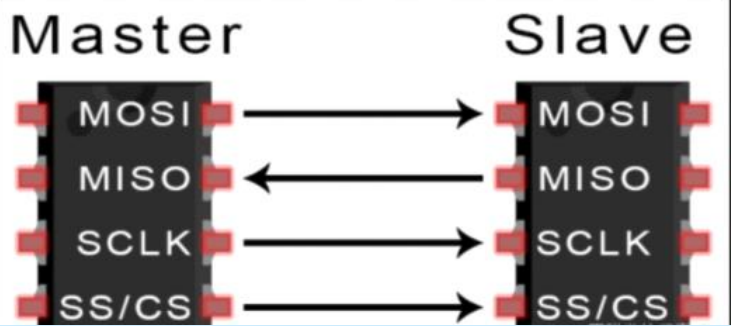

spi协议有4根线,主机输出从机输入MOSI、主机输入从机输出MISO、时钟信号SCLK、片选信号SS\CS 。 一般用于主机和从机之间通信。由主机发起读请求和写请求,主机的权限是主动的,从机是被动的。

二、信号端口解析:

片选信号CS:当CS信号为低时,spi传输开始;cs信号为高时,则为空闲状态。

时钟信号SCK:

MOSI信号:M代表主机、O代表输出,S代表从机、I代表输入,即主机输从机输入,数据的流向是从主机到从机,数据单位bit。也称之为 SDO,S是SPI,D是data,O是output

MISO信号:M代表主机、I代表输入、S代表从机、O代表输出、即主机输入从机输出,数据的流向是从从机到主机,数据单位bit。也称之为 SDI,S是SPI,D是data,O是input

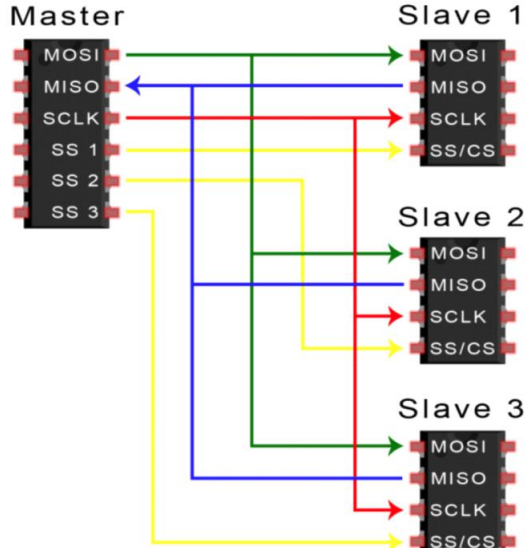

三、连接的方式

下图是一个主机一个从机的连接方式:

下图是一个主机多个从机的连接方式:

一主多从,一个主机控制多个从机。注意不允许多个主机控制一个从机。

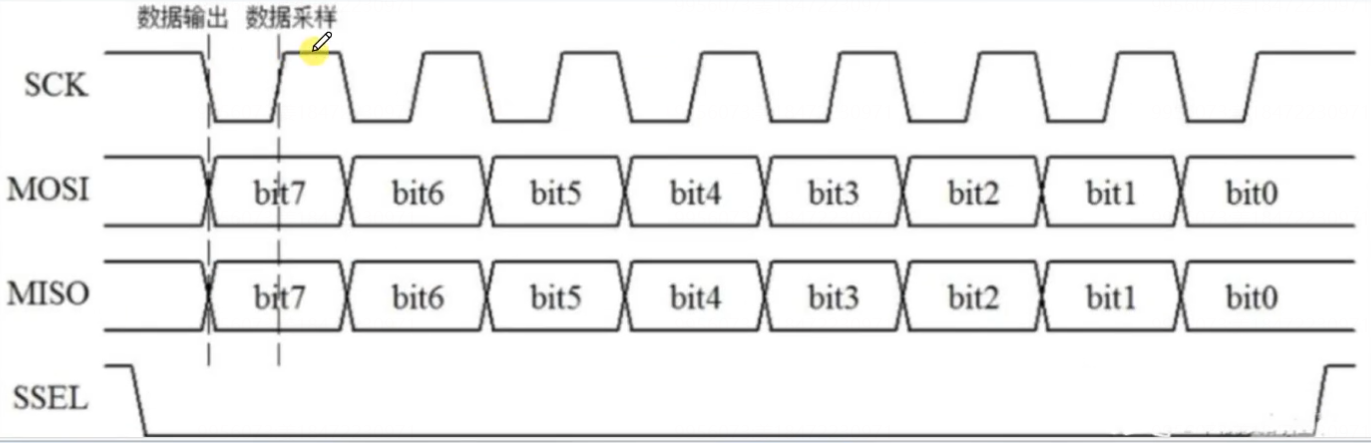

四、时序图

从下面的时序图也可以看出来SPI是全双工的,在时钟的上升沿可以同时发送和接收数据。SSEL信号就是片选信号CS,在SSEL信号为低的时候数据有效,开始发送和接收1bytes数据,在时钟sck的上升沿发送和接收数据。SPI协议属于低速协议,时钟可以跑在10M左右,也可以跑到100M。这个图是其中一个模式下的时序图。这个图中的时钟极性是1,在第二个时钟的跳变沿开始传输数据,所以时钟相位为1。CPOL=1,CPHA=1

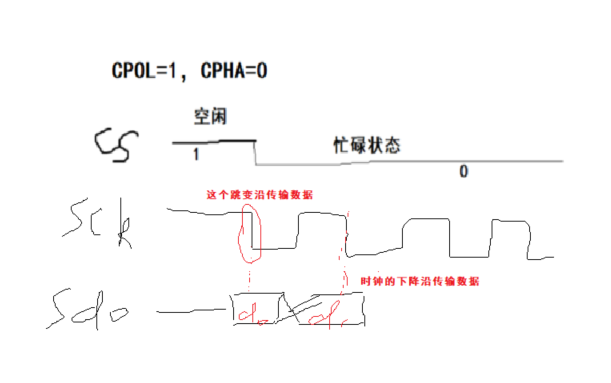

五、时钟极性和时钟相位

时钟极性(CPOL):时钟极性为0时,SCK信号处于低电平;时钟极性为1时,SCK信号处于高电平;

时钟相位(CPHA):时钟相位为0时,SCK第一个跳变沿传输数据;时钟相位为1时,SCK第二个跳变沿传输数据;

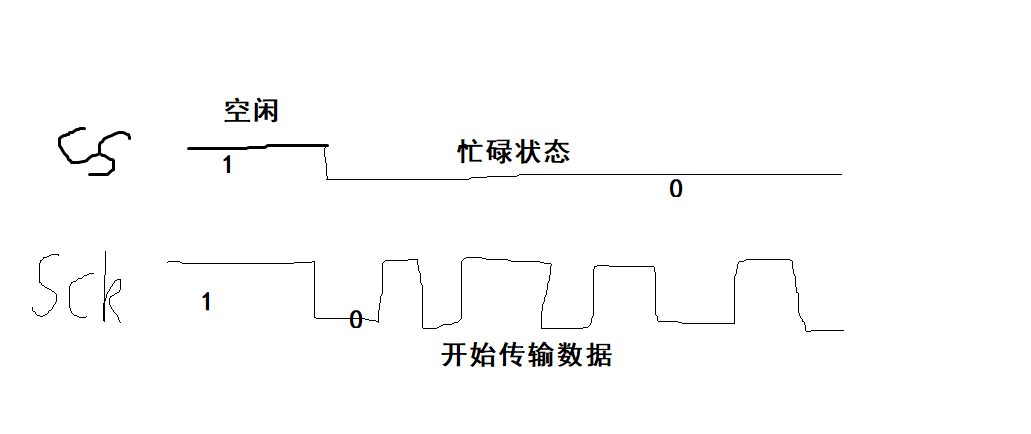

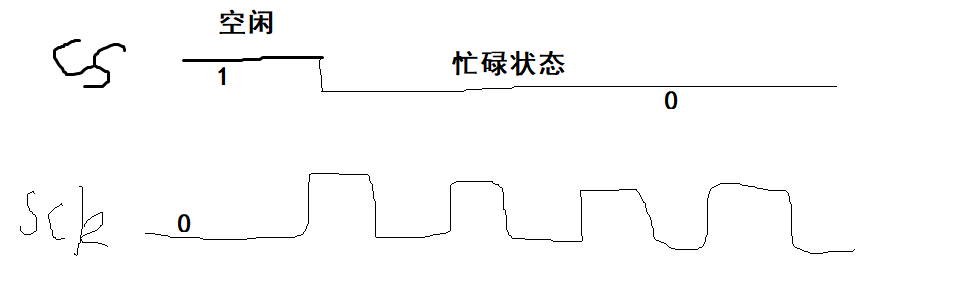

空闲状态时,即片选信号CS为高时,SCK信号此时可以为高电平(时钟极性为1),也可以为低电平(时钟极性为0),对应两种不同的模式。

1)空闲时,CS=1,SCK=1。

2)空闲时,CS=1,SCK=0。

SPI的模式由时钟极性和时钟相位来决定,时钟极性有2种模式,时钟相位也有2种模式,2*2=4种模式。

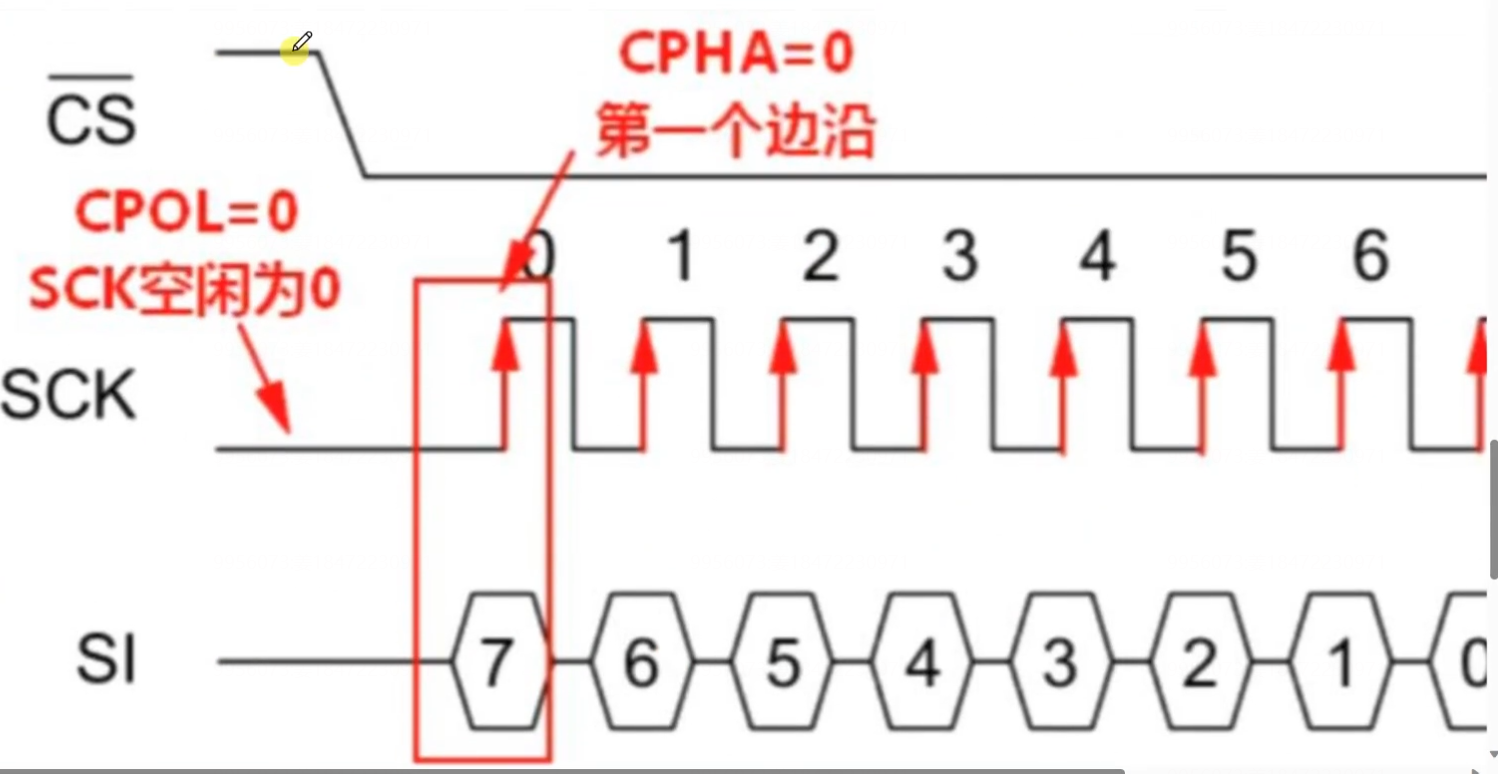

3)例子

在下面这个图中,在空闲的状态,SCK为低电平,时钟极性为0,在时钟的第一个跳变沿发送数据,所以始时钟相位为0。CPOL=0,CPHA=0,这种模式是我们常用的模式

再举一个例子:CPOL=1 ,CPHA=0模式

---晓凡 2023年12月19日于武汉书

![[Win10系统] Win10 任务栏软件图标显示为空白 | 解决方案](https://img-blog.csdnimg.cn/direct/68a85086a06e411ea3f5408256bb1be7.jpeg#pic_left)

![[Verilog] 设计方法和设计流程](https://img-blog.csdnimg.cn/direct/086c99e34f6c4a909369db7a918f9c42.png)