概述:

移位寄存器在数字电路设计中广泛被使用,列如SPI通讯中的串行输入并行输出,并行输出串行输出,FIR滤波器中作为数据的延迟链,边沿检测中的数据延迟链等等。本节针对移位寄存器的基本应用场景给出基本的模版,并观测FPGA综合后的结构图。

内容:

1. 一位分立移位寄存器

2. 串行输入,并行输出延迟链

3. 循环移位寄存器

4. 并行输入串行输出延迟链

5. 总线并行延迟链

1. 一位分立移位寄存器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a ,

output[3:0] y1 // output signal

);

reg a_dly1 ;

reg a_dly2 ;

reg a_dly3 ;

assign y1={a_dly3,a_dly2,a_dly1,a}; //穿行输入,并行输出

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0) begin

a_dly1 <= 1'b0 ;

a_dly2 <= 1'b0 ;

a_dly3 <= 1'b0 ;

end else begin

a_dly1 <= a ;

a_dly2 <= a_dly1 ;

a_dly3 <= a_dly2 ;

end

end

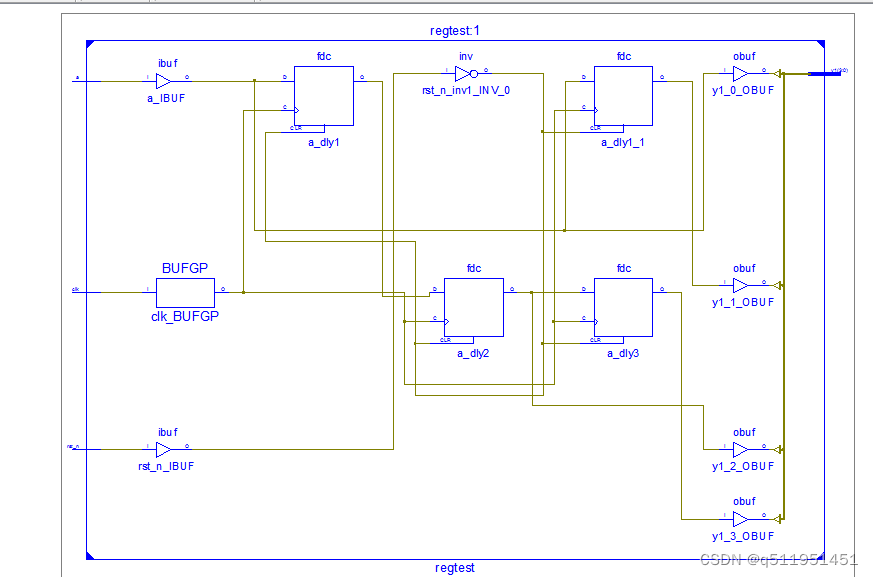

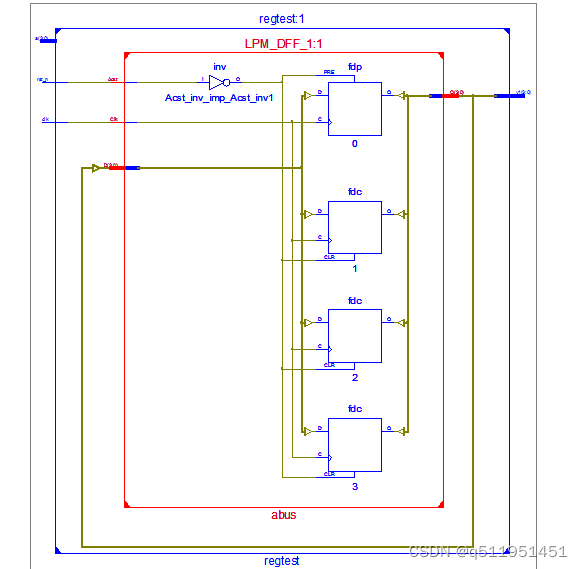

endmoduleRTL结构图,移位寄存器的结构通过FDC触发器串联构成。

技术原理图

2. 串行输入并行输出

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input a ,

output[3:0] y1 // output signal

);

reg[3:0] abus ;

assign y1=abus;

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0) begin

abus <= 1'b0 ;

end else begin

abus <= {abus[2:0],a} ;

end

end

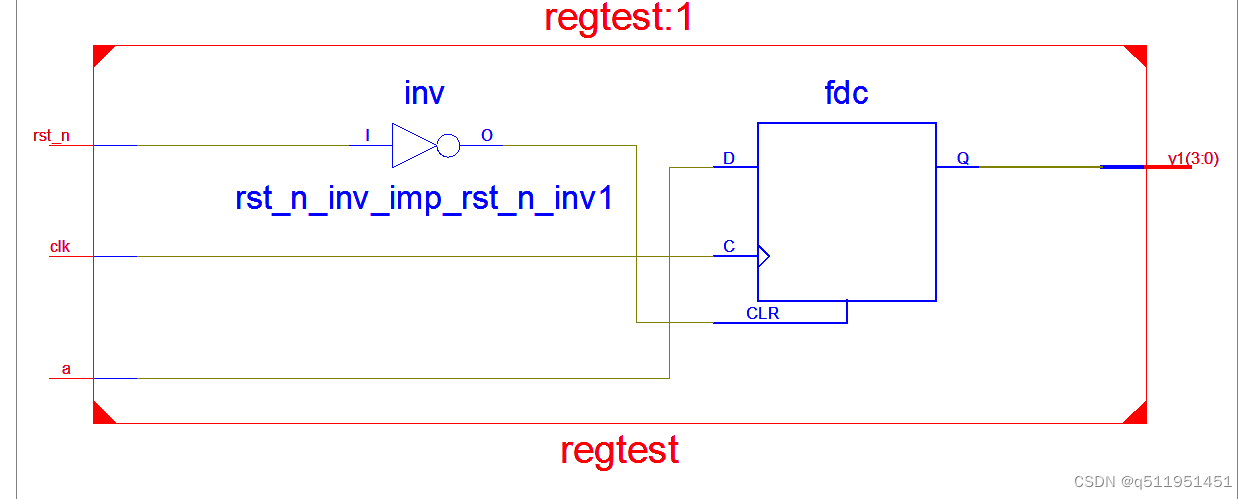

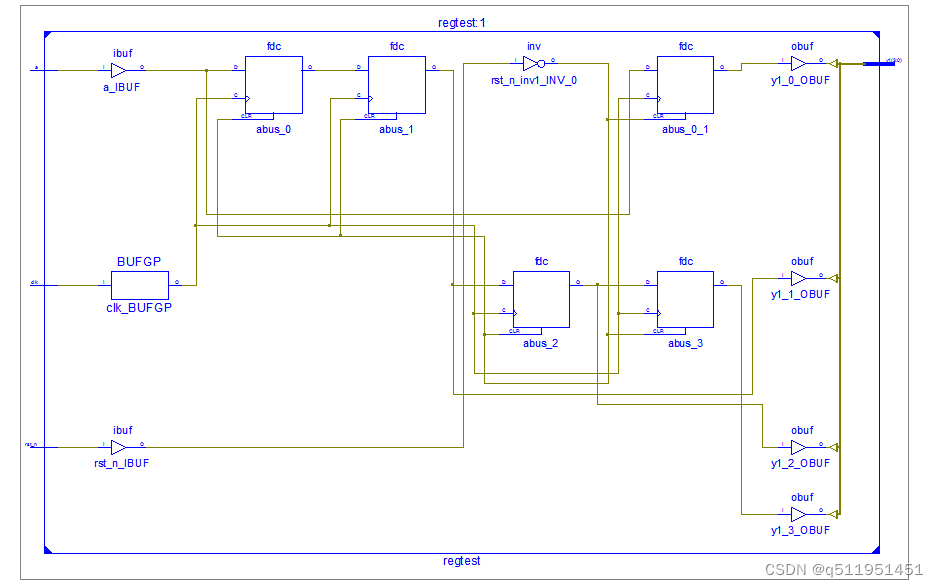

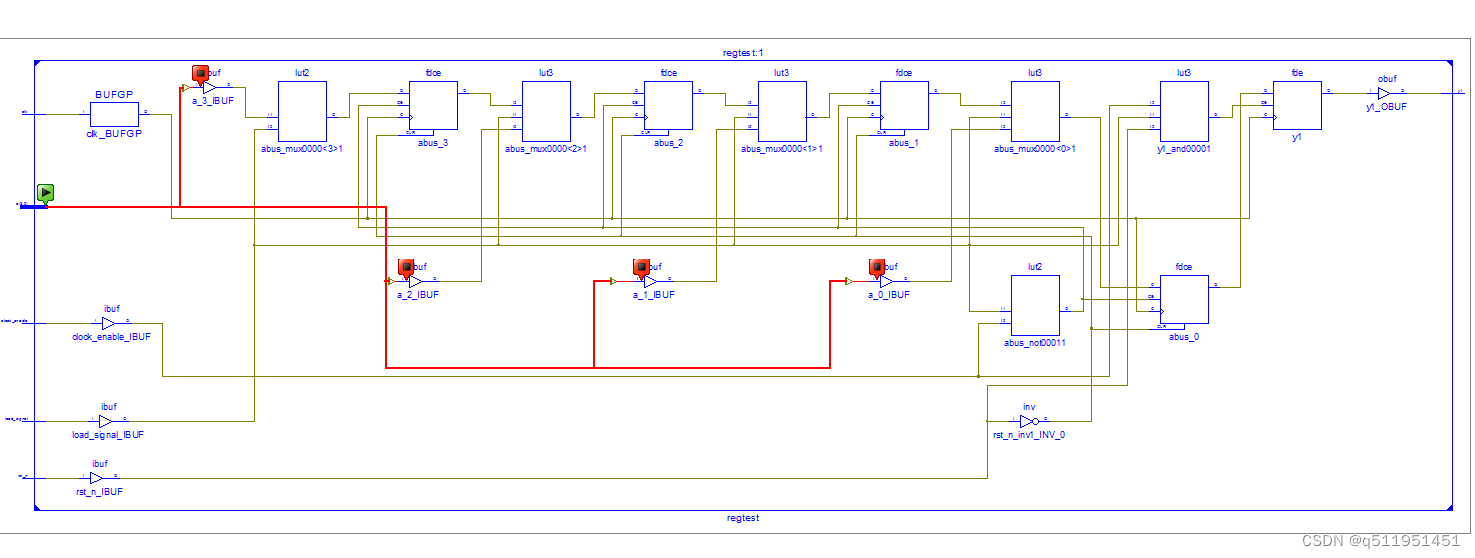

endmoduleRTL结构图

技术原理图,总线结构移位寄存器更加简洁,但是实现的电路结构是一样的。

3. 循环移位寄存器

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input[3:0] a ,

output[3:0] y1 // output signal

);

reg[3:0] abus ;

assign y1=abus;

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0) begin

abus <= 1 ;

end else begin

abus <= {abus[2:0],abus[3]} ;

end

end

endmodule

RTL结构图

技术原理图

4. 并行输入,串行输出

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input[3:0] a ,

input load_signal,

input clock_enable,

output reg y1 // output signal

);

reg[3:0] abus ;

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0) begin

abus <= 4'b0 ;

end else if (load_signal) begin

abus <= a ;

end else if (clock_enable) begin

abus <= {1'b0,abus[3:1]};

y1 <=abus[0];

end

end

endmodule

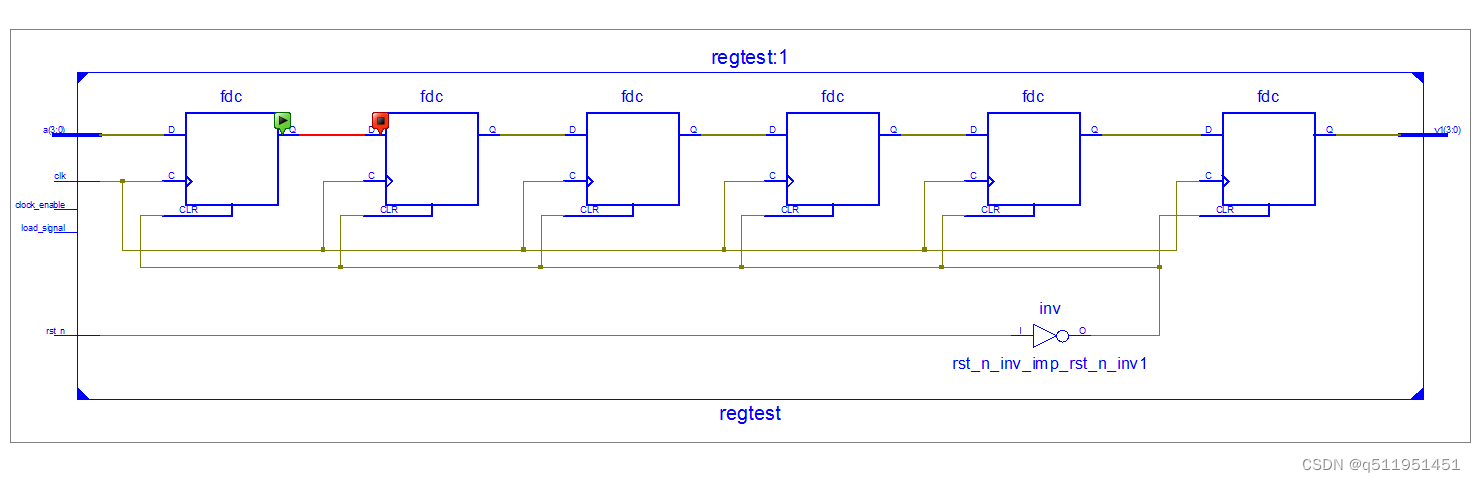

RTL结构图

技术原理图

5. 总线并行延迟链

代码

module regtest(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

input[3:0] a ,

input load_signal,

input clock_enable,

output [3:0] y1 // output signal

);

reg[3:0] abus [5:0];

integer i;

assign y1 = abus[5];

always @ (posedge clk or negedge rst_n ) begin

if (rst_n == 1'b0) begin

for (i=0;i<6;i = i+1)begin

abus[i] <= 4'b0;

end

end else begin

for (i=1;i<6;i = i+1)begin

abus[i] <= abus[i-1];

end

abus[0] <= a;

end

end

endmodule

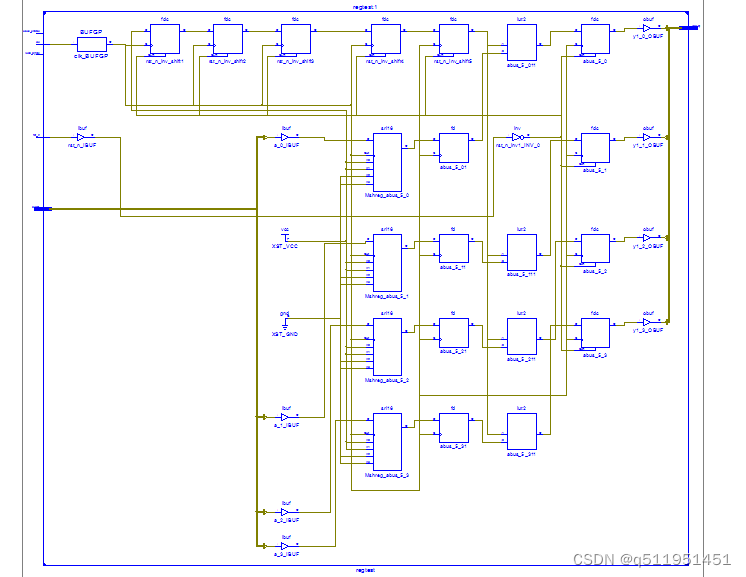

RTL结构图

技术原理图,总线延迟链中使用了SRL16移位寄存器来实现数据延迟,这是LUT内部的移位寄存器,他可以节省flip_flop的使用。

6. 总结

1. 移位寄存器广泛用于通讯的输入输出端口输出,FIR滤波的延迟,以及随机数生成等场景

2. FPGA内部使用flip_flop触发器来实现移位寄存器

3. 对于大量的移位操作,FPGA可以使用LUT4的SRL16移位寄存器来实现。