在ZNS SSD设计中,也有很多的挑战:

-

Open Zones 对写入缓冲区的需求:保持大量的 open zones(例如 1K+)会增加对带宽的需求,并要求控制器提供足够的缓冲空间来管理并发写入请求。这需要较大的高带宽写入缓冲区以降低延迟并优化性能。

-

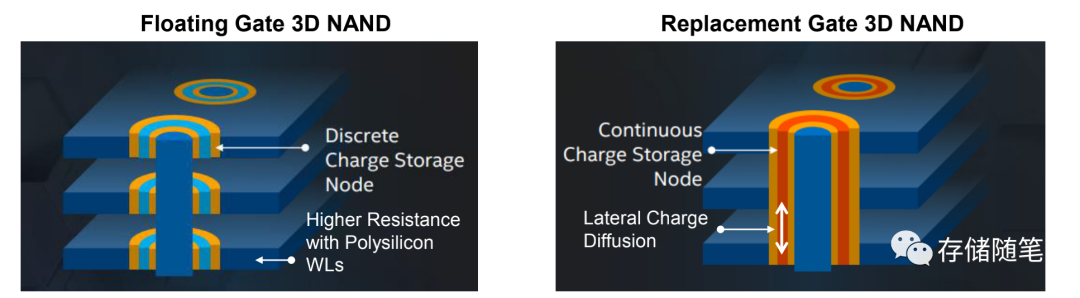

Charge-trapping QLC NAND 的编程需求:由于 charge-trapping QLC NAND 需要两次编程操作和两次数据传输,以及 要解决CTF相邻位之间的耦合效应可能导致编程电压分布不均匀引入的N WL gaps,因此在处理写入请求时可能需要更大的缓冲空间。这会进一步增加对写入缓冲区的需求。

这也是为什么FG架构QLC NAND SSD性能比CTF架构QLC NAND SSD性能要好(具体介绍请参考:浅析不同NAND架构的差异与影响)

尽管存在这些问题,但 charge-trapping QLC NAND 的高密度和低成本优势使其成为大容量存储应用的理想选择。

-

写入冲突管理:为了处理 write-write collision 和 write-erase collision,SSD 控制器需要额外的缓冲空间来存储等待写入的数据。这导致了对写入缓冲区容量的需求增大。

-

SSD 控制器内部 SRAM 的限制:通常情况下,SSD 控制器内部的 SRAM 容量有限(通常为 8-16MB),可能不足以满足所有 open zones 的数据操作和编程缓冲需求。

-

使用 DRAM 的限制:虽然可以考虑使用 DRAM 作为编程缓冲区,但 DRAM 带宽有限,并且受到超级电容的影响。此外,DRAM 的成本也相对较高。

-

RAID 纠错码 (parity) 缓冲区大小和容量开销:在使用 RAID 纠错机制的环境中,需要预留额外的空间用于存放 parity 数据。这增加了对 SSD 控制器资源的需求,并可能导致容量上的开销。

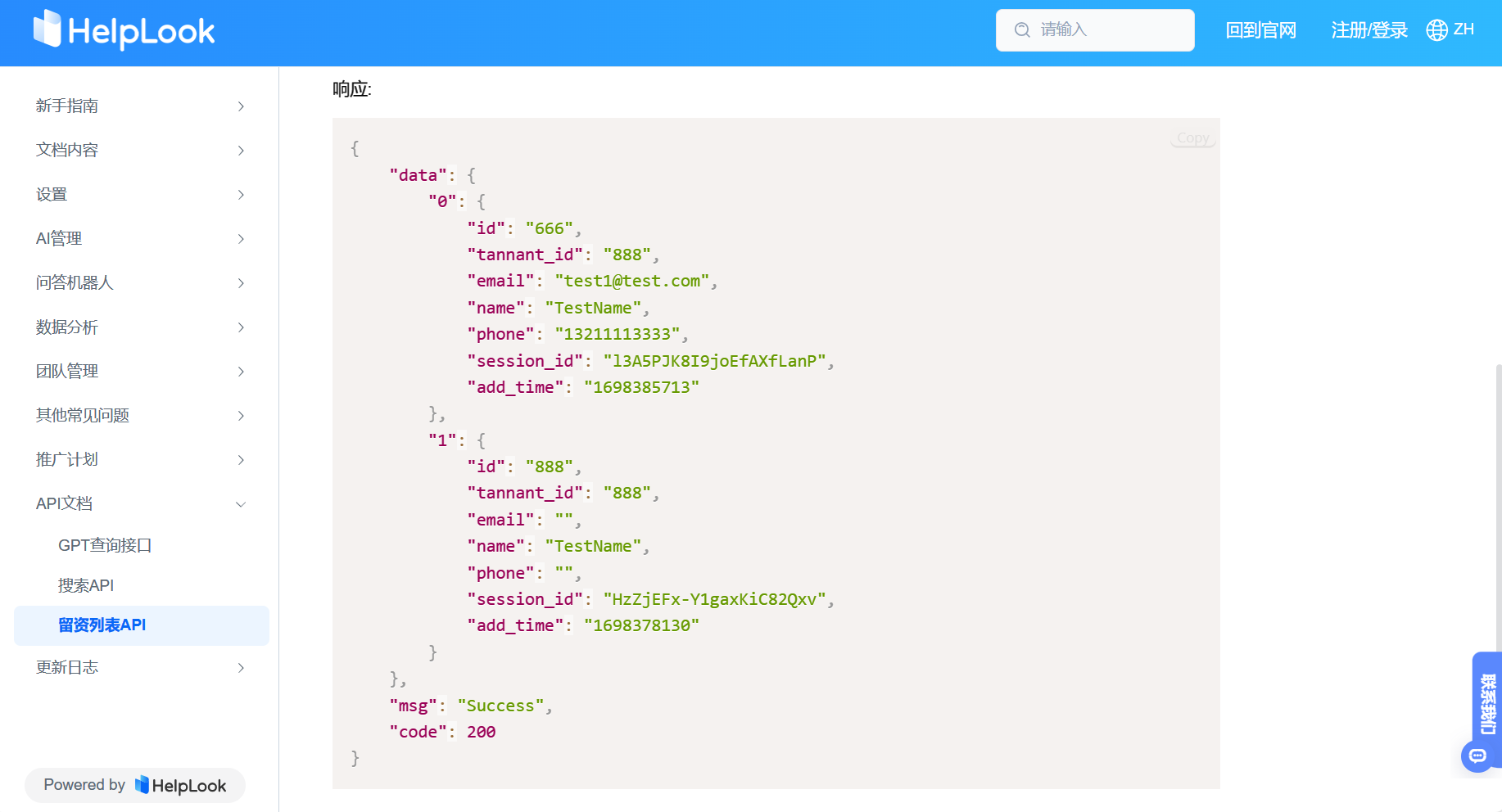

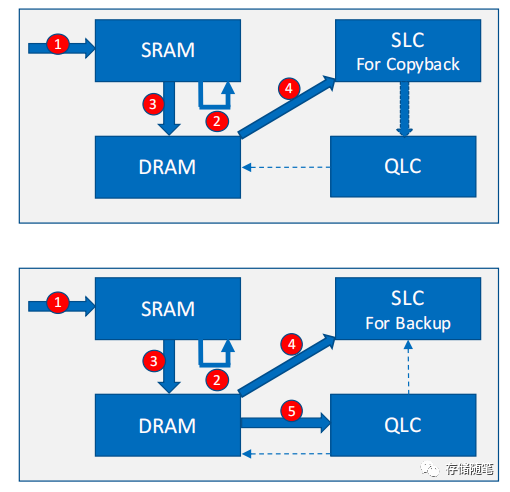

为了解决以上问题,业内有这么一种做法,使用 2-stage 缓存(SRAM+DRAM)处理数据操作和编程的方案:

1.SRAM 和 DRAM 的作用:

-

SRAM:用于 RAID 编码、FW 元数据插入以及 RAID 纠错码 (parity) 缓冲区。

-

DRAM:用作 SLC 或直接编程 QLC 的数据缓冲区。

2.支持 1K+ Open/Active Zone:

-

SLC Copyback:这种方法将待编程的数据先写入到 SLC 区域,然后再从 SLC 区域复制回 QLC 区域。由于 SLC 的编程速度较快,可以减少整体的编程时间。然而,这种策略需要额外的硬件资源来监控 SLC 块的 RBER,并确保数据的可靠性。

-

SLC Backup:这种方法将待编程的数据直接存储在 DRAM 中,然后一次性写入到 QLC 区域。虽然这种方法可能会消耗更多的 DRAM 带宽,但它避免了在不同区域之间进行数据移动,简化了数据管理过程。

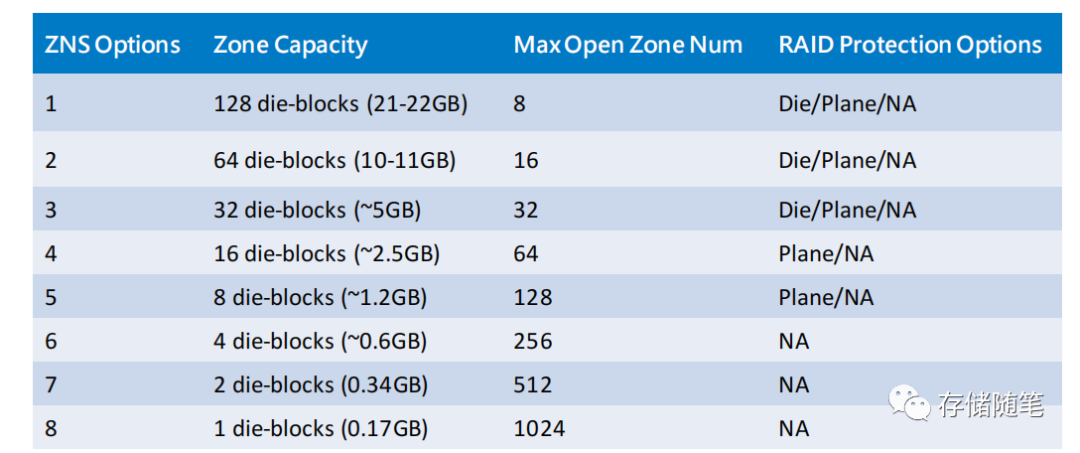

在不同的Zone的大小,对Open Zone数量和RAID配置有不同的需求。ZNS 和 Die-block 结合使用可以带来一些优势,包括更好的数据组织、更高的 I/O 性能以及更有效的资源管理。ZNS 可以将存储设备划分为一系列连续的逻辑分区(zones),每个 zone 具有预设的最大容量。这种设计有利于顺序写入,从而降低写入放大效应和延迟。但也存在一些潜在挑战,如如何有效地分配和管理 zones,如何平衡不同 dies 或 LUNs 之间的负载等。

小编每日撰文不易,如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

-

浅析不同NAND架构的差异与影响

-

SSD基础架构与NAND IO并发问题探讨

-

字节跳动ZNS SSD应用案例解析

-

SSD数据在写入NAND之前为何要随机化?

-

深度剖析:DMA对PCIe数据传输性能的影响

-

NAND Vpass对读干扰和IO性能有什么影响?

-

HDD与QLC SSD深度对比:功耗与存储密度的终极较量

-

NVMe SSD:ZNS与FDP对决,你选谁?

-

如何通过优化Read-Retry机制降低SSD读延迟?

-

关于硬盘质量大数据分析的思考

-

存储系统性能优化中IOMMU的作用是什么?

-

全景解析SSD IO QoS性能优化

-

NVMe IO数据传输如何选择PRP or SGL?

-

浅析nvme原子写的应用场景

-

多维度深入剖析QLC SSD硬件延迟的来源

-

浅析PCIe链路LTSSM状态机

-

浅析Relaxed Ordering对PCIe系统稳定性的影响

-

实战篇|浅析MPS对PCIe系统稳定性的影响

-

浅析PCI配置空间

-

浅析PCIe系统性能

-

存储随笔《NVMe专题》大合集及PDF版正式发布!