根据用户手册使用IP核

① 找到user guide / product guide 并打开

② 找到Customizing and Generating the Core(不同手册可能题目不一样),查看IP核的创建过程中各个参数的意义和设置方法。

③ 找到port description ,查看接口注释

根据网络教程使用IP核

查找别人用IP核的经验、教程,快速上手。

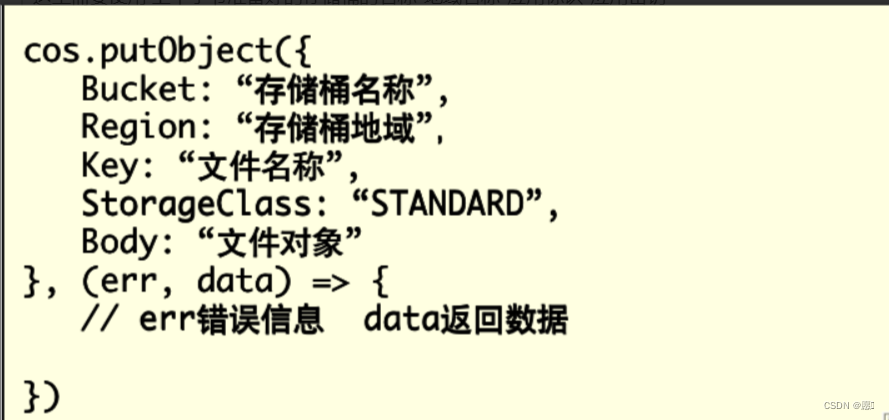

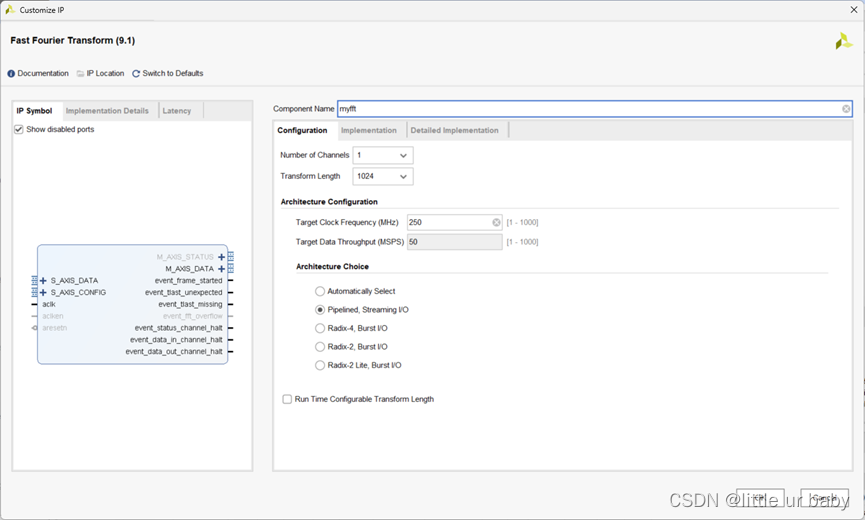

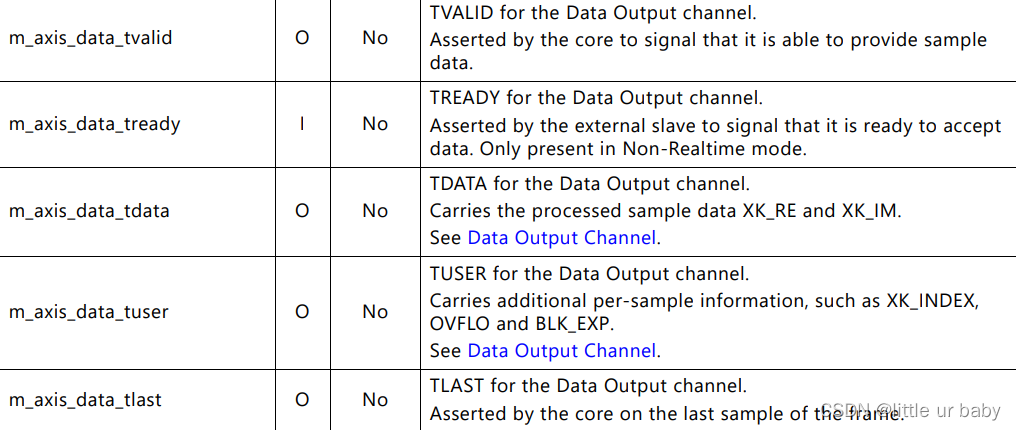

一、FFT IP核 GUI界面

左边框信息是根据右边框选项确定的引脚和性能参数。

number of channels : 通道数,正常情况只需一个通道。

transform length : fft变换频点数(8~65536),点数越高,频率越准确,但占用的资源block rams越多,transform cycles 和 latency(延迟) 也就越大。

(解释:假设信号的真实频率为1MHz和7MHz,fft ip设置为采样频率50M,

当频点数2048时,每个频点数代表的频率为:50/2048 = 0.024414 M,最接近1MHz的频点为:1 / 0.024414 = 40.98 即第41个频点,该频率为:41 * 0.024414 = 1.00081M;同理算出最接近7MHz的频点为:7 / 0.024414 = 286.89 即第287个频点,该频率为:287 * 0.024414 = 7.0028 M;

当频点数1024时,每个频点数代表的频率为:50/1024 = 0.048828 M,最接近1MHz的频点为:1 / 0.048828 = 20.49 即第21个频点,该频率为:21 *0.048828 = 1.0248M;同理算出最接近7MHz的频点为:7 / 0.048828= 143.44 即第144个频点,该频率为:144 * 0.048828 = 7.0272 M;对比一下,频点数为2048,误差分别为:0.00081、0.0028;频点数为1024,误差分别为0.0248、0.0272;)

target clock frequency : 采样时钟频率,

architecture choice:FFT IP核的架构,不同选项会对latency和transform cycles产生影响。

(automatically select:勾选自动选择以选择满足指定目标数据吞吐量的最小实现,前提是FFT核心在FPGA上实现时达到指定的目标时钟频率。)

run time configurable transform length:选择运行时可配置或不可配置的变换长度。当转换长度不可在运行时配置时(即不勾选),核心使用更少的逻辑资源,并具有更快的最大时钟速度。一般不勾选

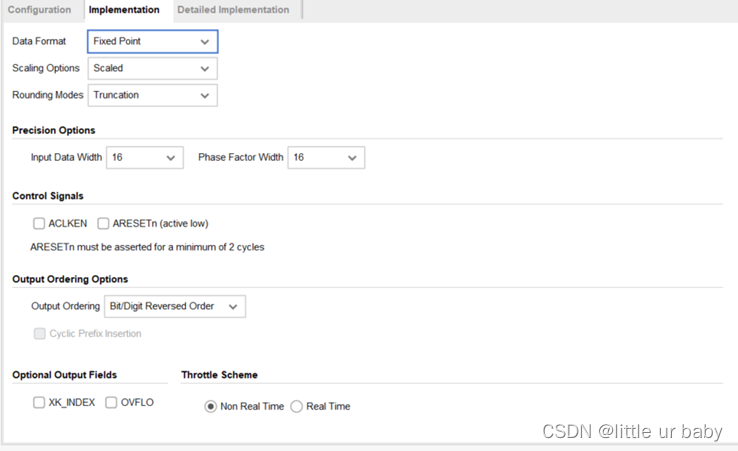

data format :数据格式,选择输入和输出数据样本是固定点格式,还是IEEE-754单精度(32位)浮点格式。当核心处于多通道配置时,浮点格式不可用。fixed point 固定点;floating point 浮点数 可以选fixed point。

scaling options: 未标度(unscaled):-所有整数位增长都被带到输出端,这可以使用更多的FPGA资源。缩放(scaled):用户定义的缩放时间表确定如何在FFT阶段之间缩放数据。

块浮点(block floating point):由核来确定最佳利用可用动态范围所需的缩放程度,并将缩放因子报告为块指数。不同的选择会改变S_AXIS_CONFIG-TDATA的接口情况,一般情况下,选block floating point即可。

rounding modes:对输出的数据进行处理:truncation截断 convergent rounding:收敛舍入,四舍五入。选择convergent rounding可以避免直流偏置,但会增加slice使用率和时延。平时直接选truncation截断也是可以的。

output ording :natural order:正序 bit/digit reversed order :倒序,一般选择natural order。

optional output fields: 是否勾选 xk_index 即 意味着是否要带频谱峰值的坐标,可以勾选上。

Throttle Schemes:选择性能和数据定时之间的折衷要求。实时模式通常提供更小、更快的设计,但对何时必须提供和使用数据有严格的限制;非实时模式没有这样的限制,但设计可能更大、更慢。一般选non real time即可。

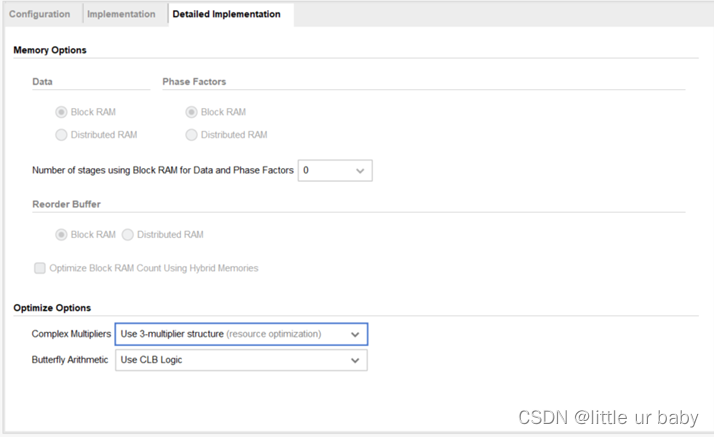

complex multipliers:选择乘法器的结构,上面有注释,一个资源优化型(resource optimization),一个性能优化型(performance optimization)。

复数乘法器:有三个选项可用于自定义复数乘法器实现:

-使用CLB逻辑:所有复数乘法器都是使用切片逻辑构建的。这是

适用于性能要求较低的目标应用程序,或

目标设备具有很少的DSP切片。

-使用3乘法器结构(资源优化):所有复数乘法器

使用三实乘五加/减结构,其中乘法器使用

DSP切片。这减少了DSP切片计数,但使用了一些切片逻辑。这

结构可以利用DSP片预加器来减少或消除对

用于额外的片逻辑,并提高性能。

butterfly arithmetic:蝶形实现的自定义有两个选项:

-使用CLB逻辑:所有蝶形级都是使用片逻辑构建的。

-使用XtremeDSP切片:此选项强制使用DSP切片中的加法器/减法器来实现所有蝶形级。

一般默认就行。

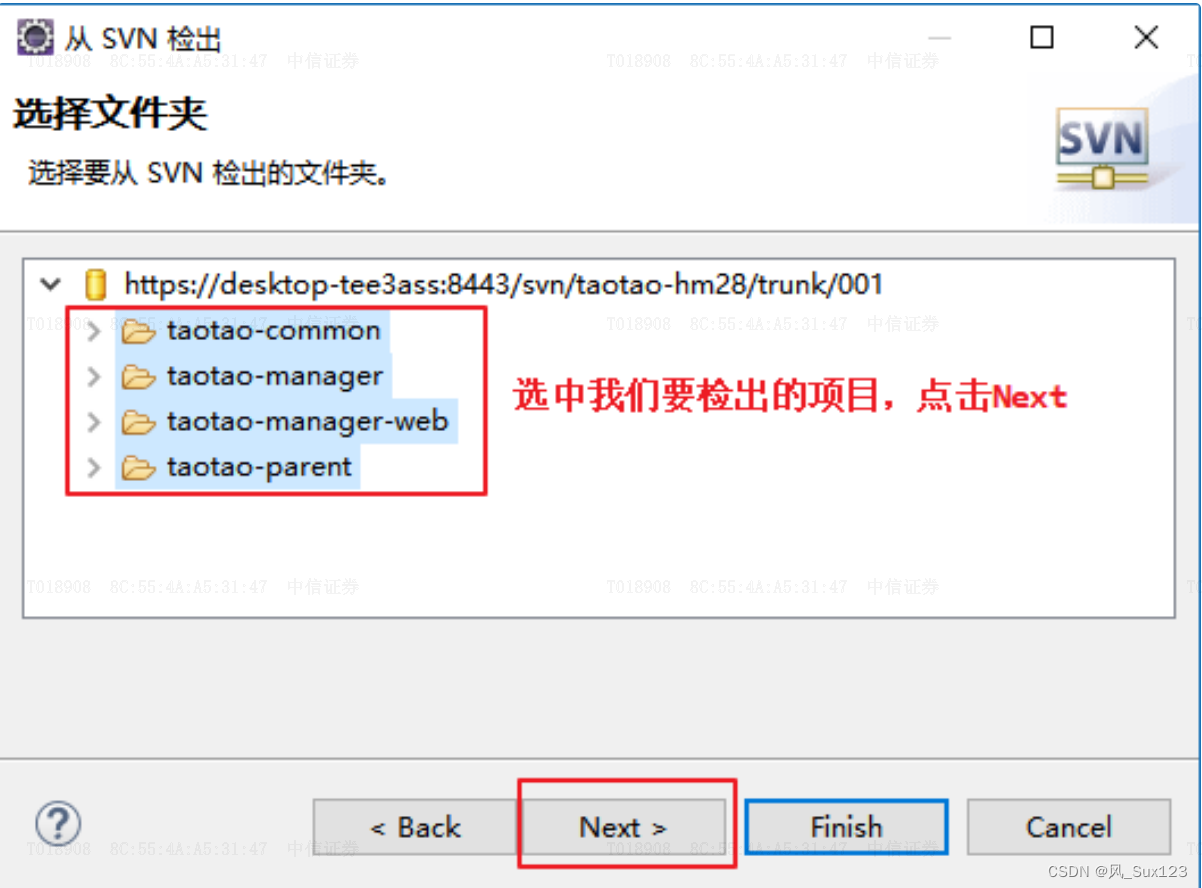

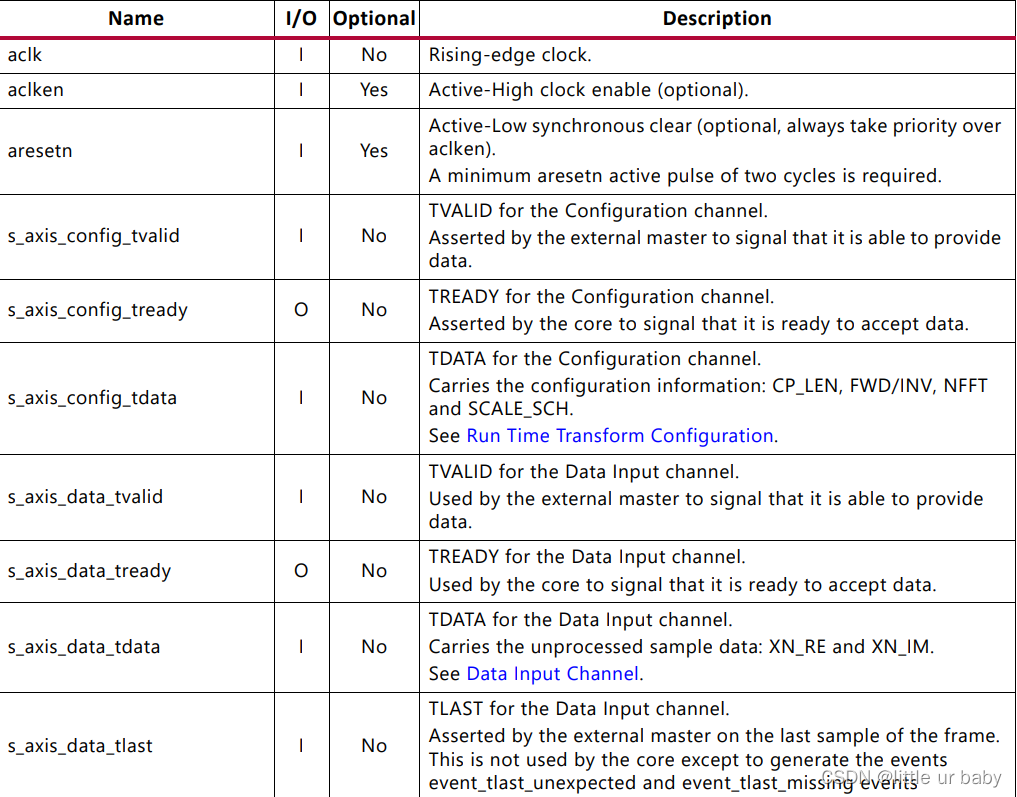

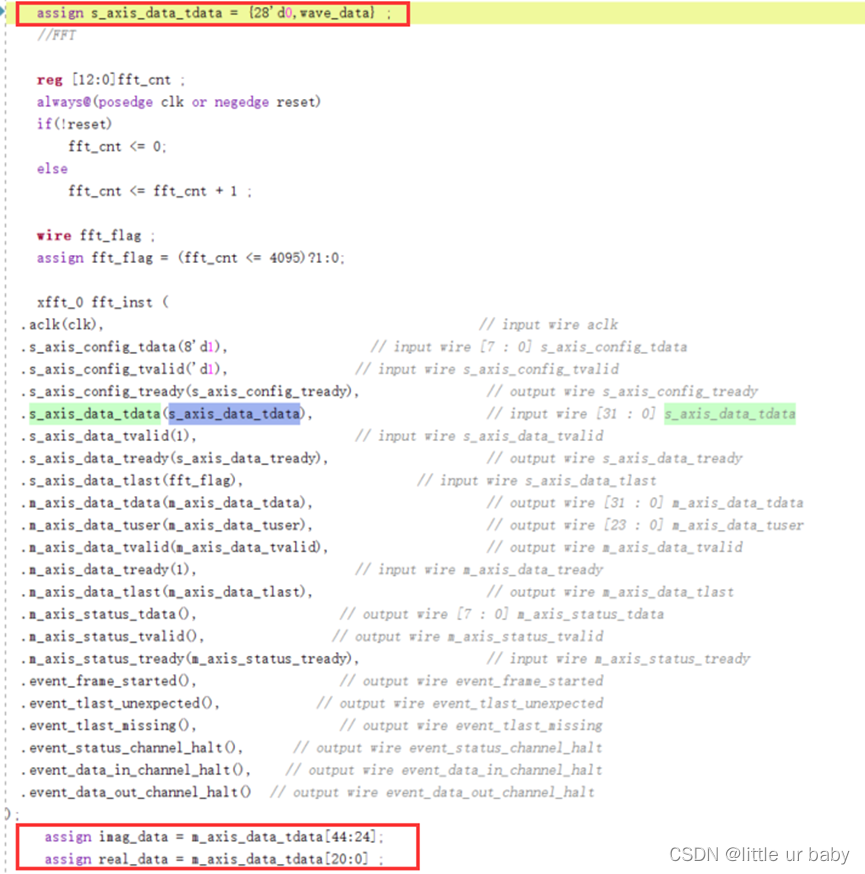

二、FFT IP核 引脚信息

引脚信号:

aclk:输入时钟(要用)

1.输出信号,用于指示设计逻辑:

s_axis_config_tready:输出信号,由IP核发出,表示准备好接受数据。要用

s_axis_data_tready:输出信号,表示Ip核准备好接收数据了。要用

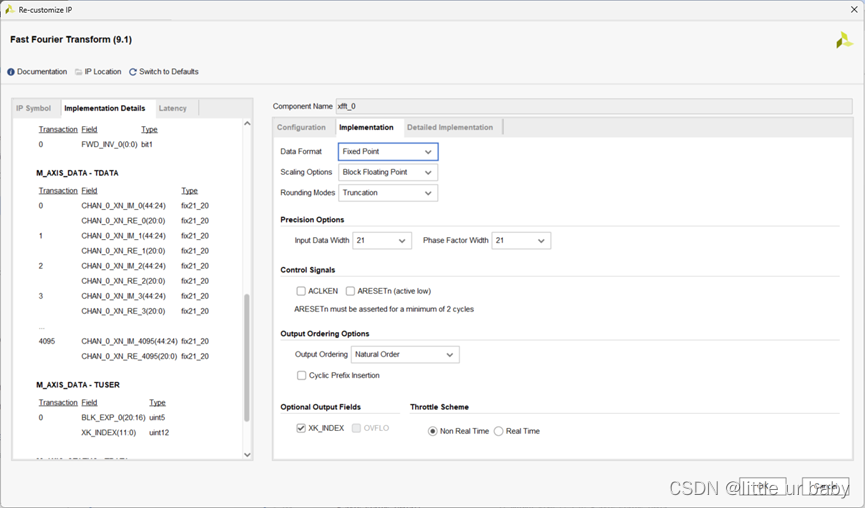

m_axis_data_tdata:傅里叶变换后的频谱数据,包括实部XK_RE和虚部XK_IM。高位是虚部,低位是实部。(可以在IP核中看到)

m_axis_data_tvalid:表明可以输出有效数据。(有用)

m_axis_data_tuser:数据输出。坐标:携带频点坐标信息,如XK_INDEX、OVFLO和BLK_EXP。勾选了XK_INDEX才有。

m_axis_data_tlast:输出的最后一个数据(不怎么用的上)

2.输入信号,用于控制FFT IP核:

s_axis_config_tdata:输入信号,配置通道的TDATA。8‘d1:傅里叶变换;8’d0:逆变换

s_axis_config_tvalid:输入信号,1即输入有效,置1即可。

s_axis_data_tdata:数据输入,要进行傅里叶变换的数据。要用

s_axis_data_tvalid:数据输入。要用

s_axis_data_tlast:数据输入。1表示当前数据是要计算的最后一个数据。除生成事件event_tlast_unexpected和event_tlast_missing事件外,核心不使用此项。这里置1就好(置0也可以。)

m_axis__tready:数据输入。由外部从机断言,以发出准备接受的信号,数据仅在非实时模式下存在。(置1即可)

3.事件接口

一般用不上,直接不连,综合时直接省略

m_axis_status_tdata:状态通道的TDATA。携带状态数据:BLK_EXP或OVFLO。(不连)

m_axis_status_tvalid:状态频道的TVALID。由核心断言,以表示它能够提供状态数据。(不连)

m_axis_status_tready:状态通道的TREADY。由外部从机断言,以发出准备接受的信号

数据仅在非实时模式下存在(得置1,不然IP输出结果出错)

event_frame_started:在核心开始处理新帧时断言。(不连)

event_tlast_unexpected:当核心在不是帧中最后一个的数据样本上看到s_axis_data_tlast High时断言。(不连)

event_tlast_missing:当帧的最后一个数据采样的s_axis_data_tlast为Low时断言。(不连)

event_status_channel_halt:当核心尝试将数据写入状态通道但无法写入时断言。仅在非实时模式下存在。(不连)

event_data_in_channel_halt:当核心从数据输入通道请求数据且无可用数据时断言。(不连)

event_data_out_channel_halt:当核心尝试将数据写入数据输出通道但无法写入时断言。仅在非实时模式下存在(不连)

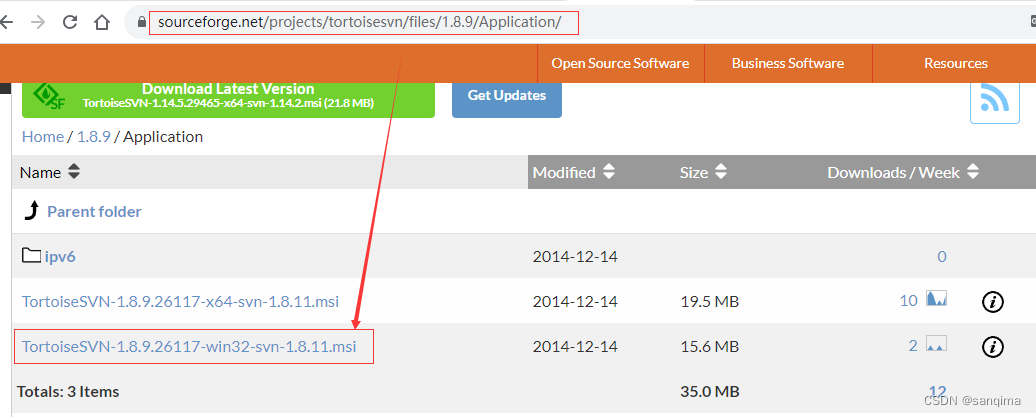

三、FFT IP核 测试

1.理论设定:

信号1:1.564 M

信号2:6.25 M

混频:

6.25 – 1.564 = 4.686 M

6.25+1.564=7.814M

故FFT后的信号频谱应该包含: 1.564 M,4.686 M,6.25 M,7.814M

2.仿真设定:

DDS产生两个正弦信号:1.564 M,6.25 M:10位无符号数(由软件生成的大小为0~1023的正弦波)

两个正弦信号混频之后:20位无符号数

FFT输入设置:21位有符号数(符号位补0)

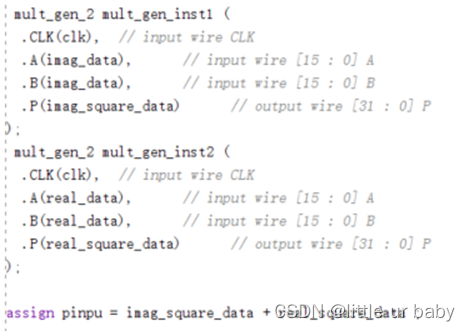

根据IP核信息补充输入数据虚部,截取输出数据实部与虚部:

求频谱强度:

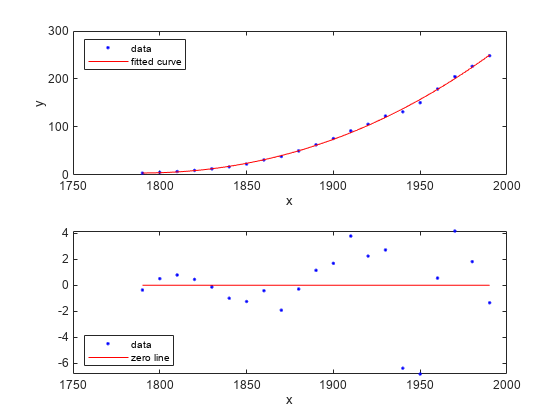

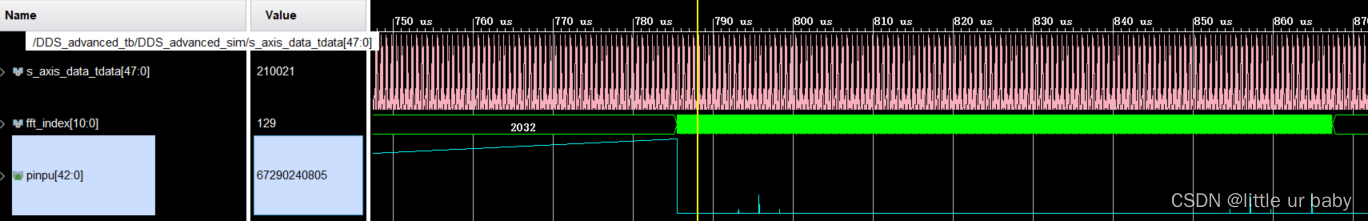

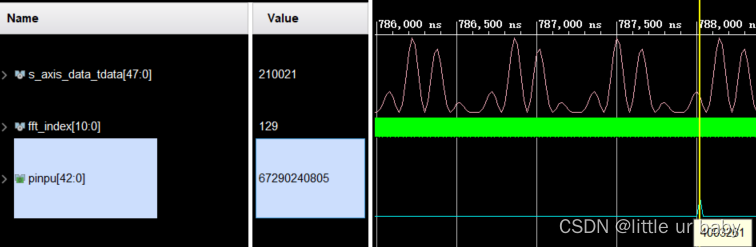

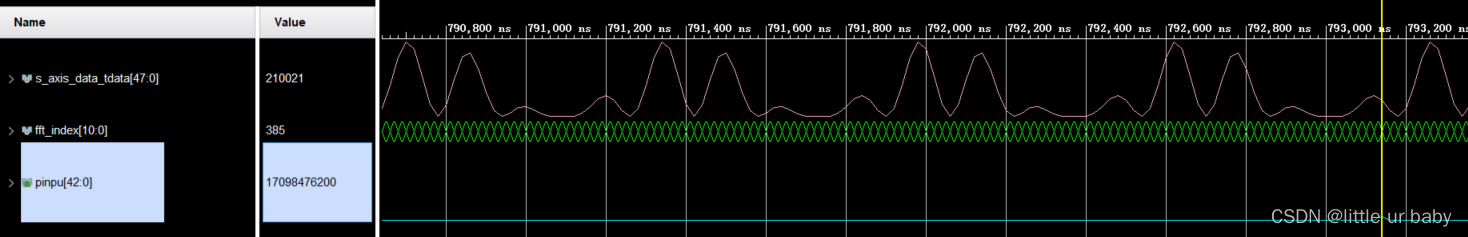

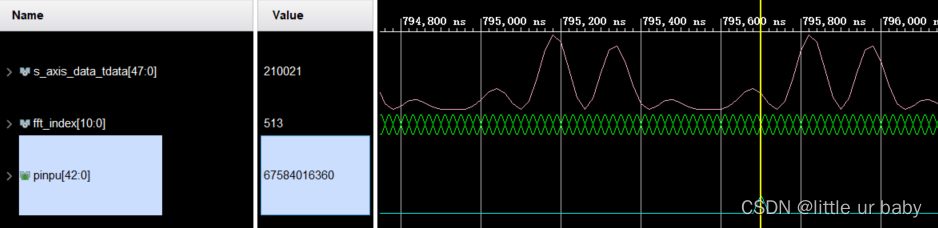

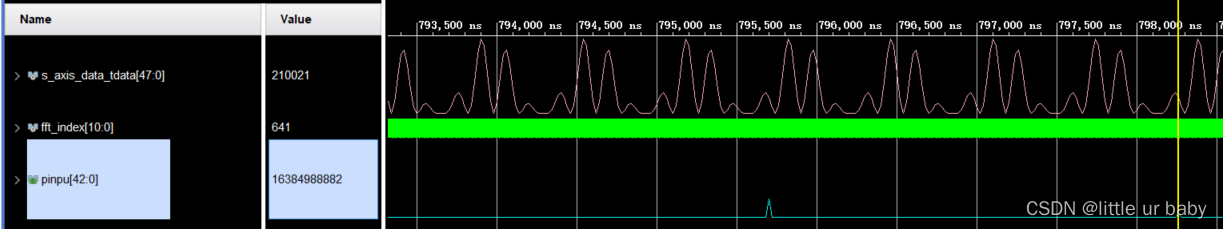

3.仿真结果:

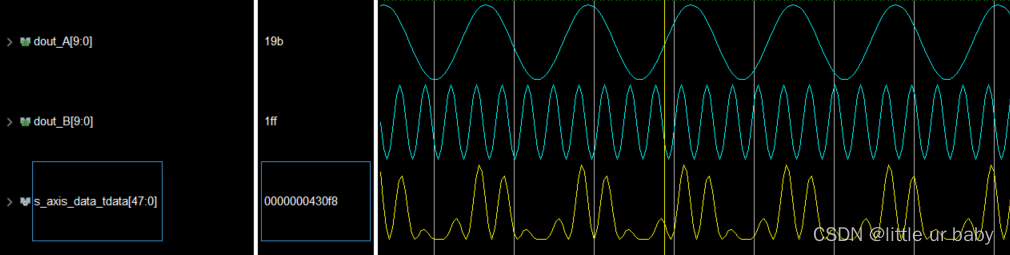

DDS产生两个正弦信号:dou_A dout_B

f=50/2048 * 128 = 1.574

f=50/2048 * 384 = 4.687

f=50/2048 * 512 =6.25

f=50/2048 * 640 = 7.812

即仿真结果:1.562 M,4.687 M,6.25 M,7.812 M

相比理论值:1.564 M,4.686 M,6.25 M,7.814M

由于精度为50/4096 MHz = 0.012M,所以计算出来的频率有一点小小的偏差,属于正常范围。

四、总结:

1. 仿真结果不对时,可以先把该IP核的所有信号加入仿真波形中检查,看看信号有无XZU状态,是否合理,并进行修改后看是否有变化。

2. 数据的类型:有符号数/无符号数 对于信号处理,特别是对于FFT来说影响还是挺大的,要确定输入的波形是正确的(比如fft要求输入为有符号数,那么输入有符号数波形应该与预想的波形一致),才能得到正确的频谱。

3. FFT IP核要求输入为有符号数,而正弦信号为无符号数时,除了增加一位符号位(0)外,还可以先通过运算把无符号数转换为有符号数,再输入FFT。

4.无论是FFT,还是乘法器或是其他IP核,都要注意输入输出数据的符号类型,提高测试速度。