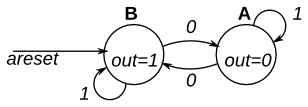

简单摩尔状态机1(Fsm1)

是一个摩尔状态机,具有两种状态,一种输入,一种输出。实现此状态机。请注意,重置状态为 B。使用异步复位。

模块声明

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);

答案

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case (state)

B:begin

if (in=='b0) begin

next_state = A;

end else begin

next_state = state;

end

end

A:begin

if (in=='b0) begin

next_state = B;

end else begin

next_state = state;

end

end

default:next_state = A;

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset=='b1)

state<=B;

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == B);

endmodule

简单摩尔状态机2(Fsm1s)

这是一个摩尔状态机,具有两种状态,一种输入,一种输出。实现此状态机。请注意,重置状态为 B。与简单摩尔状态机1,本例使用同步复位。

模块声明

module top_module(

input clk,

input reset, // synchronous reset to state B

input in,

output out);

答案

module top_module(

input clk,

input reset, // synchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

// State transition logic

case (state)

B:begin

if (in=='b0) begin

next_state = A;

end else begin

next_state = state;

end

end

A:begin

if (in=='b0) begin

next_state = B;

end else begin

next_state = state;

end

end

default:next_state = A;

endcase

end

always @(posedge clk) begin // This is a sequential always block

// State flip-flops with synchronous reset

if(reset=='b1)

state<=B;

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == B);

endmodule

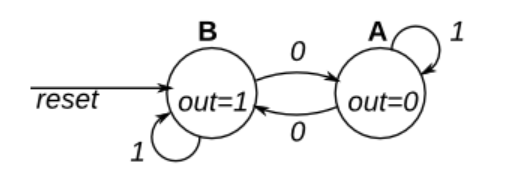

简单摩尔状态机3(Fsm2)

这是一个摩尔状态机,具有两个状态、两个输入和一个输出。实现此状态机。使用异步复位。

模块声明

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out);

答案

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

if(areset=='b1)

next_state = OFF;

else begin

case (state)

OFF:begin

if (j=='b1) begin

next_state = ON;

end

else begin

next_state = state;

end

end

ON:begin

if (k=='b1) begin

next_state = OFF;

end

else begin

next_state = state;

end

end

endcase

end

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if(areset=='b1)

state<=OFF;

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == ON);

endmodule

简单摩尔状态机4(Fsm2s)

这是一个摩尔状态机,具有两个状态、两个输入和一个输出。实现此状态机。使用同步复位。

模块声明

module top_module(

input clk,

input areset, // synchronous reset to OFF

input j,

input k,

output out);

答案

module top_module(

input clk,

input reset, // synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

if(reset=='b1)

next_state = OFF;

else begin

case (state)

OFF:begin

if (j=='b1) begin

next_state = ON;

end

else begin

next_state = state;

end

end

ON:begin

if (k=='b1) begin

next_state = OFF;

end

else begin

next_state = state;

end

end

endcase

end

end

always @(posedge clk) begin

// State flip-flops with synchronous reset

if(reset=='b1)

state<=OFF;

else begin

state<=next_state;

end

end

// Output logic

assign out = (state == ON);

endmodule

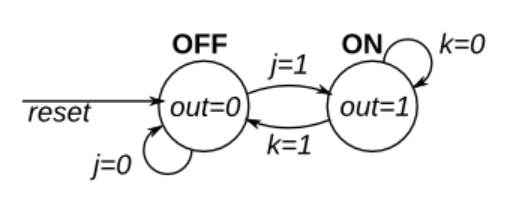

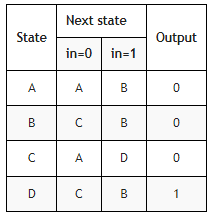

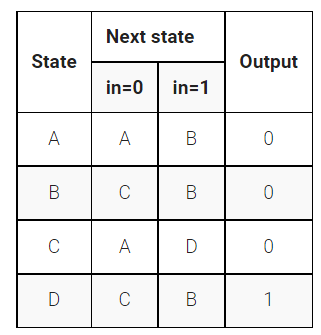

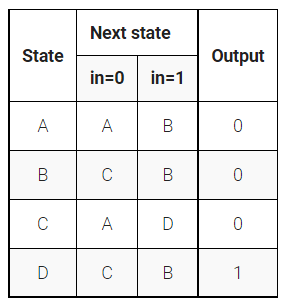

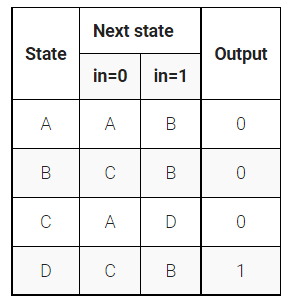

状态转换(Fsm3comb)

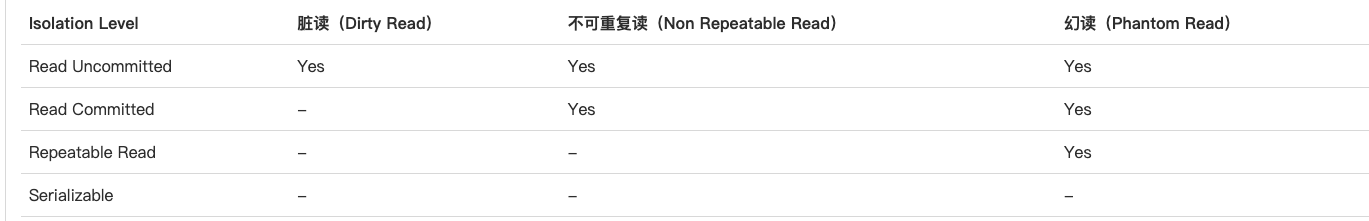

以下是具有一个输入、一个输出和四个状态的 Moore 状态机的状态转换表。使用以下状态编码:A=2’b00、B=2’b01、C=2’b10、D=2’b11。

仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。给定当前状态 ,根据状态转换表计算和输出。

模块声明

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out

);

答案

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: next_state = f(state, in)

always @(*) begin

case (state)

A: next_state = (in=='b1)? B:A;

B: next_state = (in=='b1)? B:C;

C: next_state = (in=='b1)? D:A;

D: next_state = (in=='b1)? B:C;

endcase

end

// Output logic: out = f(state) for a Moore state machine

assign out = (state==D);

endmodule

简单独热状态转换(Fsm3onehot)

以下是具有一个输入、一个输出和四个状态的 Moore 状态机的状态转换表。使用以下独热状态编码:A=4’b0001、B=4’b0010、C=4’b0100、D=4’b1000。

通过假设独热编码的检查来导出状态转换和输出逻辑方程。仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。(测试平台将使用非一个热输入进行测试,以确保您不会尝试做更复杂的事情)。

模块声明

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out);

答案

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = (!in)&&(state[A]||state[C]);

assign next_state[B] = in&&(state[A]||state[B]||state[D]);

assign next_state[C] = (!in)&&(state[B]||state[D]);

assign next_state[D] = in&&state[C];

// Output logic:

assign out = (state[D]=='b1);

endmodule

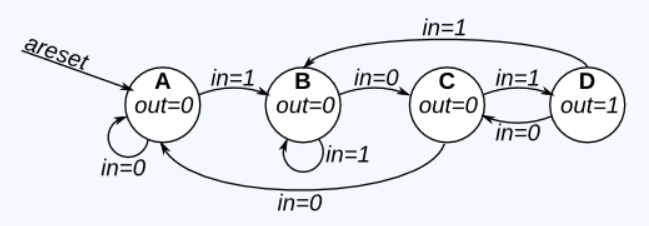

简单摩尔状态机5(Fsm3)

以下是具有一个输入、一个输出和四个状态的 Moore 状态机的状态转换表。实现此状态机。包括将 FSM 重置为状态 A 的异步复位。

模块声明

module top_module(

input clk,

input in,

input areset,

output out);

答案

根据状态转移表可以绘制状态转移图,根据状态转移图编写状态机代码。

module top_module(

input clk,

input in,

input areset,

output out); //

//parameter define

parameter N=2,

A=0,

B=1,

C=2,

D=3;

//初始化寄存器

reg [N-1:0]state_c;

reg [N-1:0]state_n;

//同步时序always模块,格式化描述次态寄存器迁移到现态寄存器

always @(posedge clk or posedge areset)begin

if(areset)begin

state_c <= A;

end

else begin

state_c <= state_n;

end

end

//组合逻辑always模块,描述状态转移条件判断

always@(*)begin

case(state_c)

A:

if(in==1)

state_n = B;

else

state_n = state_c;

B:

if(in==0)

state_n = C;

else

state_n = state_c;

C:

if(in==1)

state_n = D;

else

state_n = A;

D:

if(in==1)

state_n = B;

else

state_n = C;

endcase

end

// Output logic

assign out = (state_c==D);

endmodule

简单摩尔状态机6(Fsm3s)

以下是具有一个输入、一个输出和四个状态的 Moore 状态机的状态转换表。实现此状态机。包括将 FSM 重置为状态 A 的同步复位,这题与上题 的问题相同,但具有同步复位。

模块声明

module top_module(

input clk,

input in,

input reset,

output out);

答案

module top_module(

input clk,

input in,

input reset,

output out); //

//parameter define

parameter N=2,

A=0,

B=1,

C=2,

D=3;

//初始化寄存器

reg [N-1:0]state_c;

reg [N-1:0]state_n;

//同步时序always模块,格式化描述次态寄存器迁移到现态寄存器

always @(posedge clk)begin

if(reset=='b1)begin

state_c <= A;

end

else begin

state_c <= state_n;

end

end

//组合逻辑always模块,描述状态转移条件判断

always@(*)begin

case(state_c)

A:

if(in==1)

state_n = B;

else

state_n = state_c;

B:

if(in==0)

state_n = C;

else

state_n = state_c;

C:

if(in==1)

state_n = D;

else

state_n = A;

D:

if(in==1)

state_n = B;

else

state_n = C;

endcase

end

// Output logic

assign out = (state_c==D);

endmodule