什么是语言模板?

不论是Xilinx的Vivado,还是Altera的Quartus II,都为开发者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原语、XDC约束等相关的语言模板(Language Templates)。

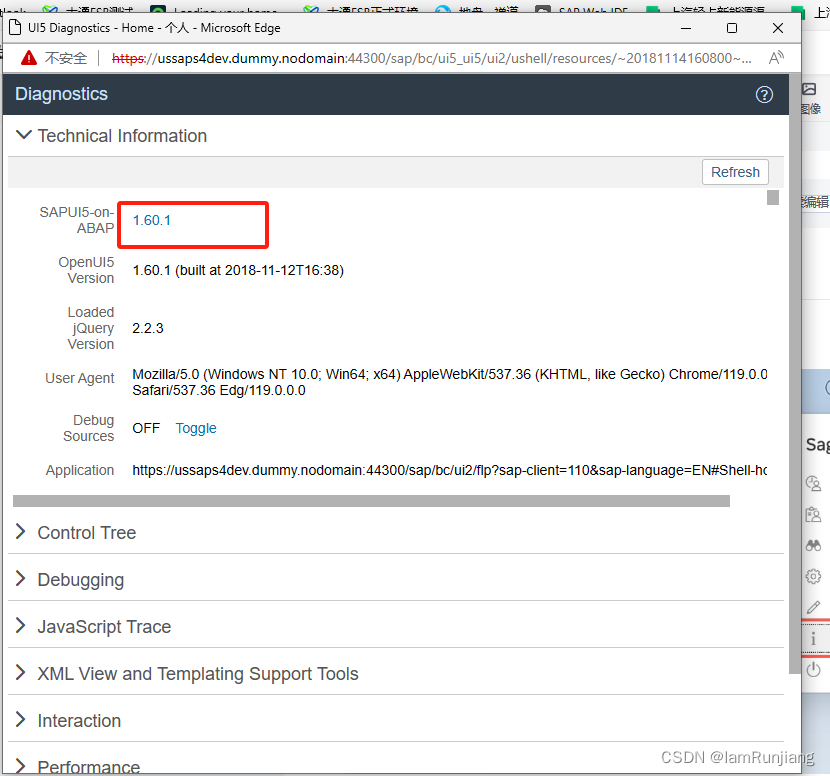

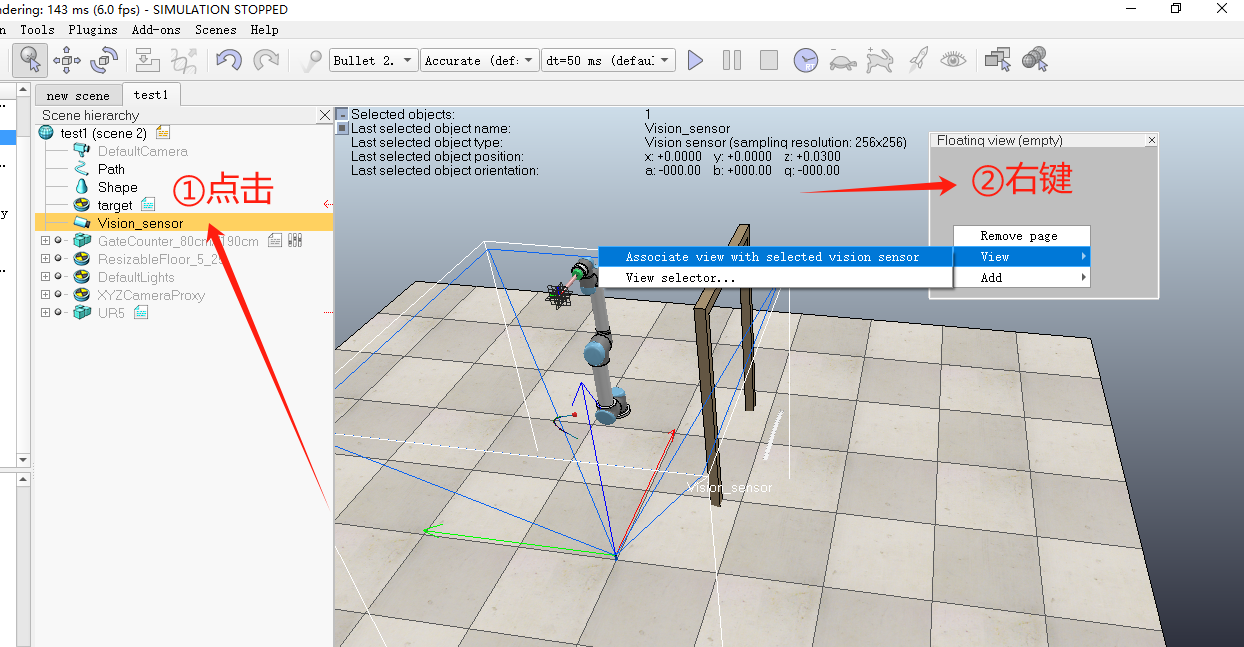

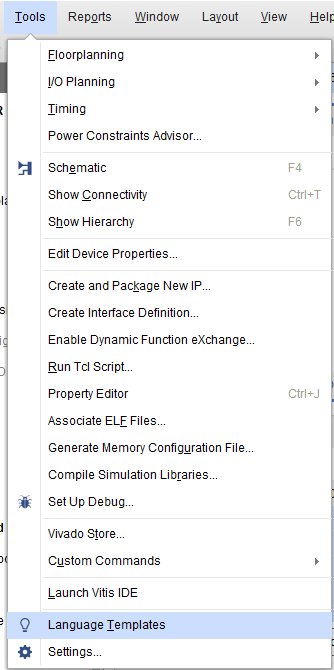

在Vivado软件中,按顺序点击Tools----Language Templates,即可打开设计模板界面。

在Quartus II软件中,需要设计文件(.v文件等)的需要处点击右键,然后点击Inset Templates,即可打开模板界面。

设计模板有什么用?

语言模板的内容还是非常丰富的,比如你可以看看xilinx推荐的文件头是什么样的:

// Company: <Company Name>

// Engineer: <Engineer Name>

//

// Create Date: <date>

// Design Name: <name_of_top-level_design>

// Module Name: <name_of_this_module>

// Target Device: <target device>

// Tool versions: <tool_versions>

// Description:

// <Description here>

// Dependencies:

// <Dependencies here>

// Revision:

// <Code_revision_information>

// Additional Comments:

// <Additional_comments>

学一学(或者重温下)Verilog语法(逻辑运算符):

// The following logical operators are used in conditional TRUE/FALSE statements

// such as an if statement in order to specify the condition for the operation.

//

// ! .... Not True

// && ... Both Inputs True

// || ... Either Input True

// == ... Inputs Equal

// === .. Inputs Equal including X and Z (simulation only)

// != ... Inputs Not Equal

// !== .. Inputs Not Equal including X and Z (simulation only)

// < .... Less-than

// <= ... Less-than or Equal

// > .... Greater-than

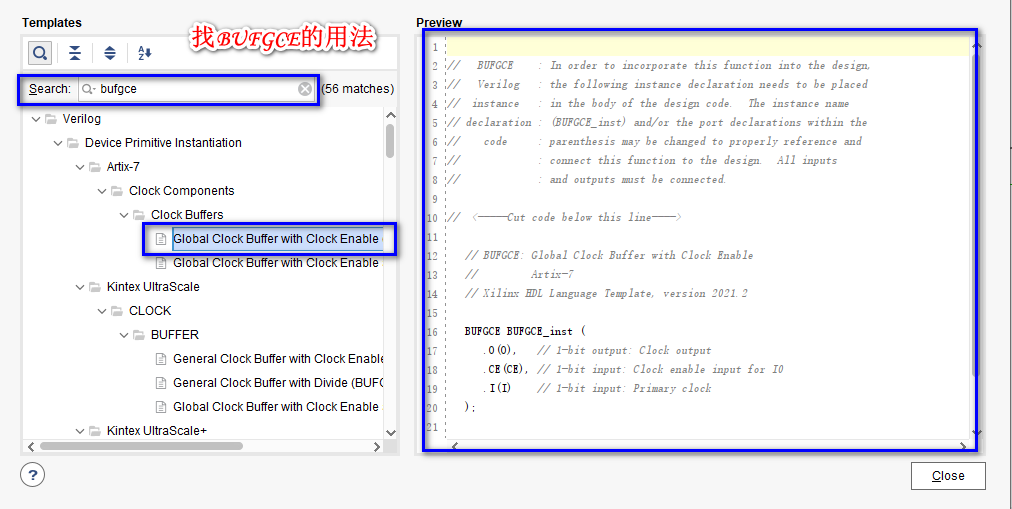

// >= ... Greater-than or Equal找不到原语使用方式的时候,也可以来这里查找(当然你也可以查xilinx的官方文档):

有些时序约束语法不太好记,你可以用这个工具查找,比如:

# Set two clocks as asynchronous

set_clock_groups -asynchronous -group <clock_name_1> -group <clock_name_2>看看xililnx提供的宏XPM(Xilinx Parameterized Macro)是怎么用的,比如CDC这部分的:

// xpm_cdc_async_rst: Asynchronous Reset Synchronizer

// Xilinx Parameterized Macro, version 2023.2

xpm_cdc_async_rst #(

.DEST_SYNC_FF(4), // DECIMAL; range: 2-10

.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values

.RST_ACTIVE_HIGH(0) // DECIMAL; 0=active low reset, 1=active high reset

)

xpm_cdc_async_rst_inst (

.dest_arst(dest_arst), // 1-bit output: src_arst asynchronous reset signal synchronized to destination

// clock domain. This output is registered. NOTE: Signal asserts asynchronously

// but deasserts synchronously to dest_clk. Width of the reset signal is at least

// (DEST_SYNC_FF*dest_clk) period.

.dest_clk(dest_clk), // 1-bit input: Destination clock.

.src_arst(src_arst) // 1-bit input: Source asynchronous reset signal.

);

// End of xpm_cdc_async_rst_inst instantiation最最重要的一点是,它提供了很多典型电路的设计方法。

由于各家FPGA的结构差异,可能相同的代码在不同的器件上生成的结构会存在很大差异。比如有时候,可能你想设计的是一个分布式DRAM,但是由于你的代码风格和综合工具的原因,它给你生成的事BRAM,那这样就和你的设计初衷相违背了(当然随着综合工具的发展,这类情况是越来越少了)。所以在设计相关电路时,请尽量参考xilinx提供的代码,以确保vivado能正确生成你想要的电路(Altera 的FPGA类似)。

parameter RAM_WIDTH = <ram_width>;

parameter RAM_ADDR_BITS = <ram_addr_bits>;

(* ram_style="distributed" *)

reg [RAM_WIDTH-1:0] <ram_name> [(2**RAM_ADDR_BITS)-1:0];

wire [RAM_WIDTH-1:0] <output_data>;

<reg_or_wire> [RAM_ADDR_BITS-1:0] <read_address>, <write_address>;

<reg_or_wire> [RAM_WIDTH-1:0] <input_data>;

always @(posedge <clock>)

if (<write_enable>)

<ram_name>[<write_address>] <= <input_data>;

assign <output_data> = <ram_name>[<read_address>];总结

- 语言模板可以学习HDL语言语法、综合属性等

- 语言模板可以快速查找设计内容、模板

- 语言模板提供的电路设计模板可以保证综合工具能正确推断出对应的电路

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!