对于字扩展与位扩展的解释:

计算机原理中的字,位扩展,都给老子进来学,看不懂算我输!

如果主存的容量无法满足 CPU 的需求,可以通过存储器扩展来解决,扩展的方式有两种:

主存的位数不够(相当于快递柜的尺寸太小,放不下大包裹),则可以通过位扩展的方式(快递柜扩容)实现;

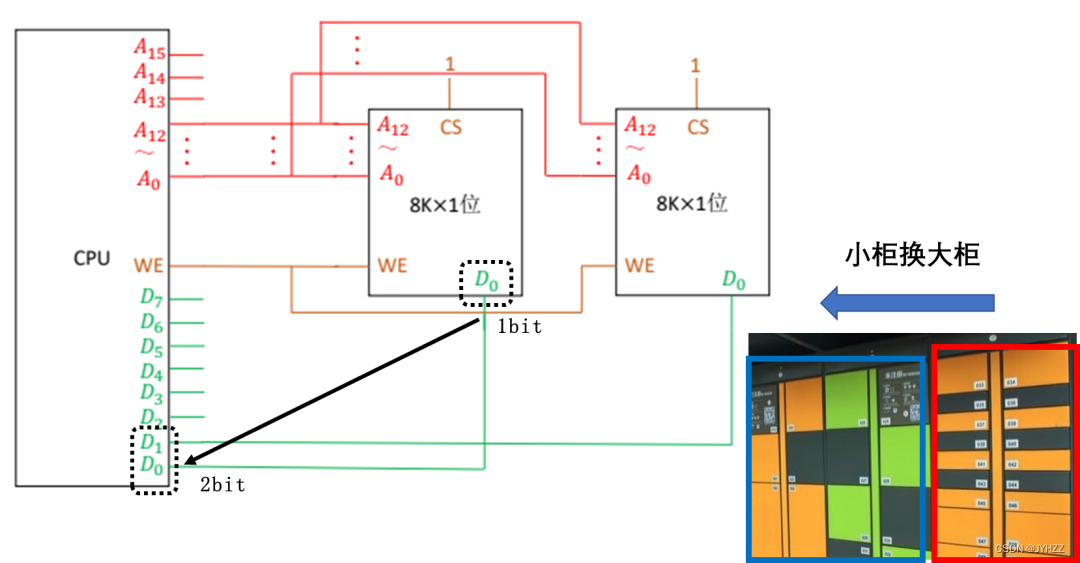

下图是用两片8K*1位的芯片扩充为8K*2位的。其中A0——A15代表地址线,D0——D7代表数据线。

1K=2^10 8=2^3 所以8K=2^13 所以用A0——A12作为芯片的数据线

由1位扩展为2位,所以是数据位数扩展。原来1位只能表示0或1,现在用D0与D1的组合可以表示00,01,10,11。 主存的字数不够(存储单元的数目不够,相当于快递柜数目太少,放不了太多包裹),则可以通过字扩展的方式实现。

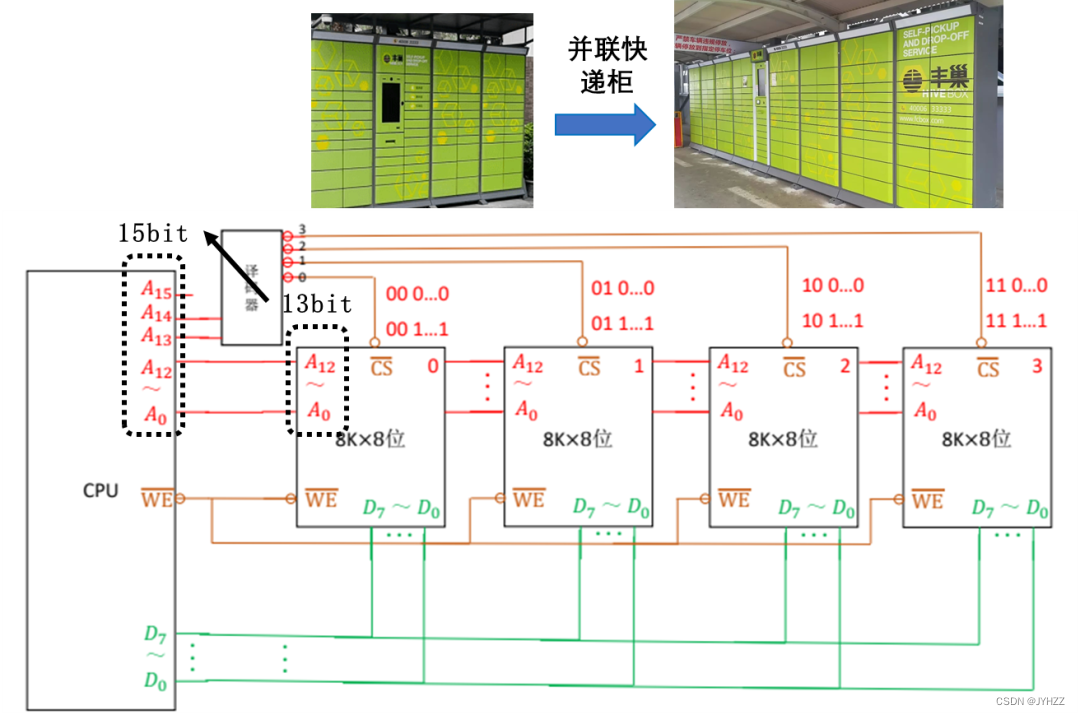

主存的字数不够(存储单元的数目不够,相当于快递柜数目太少,放不了太多包裹),则可以通过字扩展的方式实现。

下图是用四片8K*8位的芯片扩充为32K*8位的。其中A0——A15代表地址线,D0——D7代表数据线。

32K=2^15而8K只需要2^13,所以剩下的A14与A15通过译码器来用于确定选取那个芯片。

译码器有四个输出,分别为00,01,10,11。代表这四个芯片。

1. 在一个容量为128KB的SRAM存储器芯片上,按字长32位编址,其地址范围可从0000H到7fffH。

位(bit)、字节(byte)、字符、编码之间的关系

1KB=1024字节=2^10字节

1字节=8位

所以128KB=128*1024*8位=2^20位

一个数据占32=2^5位,所以总共可以存储2^20/2^5=2^15位,15位全为1就是7fffH

2. 某存储器容量为 64KB,按字节编址,地址 4000H~5FFFH 位 ROM 区,其余为 RAM 区。若采用 8K×4 位的 SRAM 芯片进行设计,则需要该芯片的数量是( C )

A. 7 B. 8 C. 14 D. 16

题干中是按字节编址,也就是说一个数据占一个字节。在题1中,是按字长32位编址,也就是一个数据占4个字节。

然后题干:地址 4000H~5FFFH 位 ROM 区,也就是ROM区有5FFFH - 4000H + 1个可以存放数据的区域。

5FFFH - 4000H + 1 = 2000H = 10 0000 0000 0000 = B = 8KB

所以RAM区占64-8=56KB,又因为一个数据占一个字节,一个字节=8位,所以转化为:

8K*4位的芯片扩展为56K*8位,所以需要(56/8)*(8/4)=14个

3. 某计算机主存容量为 64KB,其中 ROM 区为 4KB,其余为 RAM 区,按字节编址。现要用 2K×8 位的 ROM 芯片和 4K×4 位的 RAM 芯片来设计该存储器,则需要上述规格的 ROM 芯片数和 RAM 芯片数分别是( D )。

A. 1,15 B. 2,15 C. 1,30 D. 2,30

2K*8位的芯片扩展为4K*8位,所以需要2个

4K*4位的芯片扩展为60K*8位,所以需要30个

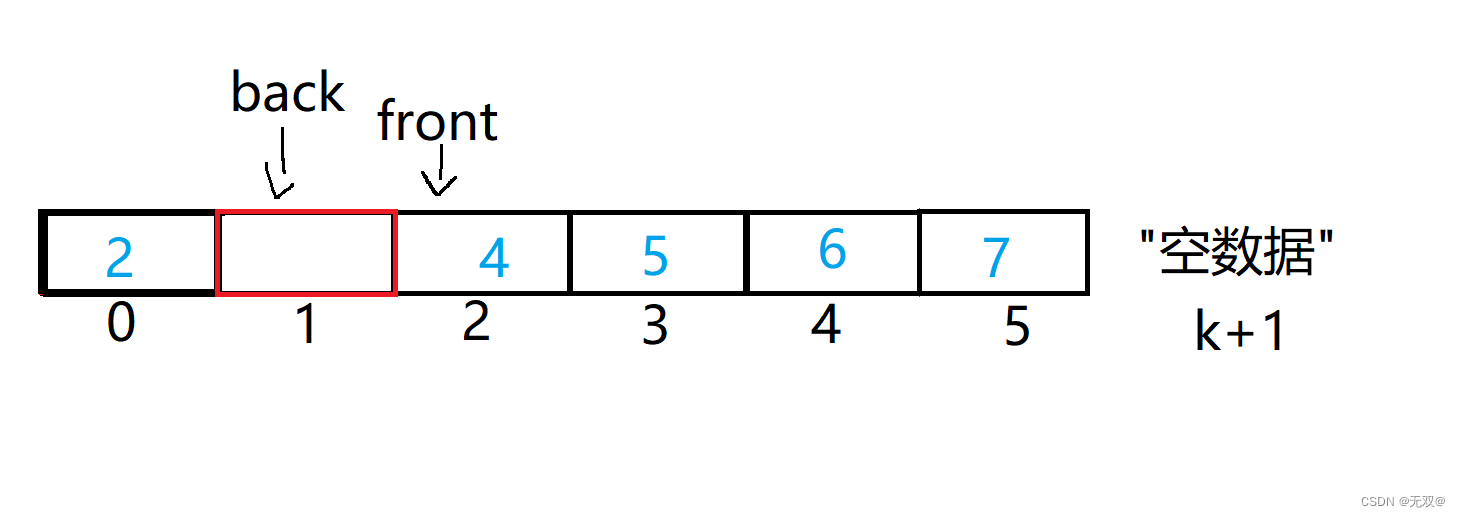

8. 假定用若干个 2K x 4 位芯片组成一个 8K x 8位存储器,则 0B1FH 所在芯片的最小地址

是 ( D )

A. 0000H B. 0600H C. 0700H D. 0800H

用8个2K x 4 位芯片组成一个 8K x 8位存储器

其中两个2K x 4 位芯片组成一个2K x 8位芯片,即位扩展(图中的芯片不对,但是大致意思是一样的)

四组这样的组成一个 8K x 8位存储器(图中的芯片不对,但是大致意思是一样的)

题干中0B1FH=0 1011 0001 1111,代表地址线

8K=2^13,所以有13根地址线。2K=2^11,所以其中11根用于连接芯片,2根用于输出组选信号。(图中A11,A10两个二进制数可以有00,01,10,11四种情况,对应了四组芯片(每组有两个芯片)组成的八位存储器。即00代表选第一组,01选第二组。。。。。)

所以0 1011 0001 1111的高两位是片选信号01,所以选第二组。

然后看0 1011 0001 1111的的第三位0,也就是图中的A9,他负责选每组中的哪个芯片,0为组中的第1个,1为第二个。

整体看一下:

若有八个的话就要有A12,A11,A10三个二进制数000,001,010,011,100,101,110,111来代表八组二个芯片组成的八位存储器。

所以选的是第二组的第一个芯片,即 010 00 0000 0000 ,转换为16进制为0800H

第一组的起始地址: 000 00 0000 0000 - 001 11 1111 1111

第二组的起始地址: 010 00 0000 0000 - 011 11 1111 1111

第三组的起始地址: 100 00 0000 0000 - 101 11 1111 1111

第四组的起始地址: 110 00 0000 0000 - 111 11 1111 1111