目录

- DAC

- 15.1 Introduction

- 15.1.1 Features

- 15.1.2 Block Diagram

- 15.2 Using the DAC

- 15.2.1 Initialization Sequence 初始化顺序

- 15.2.2 DAC Offset AdjustmentDAC偏移调整

- 15.2.3 EPWMSYNCPER Signal EPWMSYNCPER信号

- 15.3 Lock Registers

- 总结

- 代码配置 driverlib

- 代码配置 bitfield

DAC

缓冲数模转换器(DAC)是一个模拟模块,可以输出可编程的任意参考电压。

开发过程中,虽然CCS的在线仿真能够让我们观察大多数关键变量的值以调试,但在线仿真的更新频率不算太高,最大也就50Hz。感觉CCS自带的示波器也不怎么好用。

280049C芯片集成有DAC模块,可以将程序当中的某些关键变量进行输出出来,

15.1 Introduction

缓冲DAC模块由一个内部12位DAC和一个能够驱动外部负载的模拟输出缓冲器组成。为了驱动比典型负载更高的负载,可以在负载大小和输出电压稳定性之间进行权衡。有关缓冲DAC的负载条件,请参阅设备特定数据手册。缓冲DAC是一种通用DAC,除交流波形(如正弦波、方波、三角波等)外,还可用于生成直流电压。软件写入DAC值寄存器可以立即生效,也可以与EPWMSYNCPER事件同步

15.1.1 Features

每个DAC的特性具有以下特点:

- 12位可编程的内部DAC

- 可选择的参考电压源

- 使用内部VREFHI时的具有1倍和2倍的增益模式

- 能够与EPWMSYNCPER同步

15.1.2 Block Diagram

15.2 Using the DAC

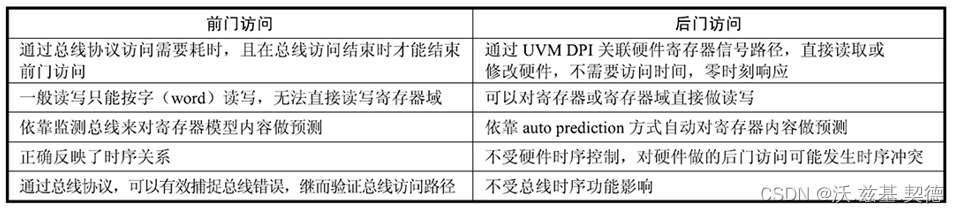

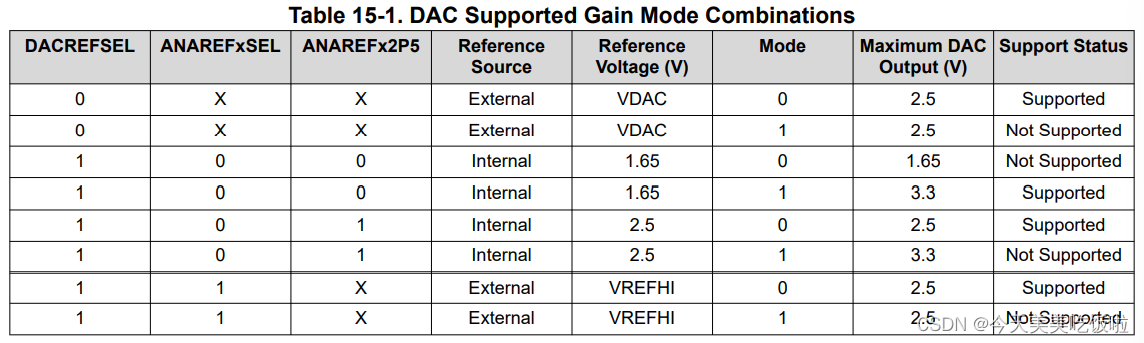

内部DAC的参考电压源DACREF可在VDAC和VREFHI之间选择。仅当VREFHI设置为DACREF且使用内部参考模式时,x2增益模式才可用(请参阅模拟子系统章节,了解如何切换到内部参考模式)。即使缓冲DAC具有x2增益模式,缓冲DAC的最大输出电压也不会大于VDDA。表15-1列出了缓冲DAC支持的增益模式组合。在此表中,x=A或B,x=无需在意,VDAC/VREFHI=2.5v,VDDA=3.3v,DACVAL=4095。

缓冲DAC模块中有两组DACVAL寄存器,DACVALA和DACVALS。DACVALA是一个只读寄存器,它主动控制缓冲的DAC值。DACVALS是一个可写的影子寄存器,可以立即加载到DACVALA中,也可以与下一个EPWMSYNCPER事件同步。如果在缓冲DAC输出电压时禁用到DAC的时钟,输出电压保持不受影响,但DACVALA和DACVALS将不再通过寄存器写入进行更新。启用缓冲DAC的时钟可将其恢复到禁用时钟之前的状态。

内部DAC的理想输出通过以下公式计算

D A C O U T = D A C V A L A × D A C R E F 4096 DACOUT = \frac{DACVALA\times DACREF}{4096} DACOUT=4096DACVALA×DACREF

缓冲DAC可用于对PGA的输入信号进行电平移位(详见PGA部分)。缓冲DAC的输出缓冲器在电源轨(VDDA/VSSA)附近可能表现出非线性行为。要确定缓冲DAC的线性范围,请参阅设备特定数据手册。

根据理想输出可知,DAC的输出电压与参考电压相关,但DAC的输出电压不会大于VDDA,因此在编程中想要使用DAC模块以DA某个变量时,一定要注意实际输出的电压,谨防被限幅。

15.2.1 Initialization Sequence 初始化顺序

- 启用缓冲DAC时钟。

- 使用DACREFSEL寄存器以设置DACREF参考电压。

- 使用DACOUTEN寄存器为缓冲DAC使能输出。

- 在输出电压之前等待通电时间过去。要确定缓冲DAC的通电时间,请参阅设备数据手册。

- 对于缓冲DAC的可预测行为,可以根据缓冲DAC的稳定时间来间隔对DACVALS的连续写入。要确定缓冲DAC的稳定时间,请参阅设备数据手册。

15.2.2 DAC Offset AdjustmentDAC偏移调整

零偏移误差定义为中间码(2048)处的电压与1.25v(对于2.5v参考电压)之间的差值。DAC偏移误差在2.5v参考电压下校准,并作为Device_cal()函数的一部分加载到DAC偏移微调寄存器中。如果DAC在2.5v以外的任何参考电压下使用,则必须调整偏移微调,以确保偏移误差性能保持在设备特定的数据手册限制范围内。DAC偏移寄存器是一个16位寄存器,在寄存器的下半部分包含8位有符号偏移微调。使用C2000Ware中的函数调用DAC_tuneOffsetTrim()调整偏移。

15.2.3 EPWMSYNCPER Signal EPWMSYNCPER信号

EPWMSYNCPER来自EPWM的时基子模块。有关如何生成此信号的详细说明,请参阅增强型脉宽调制器(ePWM)一章的时基子模块部分。

当DACCTL[LOADMODE]=1时加载DACVALA的EPWMSYNCPER信号是电平触发加载。如果EPWM的TBCTR和TBPRD均为0,则EPWMSYNCPER将保持在高电平,DACVALA将立即从DACVALS加载,而不管DACCTL[LOADMODE]的值是多少。因此,建议在将DACCTL[LOADMODE]设置为1之前先配置EPWM。

15.3 Lock Registers

提供了DACLOCK寄存器,以防止伪写入修改DACCTL、DACVALS和DACUUTEN寄存器。一旦寄存器通过DACLLOCK受到保护,写入访问将被锁定,直到设备复位。

总结

使用DAC模块很简单,只需要配置参考电压,并写入DACVALS寄存器一个数字值即可。参考电压可配置为外部参考VDAC和内部参考电压1.65V和2.5V,并结合增益作为DAC模块最终的参考电压DACREF。

举个例子,配置参考电压为内部参考电压1.65V,增益设置为2,则参考电压DACREF=3.3V,若向DACVALS写入数字值2048,则输出的DAC模块的输出带电压 D A C O U T = D A C V A L S × D A C R E F 4096 = 1.65 V DACOUT=\frac{DACVALS\times DACREF}{4096}=1.65V DACOUT=4096DACVALS×DACREF=1.65V

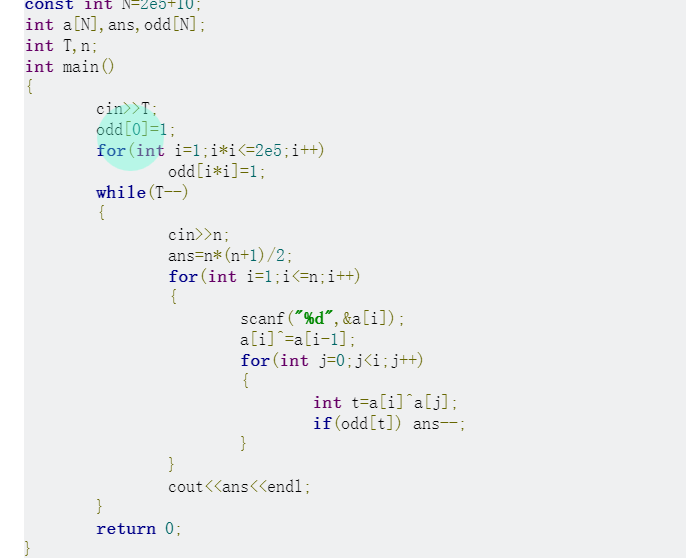

代码配置 driverlib

#define myDAC0_BASE DACA_BASE

void myDAC0_init()

{

//

// Set DAC reference voltage.

//

DAC_setReferenceVoltage(myDAC0_BASE, DAC_REF_ADC_VREFHI);

//

// Set DAC gain mode.

//

DAC_setGainMode(myDAC0_BASE, DAC_GAIN_TWO);

//

// Set DAC load mode.

//

DAC_setLoadMode(myDAC0_BASE, DAC_LOAD_SYSCLK);

//

// Enable the DAC output

//

DAC_enableOutput(myDAC0_BASE);

//

// Set the DAC shadow output

//

DAC_setShadowValue(myDAC0_BASE, 0U);

//

// Delay for buffered DAC to power up.

//

DEVICE_DELAY_US(5000);

}

代码配置 bitfield

void myDACA_init()

{

DacaRegs.DACCTL.bit.DACREFSEL = 1; // select internal VREF

DacaRegs.DACCTL.bit.MODE = 1; // gain is 2

DacaRegs.DACCTL.bit.LOADMODE = 0; // load on the next SYSCLK, irrespective of EPWMSYNCPER signal

DacaRegs.DACOUTEN.bit.DACOUTEN = 1; // enable DAC output

DacaRegs.DACVALS.all = 2048; // DACVALS

}