(一)低功耗isolation cell的目的

低功耗架构设计需要前后端拉通规划,前端设计有PMU功耗管理单元,比如A模块电压常开,B模块电压可关断,那么请思考,当B模块关断电压后,B模块输出到A模块的信号是怎样的驱动力?会造成什么结果?

后果1:

假如电源的工作电源为1.2V,当B模块关断电压后,B模块输出到A模块的信号(X态)可能为0~1.2V中任意电压,如果X处在中间电平0.6V,若这个信号送给电压常开域中的一个反相器,就会导致这个反相器的PMOS和NMOS都导通,就会存在一个短路电流从电源流经PMOS、NMOS再到地,造成功耗浪费。

后果2:

假如电源的工作电源为0~1.2V,那么X态信号可能随着温度、电压等环境因素改变而震荡,导致常开电压模块的逻辑功能出现不可预知的错误,甚至引起系统宕机,造成芯片功能的不可靠,芯片上到汽车、飞机上去后,不堪设想。

因此,当A模块电压常开,B模块电压可关断,在B模块关断电压后,B模块输出到A模块的信号需要用isolation cell进行电压钳位(clamp 0或者clamp 1信号),这样就避免了X态的传播。

也就是说Isolation cell连接的两端分别是power gated domian和always_on_domain,Isolation_cell的作用就是将power gated domian输出到always on domain的信号隔离,以防止power gated domian电源关闭后输入到always on domian的信号出现不确定状态(如X态等)。

(二)低功耗isolation cell的类型

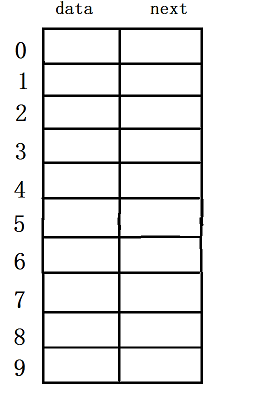

isolation cell一般有sink side、source side两种类型。

什么是sink side?

即isolation cell放置于常开电压域PD_ON,只需要一组电源,推荐使用这种类型,较为简洁。

什么是source side?

即isolation cell放置在power gated domain(PD_SHUT)里面,但是需要接常开电源(VDDG)供电,保证power gated domain(PD_SHUT)的电压关闭后,isolation仍能输出clamp值。这种情况下,isolation cell一般得有两组电源,分别是primary power(VDD)和 backup power(VDDG),当VDD关断后,VDDG就供电,否则isolation谁来供电输出clamp值呢。

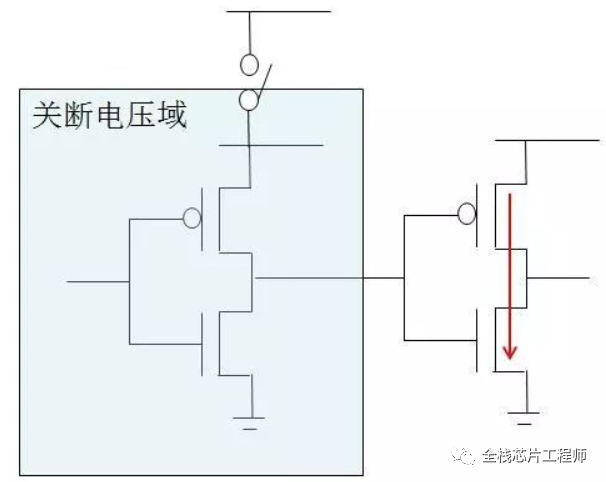

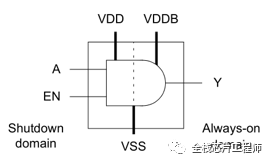

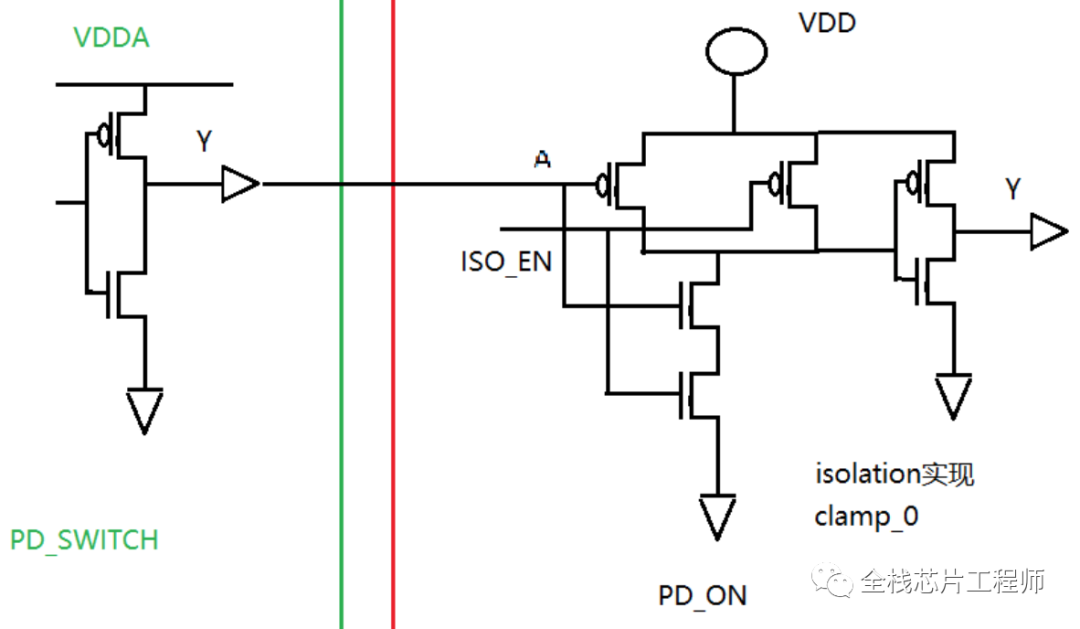

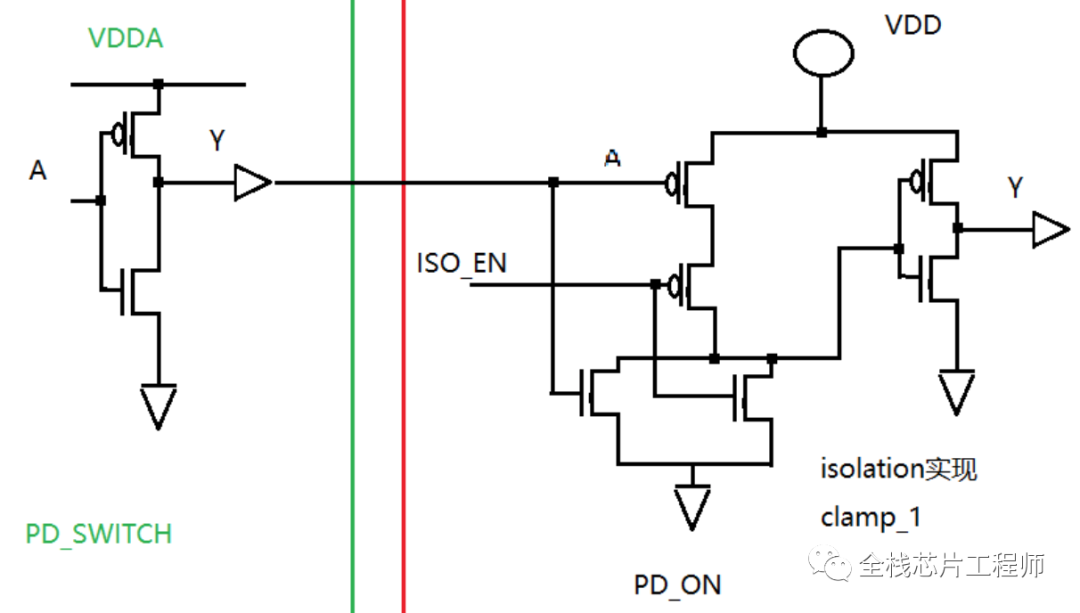

isolation cell的结构(下图为source side isolation类型):

(三)低功耗isolation cell的结构

上面介绍了模块电压关闭之后,其输出需要isolation cell进行钳位的原因,以及isolation cell的两种类型及两组电源的需求,通常isolation cell和Level Shifter一起连用,AND和OR门都可以组成一个isolation cell;

1. AND类型:输出iso成0;

2. OR类型:输出iso成1;

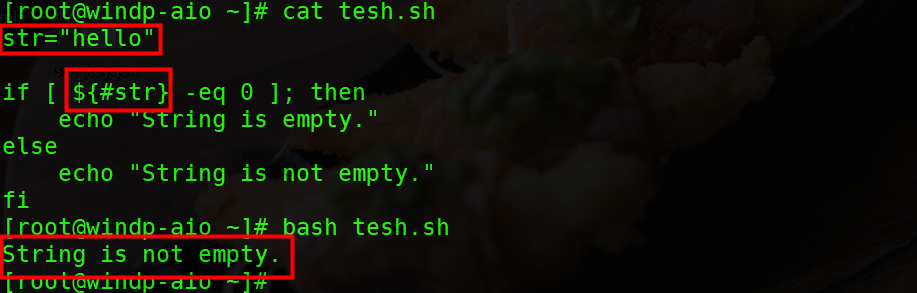

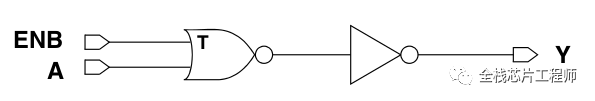

首先看AND类型,EN有效时(置0),输出Y(isolation)=0,请思考下图的类型是source类型还是sink类型?

展开与门电路结构如下图右边部分,请思考,下图Y输出是否和上图一致?ISO_EN是高有效还是低有效?想通了就很有趣!

isolation实现clampe_0功能

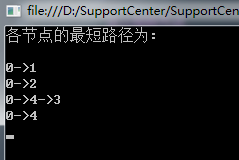

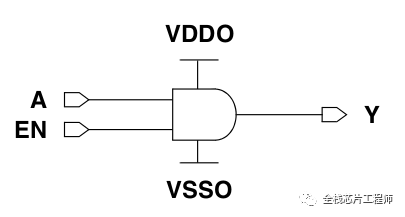

然后我们看OR或门类型:ENB有效,Y就被钳位为1。

或门展开电路如下图右边部分,请思考下图ISO_EN是1有效吗?管子是如何工作才能钳位输出?钳位输出是1吗?是不是很有趣!

综上,通常Isolation cell和Level Shifter一起连用,AND和OR门都可以组成一个isolation cell。Isolation可以放在input端,output端或者第三方Voltage Area中,但是考虑到power-on rail的走线,isolation cell自身的功耗,一般还是放在input端比较好,因为放在input端不需要always-on的power。

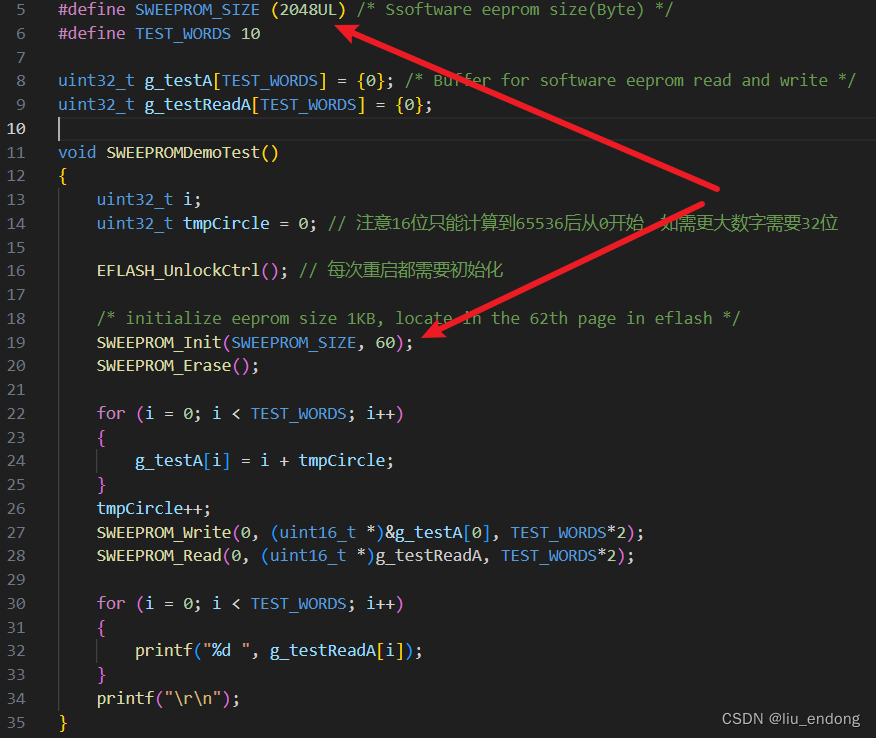

(四)低功耗isolation cell的UPF语法

set_isolation ISO0_PD_SHUT 指定isolation cell的添加rule,相当于前缀名称

-domain PD_SHUT 指定添加isolation cell的voltage area

-applies_to input 指定isolation cell在voltage area的input还是output

-diff_supply_only true 指定cell port上是否允许有其他supply

-loacation parent 指定isolation的放置位置,parent代表放在driver pin的父module

-isolation_signal PMU/iso_en 指定isolation cell的isolation 控制信号

-calmp_value 1 指定isolation cell的输出值

景芯微SoC团队业务

景芯微SoC团队业务介绍:

-

提供SoC、MCU、ISP、CIS等芯片设计服务

-

提供芯片设计、验证、DFT、后端全流程设计服务

-

提供后端设计工艺包括7nm、12nm、28nm、40nm、55nm、65nm、90nm、110nm、180nm等节点,提供极具性价比的投片渠道

景芯SoC训练营,让每个人都能设计一款SoC/MCU芯片!

选拔优秀训练生加入我们的设计外包团队,兼职做项目!

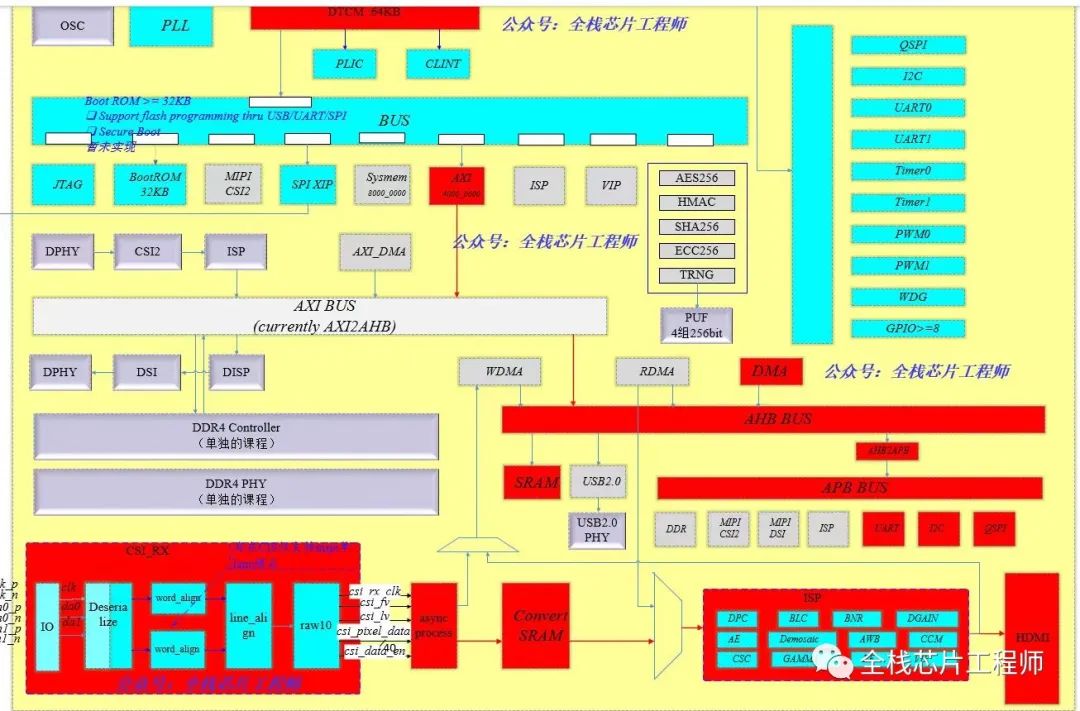

【全网唯一】景芯SoC是一款用于【芯片全流程培训】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

-

CPU: RISC-V

-

ITCM: 64KB

-

DTCM: 64KB

-

外设:MIPI/USB/HDMI/UART/I2C/QSPI

-

系统时钟:100MHz

-

MIPI RX解码

-

ISP图像处理

-

HDMI接口

(一)SoC前端课程,您将学会

-

高速接口的Verilog设计实现

-

图像算法及Verilog设计实现

-

MIPI通信协议的Verilog实现

-

Lint、CDC检查及UVM验证

-

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

(二)SoC中端课程,您将学会

-

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

课程提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容,请联系号主报名,登录服务器实践,工程数据分割为如下三个部分。

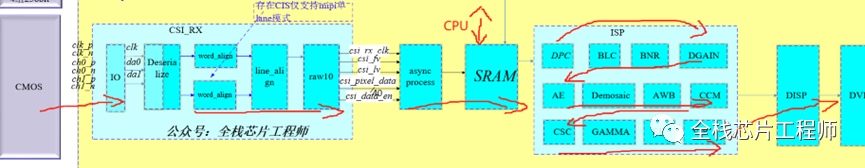

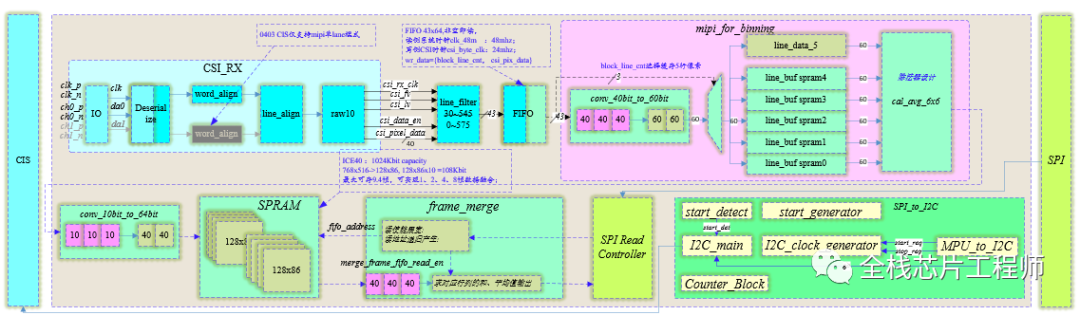

图像处理的数据通路:

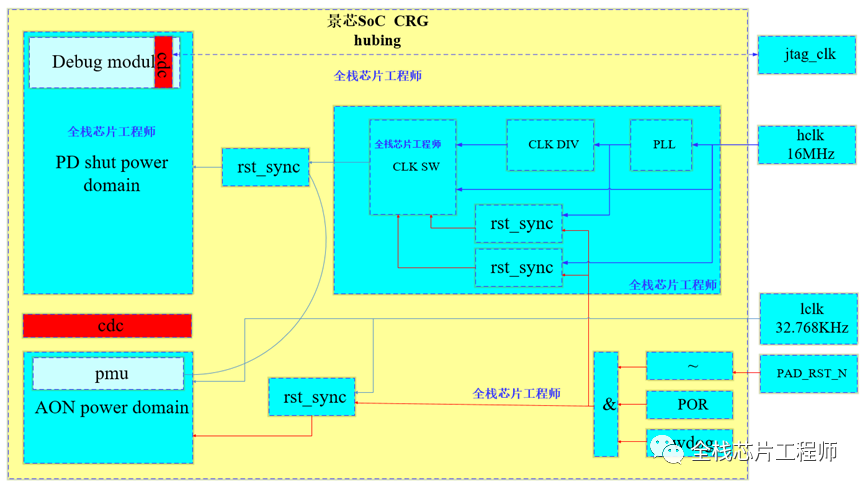

景芯SoC的CRG设计:

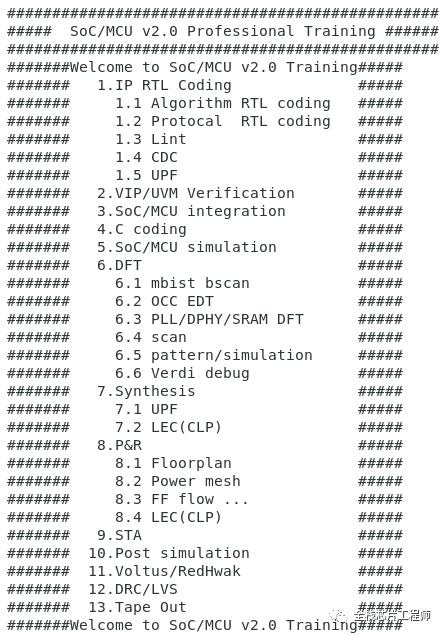

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、STA分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

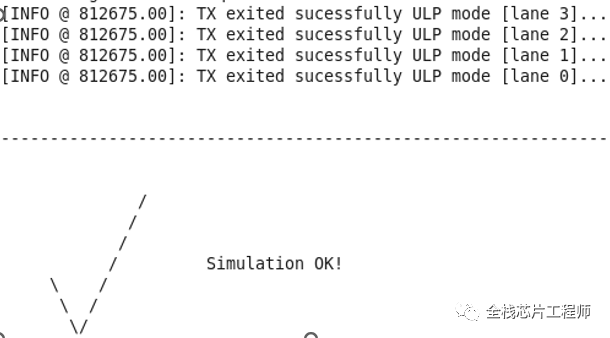

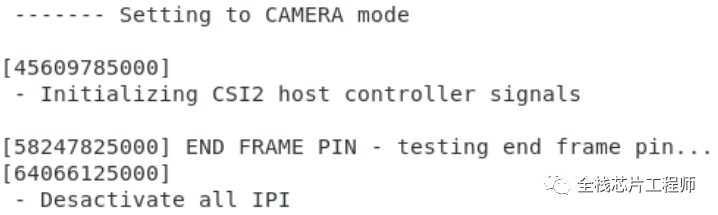

MIPI DPHY+CSI2解码

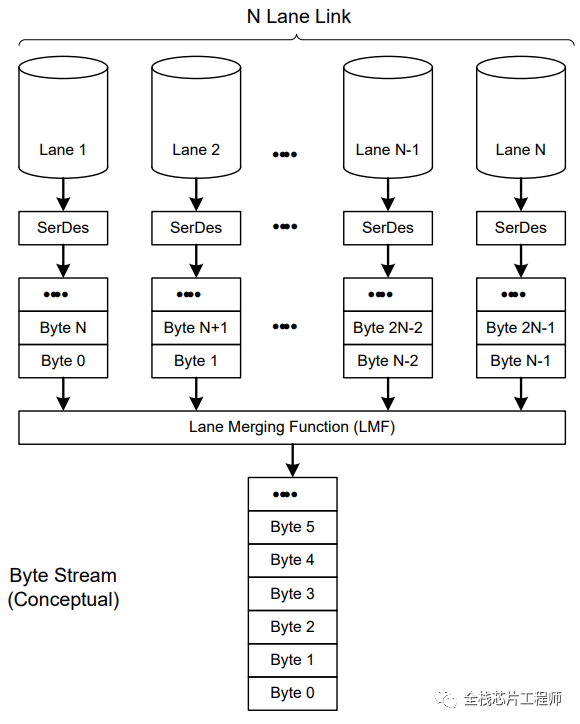

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

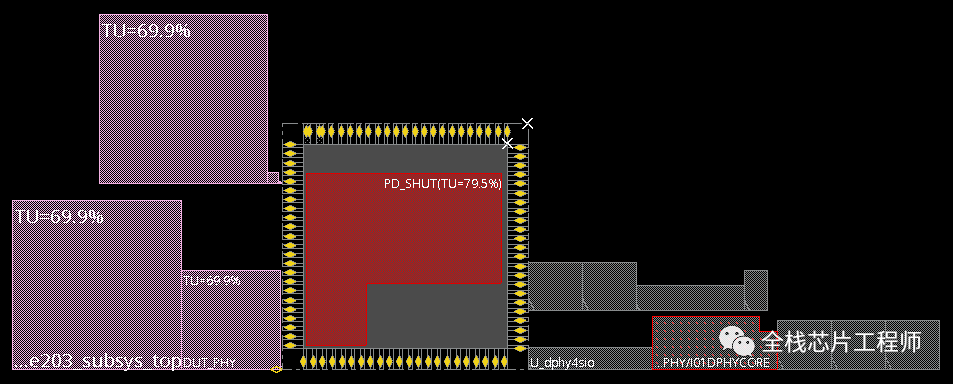

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

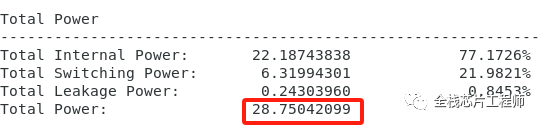

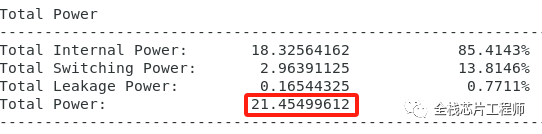

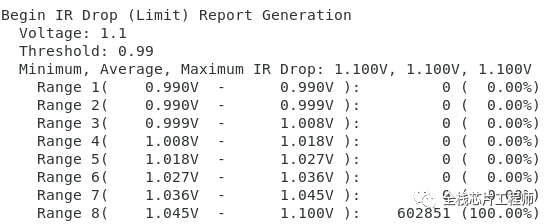

低功耗设计前,功耗为28.75W

低功耗设计后,休眠时,功耗为21.45mW,降低7mW

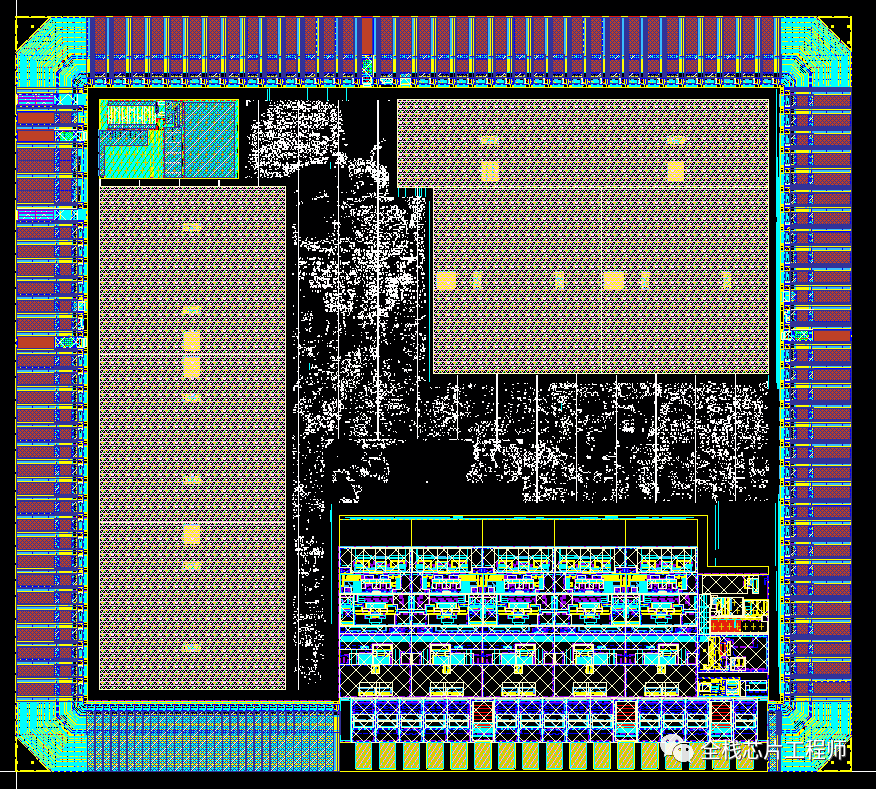

芯片的版图设计V1.0

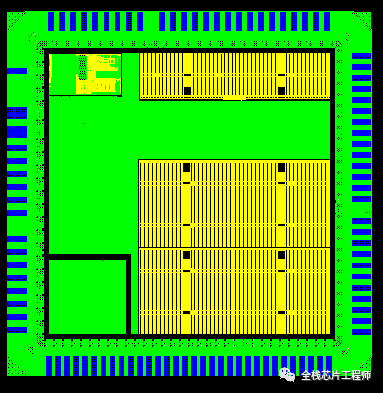

芯片的版图设计V2.0

低功耗设计的DRC/LVS,芯片顶层的LVS非常具有挑战性!业界独一无二的经验分享。

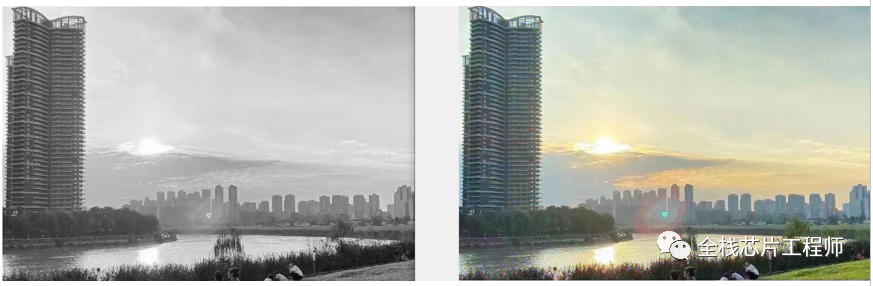

ISP图像处理

-

dpc - 坏点校正

-

blc - 黑电平校正

-

bnr - 拜耳降噪

-

dgain - 数字增益

-

demosaic - 去马赛克

-

wb - 白平衡增益

-

ccm - 色彩校正矩阵

-

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

-

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

-

ee - 边缘增强

-

stat_ae - 自动曝光统计

-

stat_awb - 自动白平衡统计

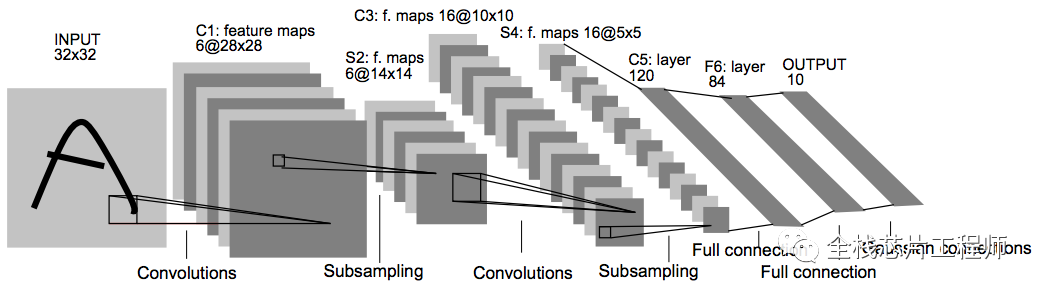

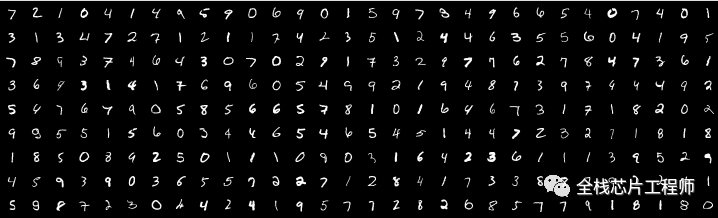

CNN图像识别

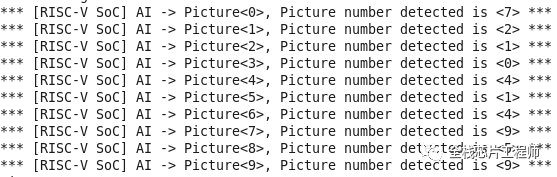

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

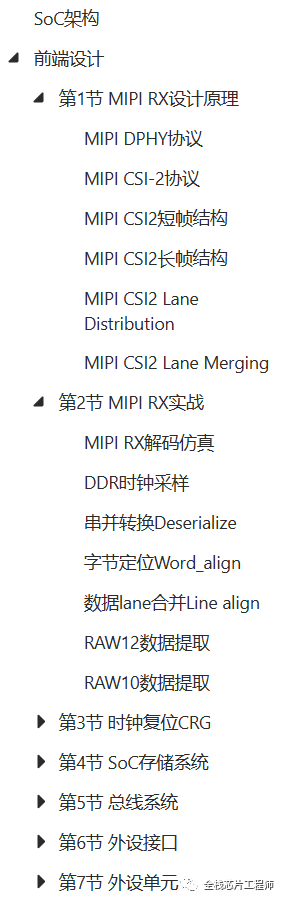

前端设计目录

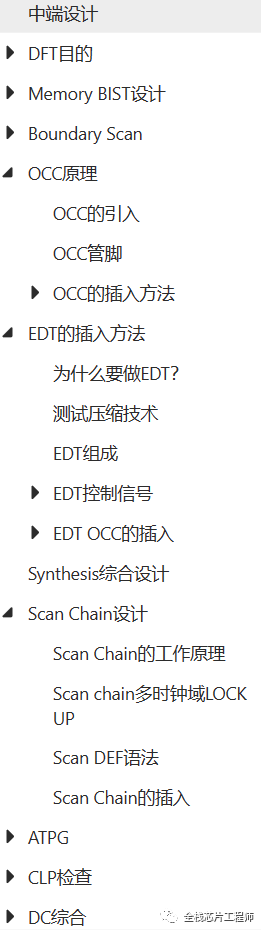

中端设计目录

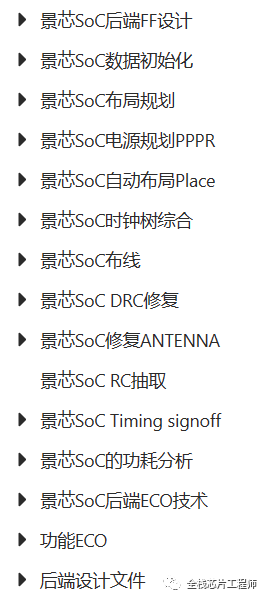

后端设计目录

欢迎加入【全栈芯片工程师】知识星球交流技术,从算法、前端、DFT到后端的全流程设计交流。点击下方图片,加入知识星球!

欢迎加入CIS+ISP技术交流群,先加我微信,我拉你进群!

欢迎加入MCU芯片设计交流群,先加我微信,我拉你进群!