一 初识以太网电路

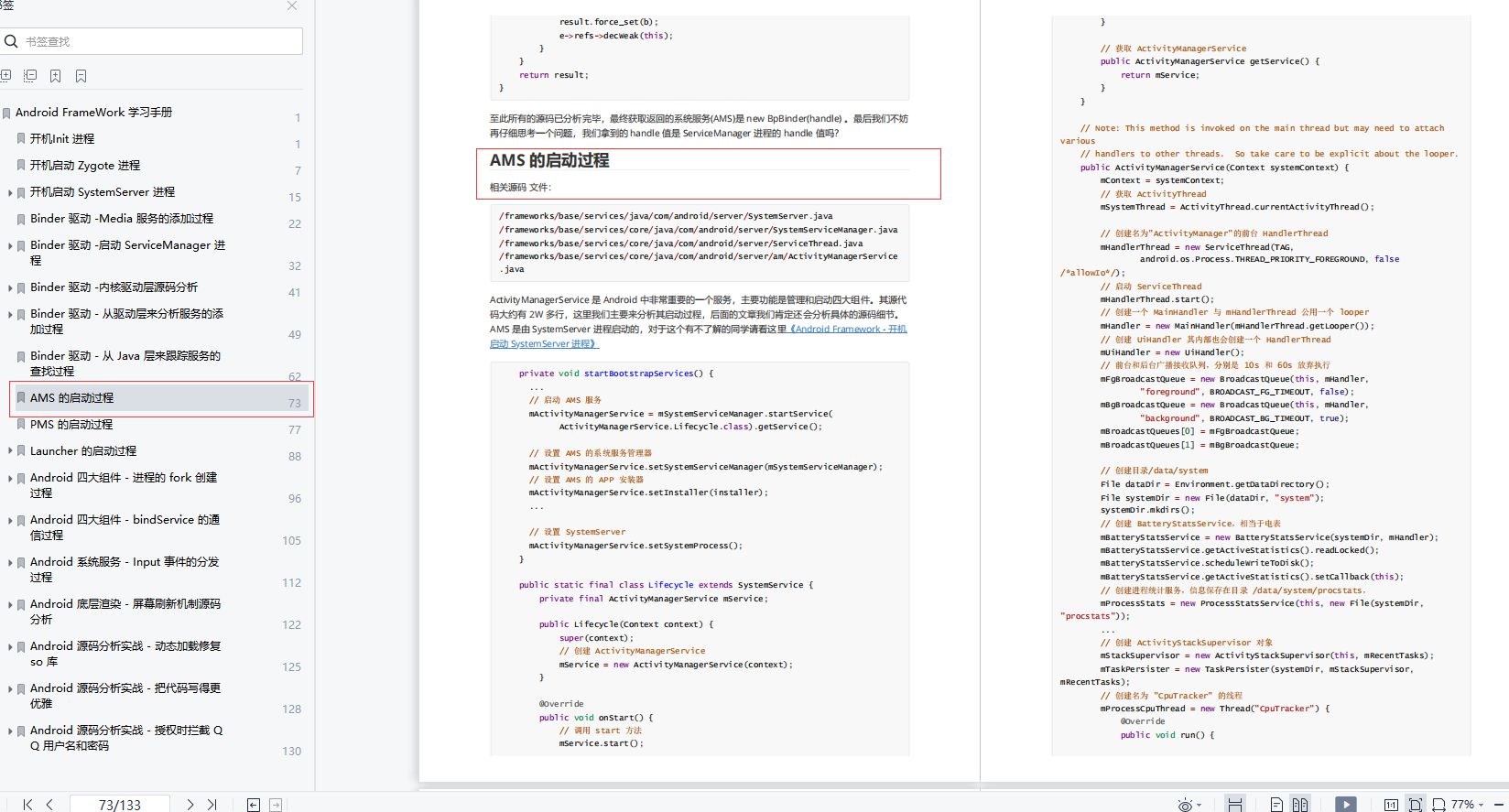

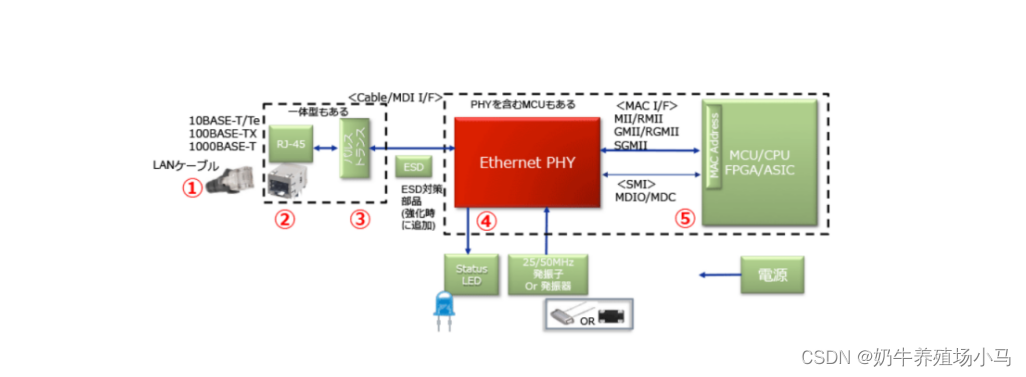

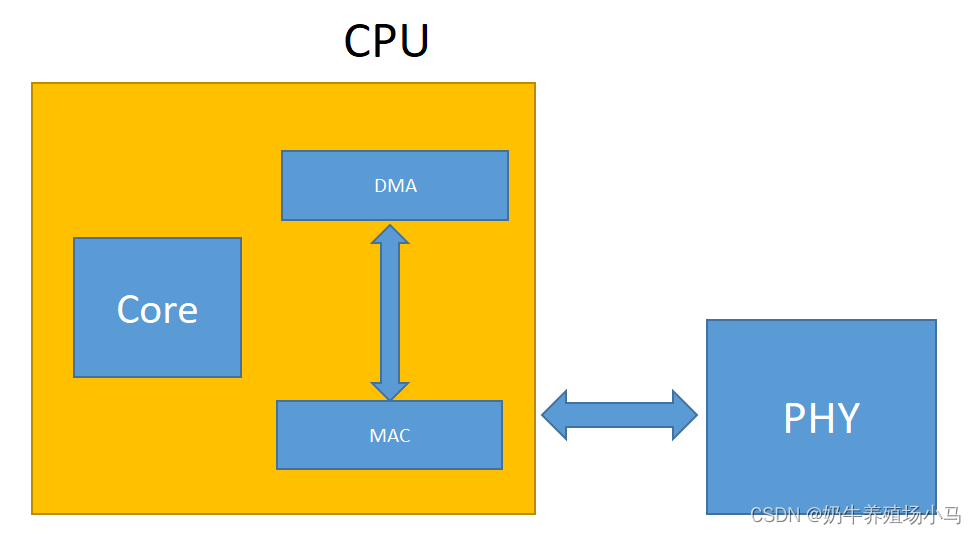

从硬件的角度看,以太网接口电路主要由 MAC(Media Access Control)控制器和物理层接口 PHY(Physical Layer)两大部分构成,一般一个嵌入式终端系统的以太网硬件抽象 如下:

1 网线 它按通信速度分类。

2 RJ-45 以太网连接器。

3 脉冲变压器 它可以防止电流从外部直接流入并保护设备内部的电路。

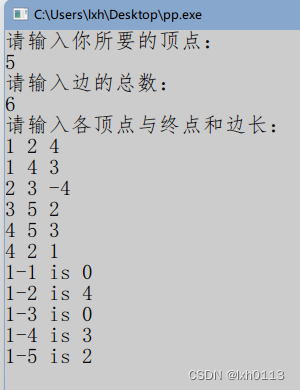

关于 脉冲变压器

当我们的PHY芯片发送数据,接受到MAC层发送过来的数字信号,然后转换成模拟信号,通过MDI接口传输出去。但是我们的网线传输的距离又很长,有时候需要送到100米甚至更远的地址,那么就会导致信号的流失。而且外网线与芯片直接相连的话,电磁感应和静电,也很容易导致芯片的损坏,所以就要使用网络变压器,其主要作用是

3.1 传输数据,它把PHY送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到不同电平的连接网线的另外一端

3.2 隔离网线连接的不同网络设备间的不同电平,以防止不同电压通过网线传输损坏设备

3.3 还能使芯片端与外部隔离,抗干扰能力大大增强,而且对芯片增加了很大的保护作用,保护PHY免遭由于电气失误而引起的损坏(如雷击)

4 物理层PHY:真正用于传输数据(数/模信号转换)

发送 :将MAC下发的数字信号转换为模拟信号发送出去

接收 : 将外部的模拟信号转换为数组信号 上传给MAC

5 太网控制器 MAC:只要用于控制与对方通信(通信控制)

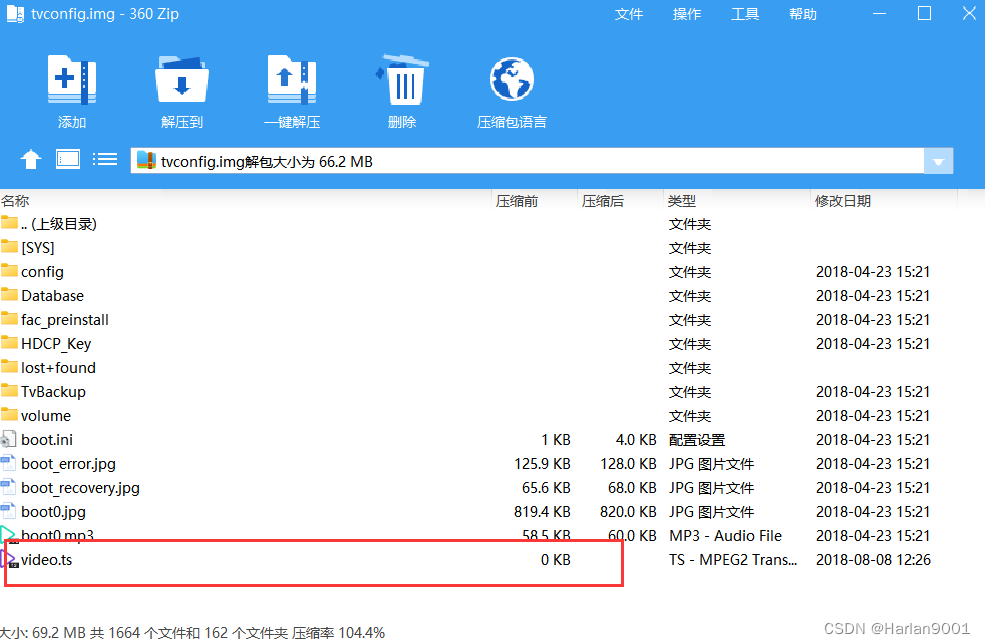

主要有MAC控制器、PHY芯片、网络变压器和RJ45接头组成,有的系统会有DMA控制。一般的系统中CPU和MAC以及DMA控制器都是集成在一块芯片上的,为了节省空间简化设计,很多时候网口的变压器和RJ45的接头集成在一起。

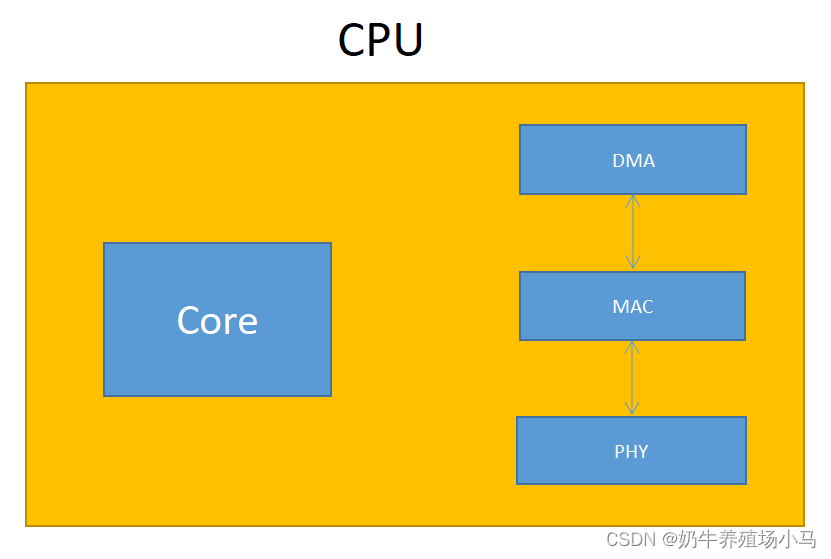

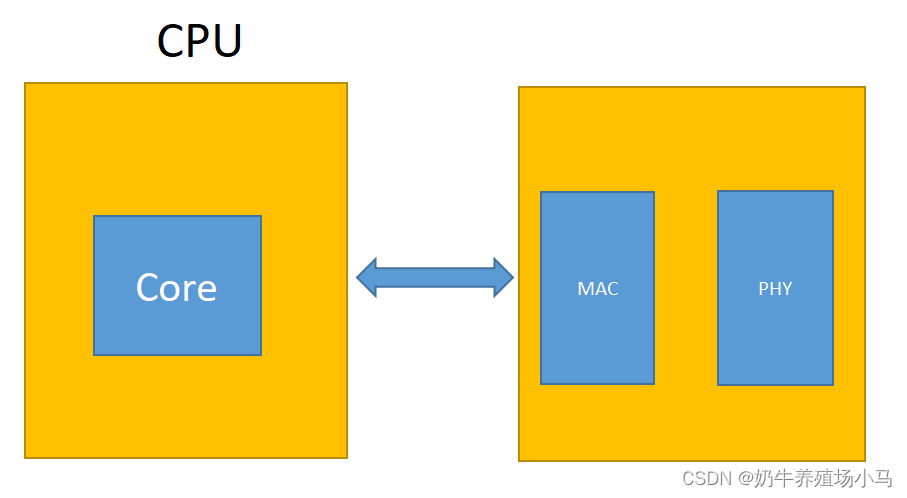

在实际的设计中,由于PHY 整合了大量模拟硬件,而 MAC 则是典型的全数字器件。考虑到芯片面积及模拟/数字混合架构的原因,通常,将 MAC 集成进微控制器而将 PHY 留在片外。更灵活、密度更高的芯片技术已经可以实现 MAC 和 PHY 的单芯片整合。总的来说,可分为下列几种类型:

CPU 集成 MAC 与 PHY,目前来说并不多见。

CPU 集成 MAC,PHY 采用独立芯片,这种比较常见。

CPU 不集成 MAC 与 PHY,MAC 与 PHY 采用集成芯片(形成一个独立的网卡),这种也比较常见。

所以网卡:可以理解成phy 和mac 组成的一个芯片,直接可以通过各种接口和cpu对接

二 MAC控制器

太网控制器,作用是数据控制。

EMAC即百兆网卡,GMAC即千兆网卡,属于数据链路层。MAC和PHY之间直接通过MII接口进行通信。一个MAC可以同时管理多个PHY的行为。

GMAC主要四个功能:帧发送、帧接收、GMAC控制、媒体独立接口管理(GMII)。

帧发送:

接收上层协议传来的数据,加头尾(控制信息),组成以太网帧,以位数据流形式传到物理层PHY。

帧接收:

接收物理层PHY位数据流,检查是否有效(目的IP,校验码,字节对齐),发送给上层协议,或丢弃。

GMAC控制:

用于全双工模式下控制帧的生成、检测,它处在主机和发送、接收模块之间,对普通的数据帧来说是透明的。

媒体独立接口管理(GMII)

控制物理层PHY的输入输出操作,检查物理层的状态信息。(控制PHY)

三 PHY

用于真正的收发数据。属于物理层。

RJ45网线传输的是特殊编码的差分模拟信号,而计算机等电子设备是不支持这种信号的直接输入的。比如发送数据时,MAC主要处理的数字信号,而 PHY芯片就是负责把MAC的数字信号进行编码,串行化等操作后,转化为模拟信号进行发送。它只是做信号的转换,而不对数字信号进行任何的处理,即使一帧有问题的数据,它也会如实的转发出去。收数据时的流程反之。

PHY还有个重要的功能就是实现CSMA/CD的部分功能。它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去。

PHY 有一个重要的功能就是 自协商。 什么是自协商? 就是PHY一旦连入网络,PHY 会和它相连接的端口的PHY进行协商,当前通信使用的速率是 1000M, 100M 还是10M? 他们相互沟通后,会确定一个 两个端口都支持的最大网络速率。

PHY 还提供了自动控制LED 等的功能。根据当前网络的传输速率,是否有数据传输,来自动控制LED 灯的行为。至于如何控制LED,可以根据PHY的datasheet 进行相关配置。

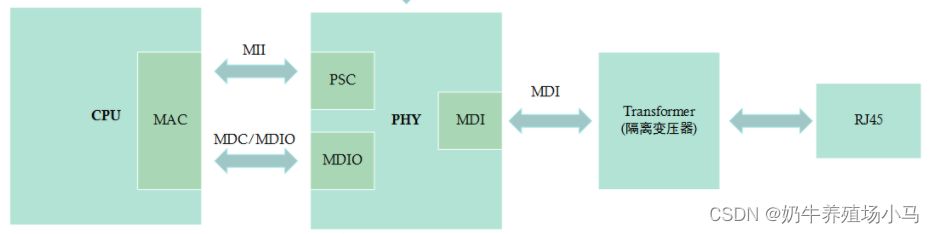

四 MAC控制器和PHY的通讯

以常见的 CPU 集成 MAC,PHY 采用独立芯片为例,抽象后如下:

其中:

MDIO总线接口叫做串行管理接口,以太网MAC通过该接口可以访问PHY的寄存器,通过对这些寄存器操作可对PHY进行控制和管理。

MII总线接口叫做介质独立接口,主要是完成数据收发相关的业务,以太网MAC通过该接口发出数据帧经过PHY后传输到其他网络节点上,同时其他网络节点的数据先经过PHY后再由MAC接收;

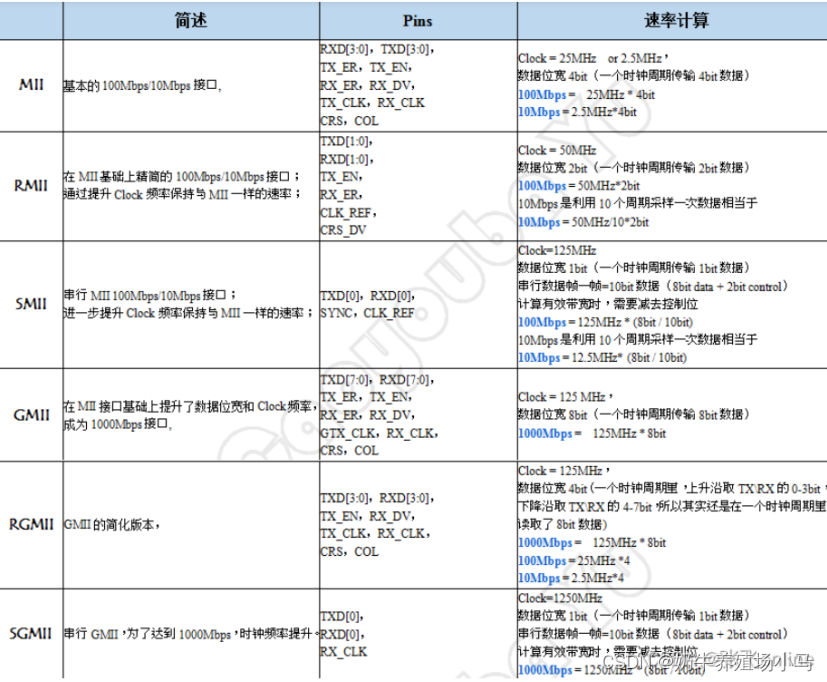

4.1 MII 介质独立接口

有以下接口:

MII: 支持10M/100M,缺点是信号线太多,16根线。

RMII: Reduced MII. 简化的MII,信号线少一倍,8根线,因此时钟也要快一倍。

SMII: Serial MII. 比RMII信号线更少,4根线。

GMII: Gigabit MII。也就是千兆接口了。 相对前面三个,数据从4bit变成8bit。时钟125MHz(1000/8)。缺点是信号线太多,24根线。

RGMII: Reduced GMII。 简化版GMII,为了保持传输速率(1000Mbps)不变,在时钟上升沿和下降沿都采样。

SGMII: Serial GMII。 时钟速率625MHz,所以能到1.2Gbps

以 MII 为例

MII 数据接口总共需要 16 个信号,包括 TX_ER,TXD[3:0],TX_EN,TX_CLK,COL,RXD[3:0],RX_ER,RX_CLK,CRS,RX_DV 等。MII的时钟为25MHz,传输速率为10/100Mbps。

如 25MHZ时钟,数据位宽4bit(一个时钟周期传输 4bit 数据),

则传输速率: 25MHZ * 4bit = 100Mbps

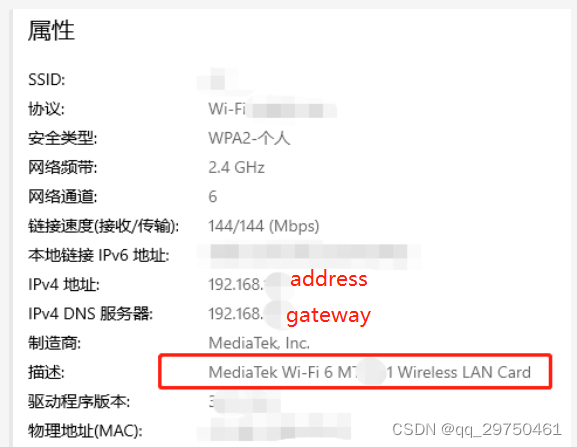

4.2 MDIO 串行管理接口

如上文所述,MDIO用于上层(MAC)配置底层(PHY)的参数,它包括时钟信号 MDC 和数据信号 MDIO ,驱动程序可以通过 MDIO 和 MDC 这两根线访问 PHY 芯片的任意一个寄存器。

如果系统中不止一个PHY,MDIO 接口支持多达 32 个 PHY 。但是同一时刻内只能对一个 PHY 进行操作,那么如何区分这 32 个 PHY 芯片呢?和 IIC 一样,使用器件地址即可。同一 MDIO 接口下的所有 PHY 芯片, 其器件地址不能冲突,必须保证唯一 ,具体器件地址值要查阅相应的 PHY 数据手册。

注意,这里提到的PHY芯片Strap的物理地址仅与MDIO的配置过程寻址有关,和通常意义上的 MAC 地址没有任何关系。