【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

altera的fpga本身自带了rom的ip,使用起来也十分方便。实际开发中,使用rom的场景也很多,比如一些默认的配置文件,需要存储的寄存器数据,还有就是一些保存chip信息的数据,这些都是可以当成rom最后综合到sof文件里面的。

要实现ip rom的使用,需要完成这么几个步骤,

1、创建mif文件

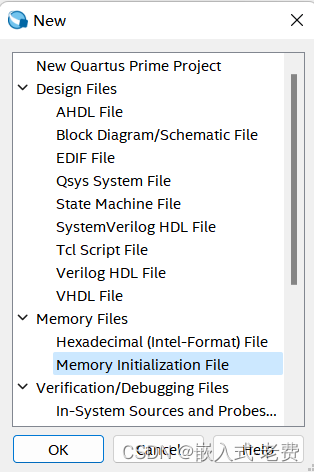

创建mif文件,主要是给ip rom使用的,最终导入到ip里面。选择File,再选择New,

在弹出来的对话框中选择Memory Initialization File,就可以看到这样的对话框,

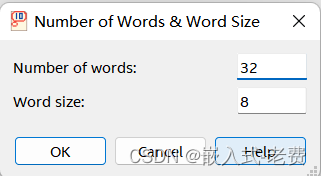

这里提示我们需要多少个word,每个word是多长。不妨输入32和8,

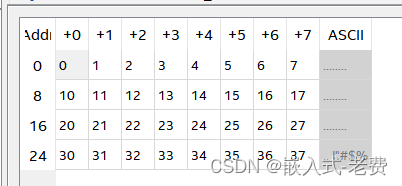

因为我们只是测试,所以只要在对应的矩阵框里面输入相关的数据即可。修改后记得保存,把这个生成的mif文件添加到刚刚创建的工程当中。

2、创建ip rom

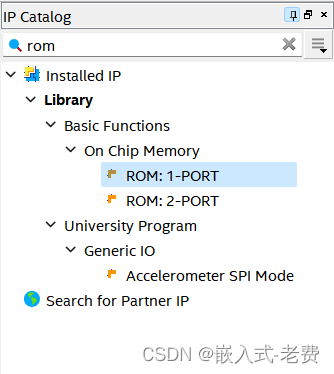

创建ip rom的过程也不复杂,首先在ip catalog中输入rom即可,

在对话框中输入文件名之后,就可以开始配置,

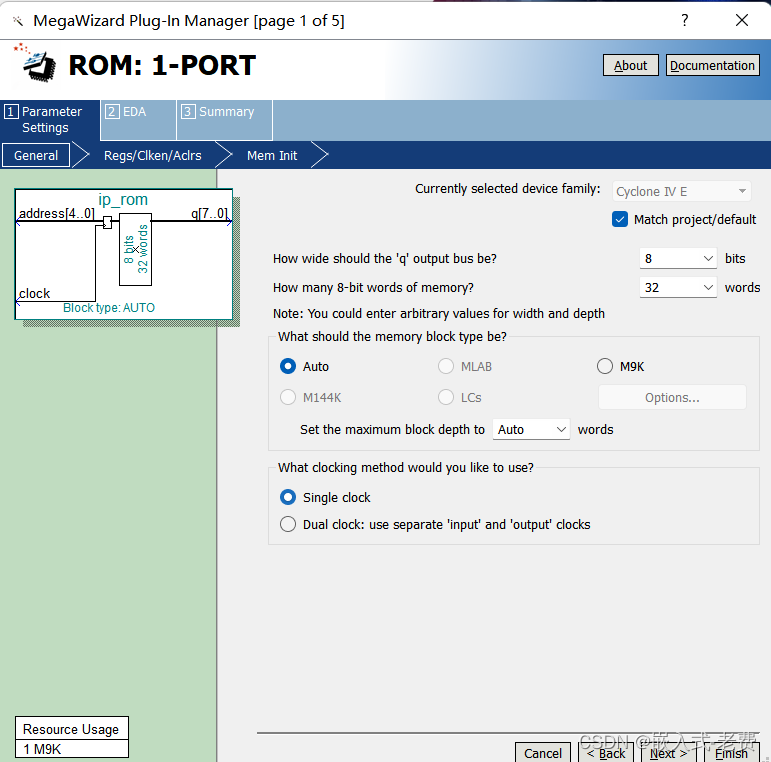

首先当然还是要输入word个数和word的bit数目。这里需要和之前创建的mif文件保持一致。完成后,继续下一步,

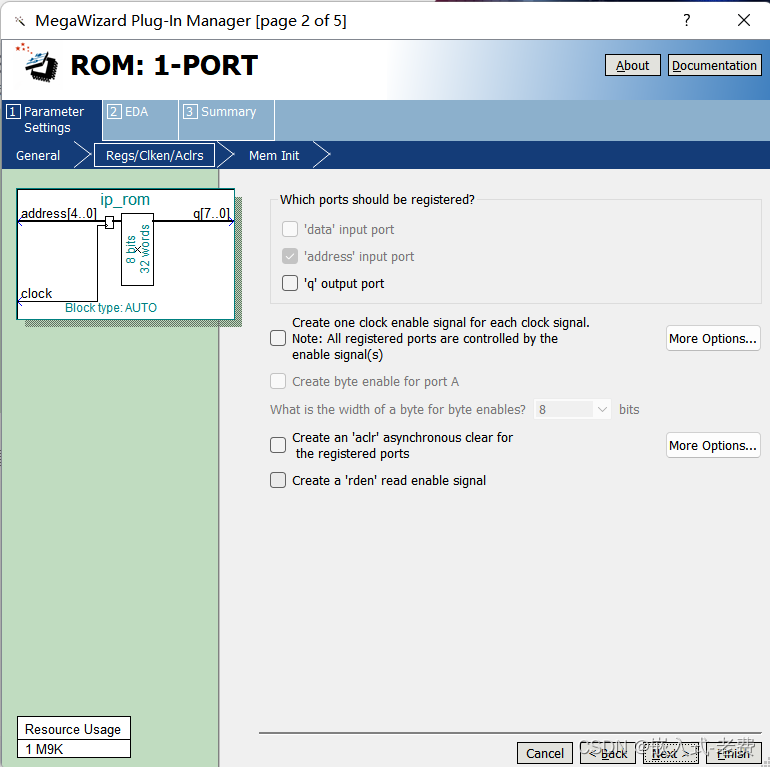

这里为了提高输出速度,取消了‘q’ output port之前的勾选按钮。下一步,

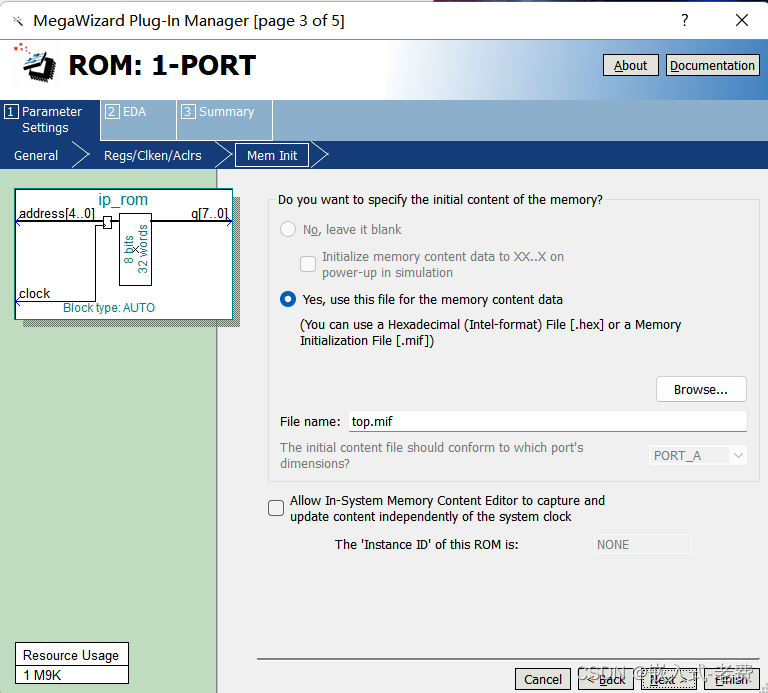

这是ip rom里面比较重要的一步。最主要的工作就是需要把刚才创建的top.mif文件导入到ip rom中去。走到这一步,其实主要的工作已经完成了,可以直接单击Finish。Quartus会提示我们是否把文件添加到工程中,选择是即可。

3、准备测试文件rom_test.v

module rom_test(clk, rst);

input clk;

input rst;

wire[7:0] data;

reg[4:0] address;

always@(posedge clk or negedge rst)

if(!rst)

address <= 5'd0;

else

address <= address + 1;

ip_rom ip_rom0(

.address(address),

.clock(clk),

.q(data)

);

endmodule

测试的代码比较简单,主要的工作就是递增address地址。其次输入信号只有clk和rst,没有输出信号。它们对应的引脚是E1和N13。既然没有输出信号,那么怎么判断我们的配置和测试代码是否正确呢,一个重要的办法就是借助于signal tap来检验。

4、配置signal tap

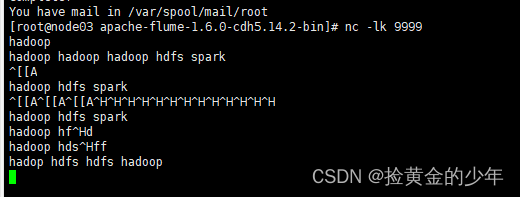

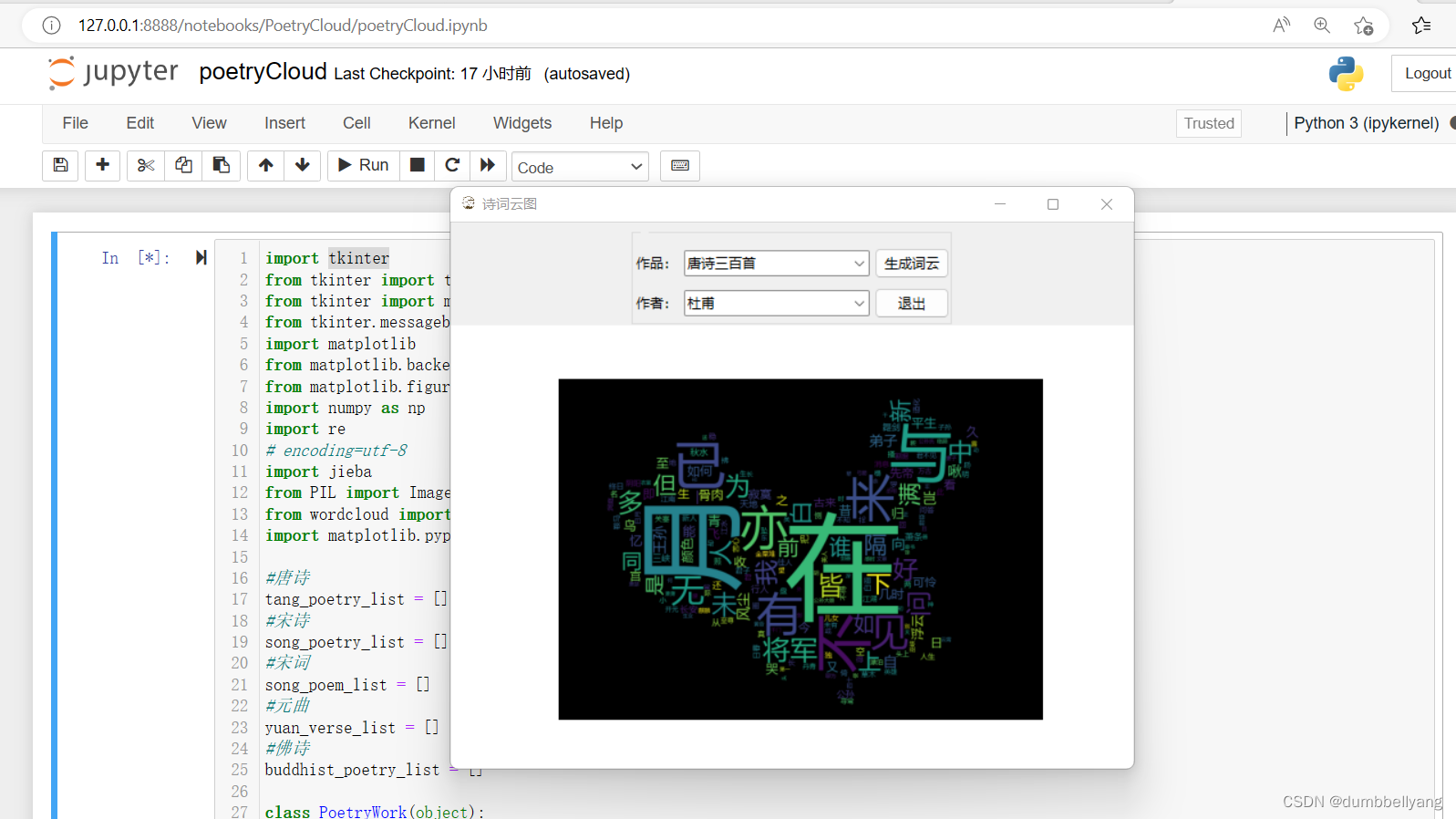

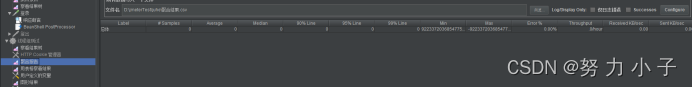

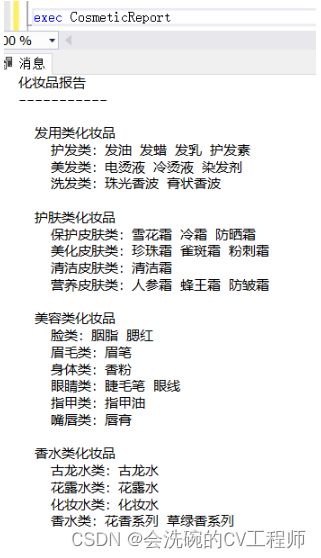

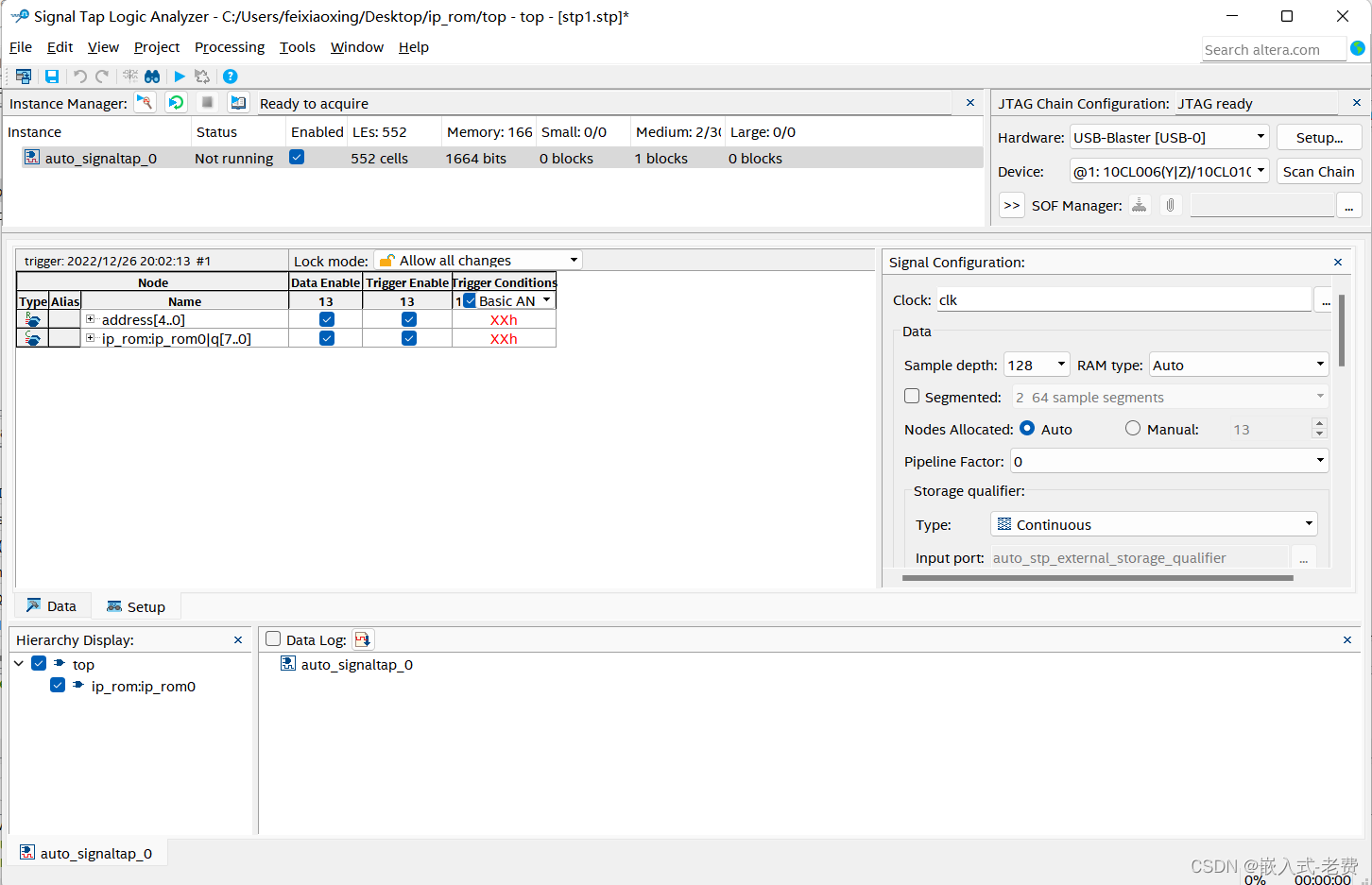

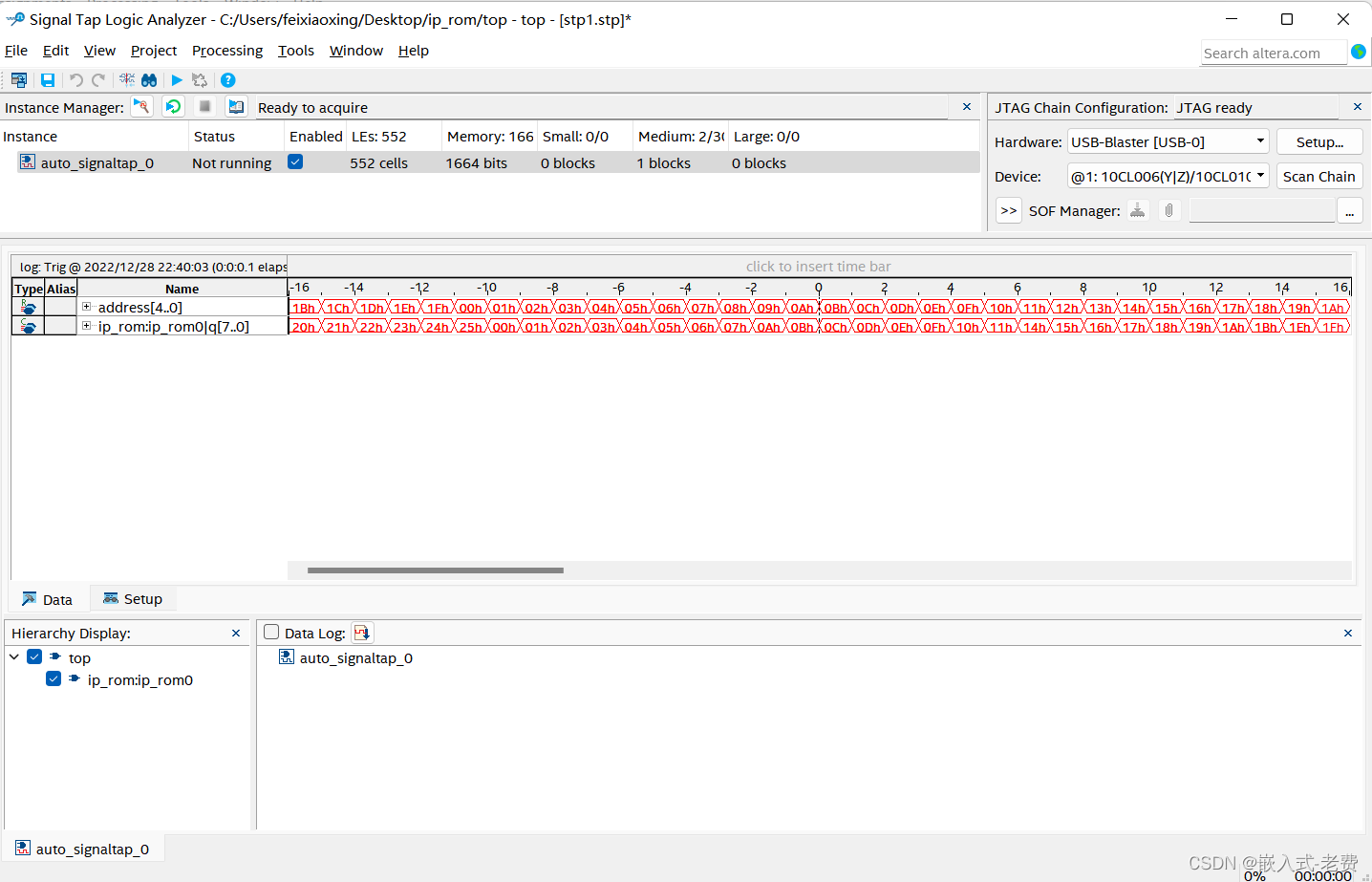

配置signal tap都是一些常规动作,比如设置jtag、配置clk、挑选address和q数据。 在输入F6和Esc之后,不出意外就可以看到这样的数据,

分析一下,之前mif文件设定的时候,0-7对应的数据是0-7,8-15对应的数据是8-17,以此类推。我们可以先找到address为0的时候,然后看q什么时候是0。有了0作为基准之后,就可以看剩下来的地址了。通过观察发现,q吐出数据的速度会慢一个节拍,也就是address为0的时候,下一个节拍才会出现0x00数据,接着address为1的时候,下一个节拍吐出0x01的数据。这就是从signal tap抓包的出来的结论,也是后面实际使用的时候需要注意的地方。

5、总结

ip rom和之前ip pll最大的不同就是需要创建一个类似于mif这样的文件。其他的地方就是如法炮制,创建好ip之后,实例化一个ip添加到top文件中,就可以开始使用了。