北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

使用FPGA开发板验证的教程,请参考

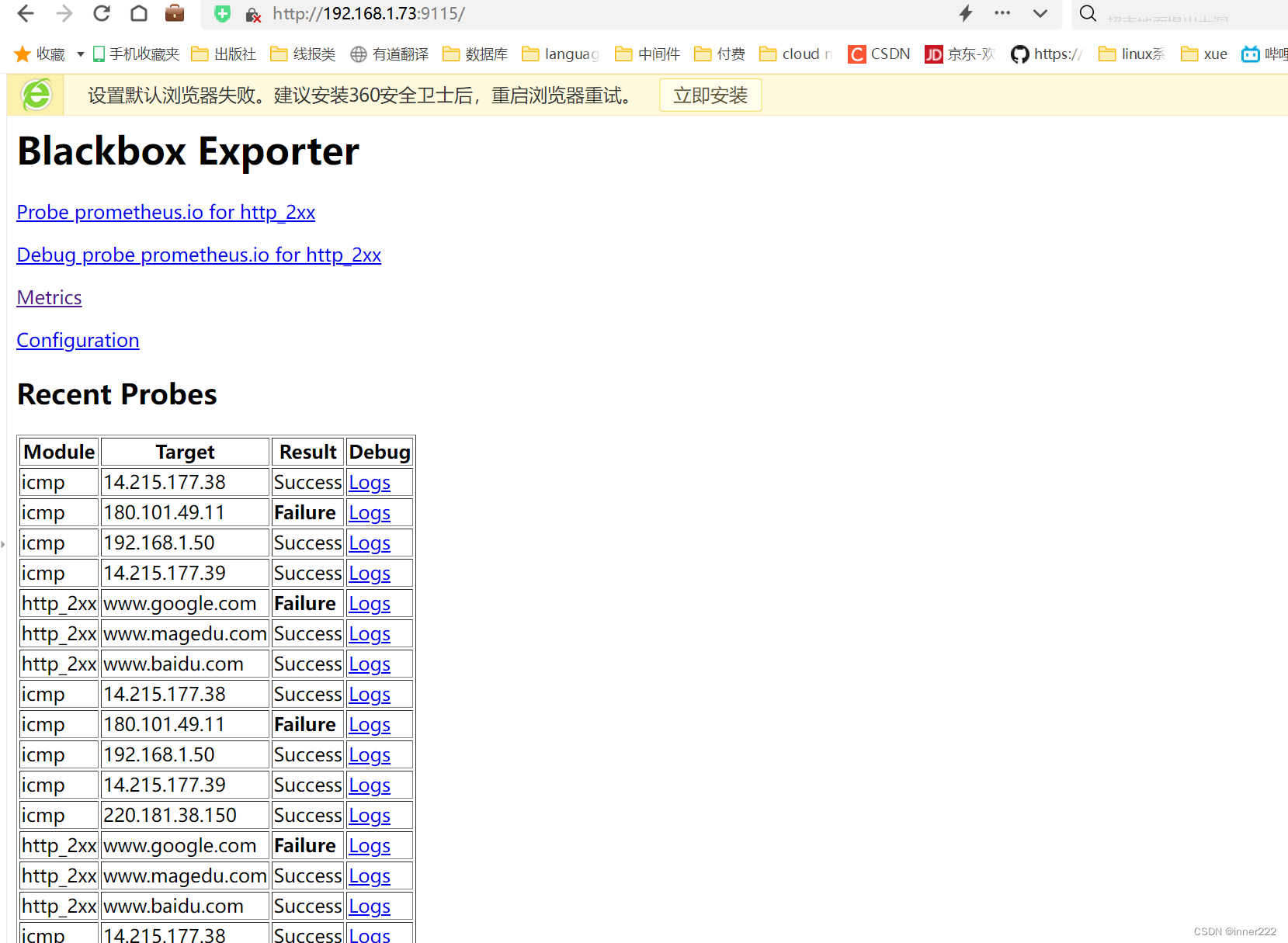

北邮22级信通院数电:Verilog-FPGA(10)第十周实验 实现移位寄存器74LS595-CSDN博客

本篇博客主要以modelsim仿真的方法验证74LS595移位寄存器的功能。

目录

一.代码部分

1.1 shift_register.v

1.2 dtri.v

1.3 dtri_n_g.v

1.4 shift_register_tb.v

二.仿真验证结果

一.代码部分

1.1 shift_register.v

主程序。

module shift_register

(

input SCK,SI,SCLR,RCK,G,

output wire QA,QB,QC,QD,QE,QF,QG,QH,QH_s

);

wire RA,RB,RC,RD,RE,RF,RG,RH,RH_n;

wire SA,SB,SC,SD,SE,SF,SG,SH;

dtri Ra(.clk(SCK),.rst(SCLR),.d(SI),.q(RA));

dtri Rb(.clk(SCK),.rst(SCLR),.d(RA),.q(RB));

dtri Rc(.clk(SCK),.rst(SCLR),.d(RB),.q(RC));

dtri Rd(.clk(SCK),.rst(SCLR),.d(RC),.q(RD));

dtri Re(.clk(SCK),.rst(SCLR),.d(RD),.q(RE));

dtri Rf(.clk(SCK),.rst(SCLR),.d(RE),.q(RF));

dtri Rg(.clk(SCK),.rst(SCLR),.d(RF),.q(RG));

dtri Rh(.clk(SCK),.rst(SCLR),.d(RG),.q(RH));

assign RH_n = ~RH;

assign QH_s = ~RH_n;

dtri_n_g Qa(.clk(RCK),.d(RA),.g(G),.qb(SA),.qq(QA));

dtri_n_g Qb(.clk(RCK),.d(RB),.g(G),.qb(SB),.qq(QB));

dtri_n_g Qc(.clk(RCK),.d(RC),.g(G),.qb(SC),.qq(QC));

dtri_n_g Qd(.clk(RCK),.d(RD),.g(G),.qb(SD),.qq(QD));

dtri_n_g Qe(.clk(RCK),.d(RE),.g(G),.qb(SE),.qq(QE));

dtri_n_g Qf(.clk(RCK),.d(RF),.g(G),.qb(SF),.qq(QF));

dtri_n_g Qg(.clk(RCK),.d(RG),.g(G),.qb(SG),.qq(QG));

dtri_n_g Qh(.clk(RCK),.d(RH),.g(G),.qb(SH),.qq(QH));

endmodule1.2 dtri.v

输出为Q的D触发器。

module dtri

(

input clk,rst,d,

output wire q

);

reg q1;

always @ (posedge clk)

if(!rst)

q1 <= 1'b0;

else

q1 <= d;

assign q = q1;

endmodule

1.3 dtri_n_g.v

输出为~Q的D触发器。

module dtri_n_g

(

input clk,d,g,

output wire qb,qq

);

reg q1,q2;

always @ (posedge clk)

begin q1 <= ~d; end

assign qb = q1;

always @ (*)

begin

if(g) q2 <= 1'b0;

else q2 = ~q1;

end

assign qq = q2;

endmodule1.4 shift_register_tb.v

仿真程序。

`timescale 1ns/100ps

module shift_register_tb();

reg SCK,SI,RCK,SCLR,G;

wire QA,QB,QC,QD,QE,QF,QG,QH,QH_s;

initial

begin

SCK=0;

SI=0;

RCK=0;

SCLR=0;

G=0;

#20 SI=1;SCLR=1;

#20 SI=0;RCK=~RCK;

#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;

#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;

#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;

#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;#10 RCK=~RCK;

#10 RCK=~RCK;G=1;

#10 SI=1;

#20 SI=0;RCK=1;

#10 RCK=0;G=0;

#40 SCLR=0;

#10 RCK=1;

#10 RCK=0;SCLR=1;

end

always #10 SCK=~SCK;

shift_register shift_1

(

.SCK(SCK),

.SI(SI),

.RCK(RCK),

.SCLR(SCLR),

.G(G),

.QA(QA),

.QB(QB),

.QC(QC),

.QD(QD),

.QE(QE),

.QF(QF),

.QG(QG),

.QH(QH),

.QH_s(QH_s)

);

endmodule

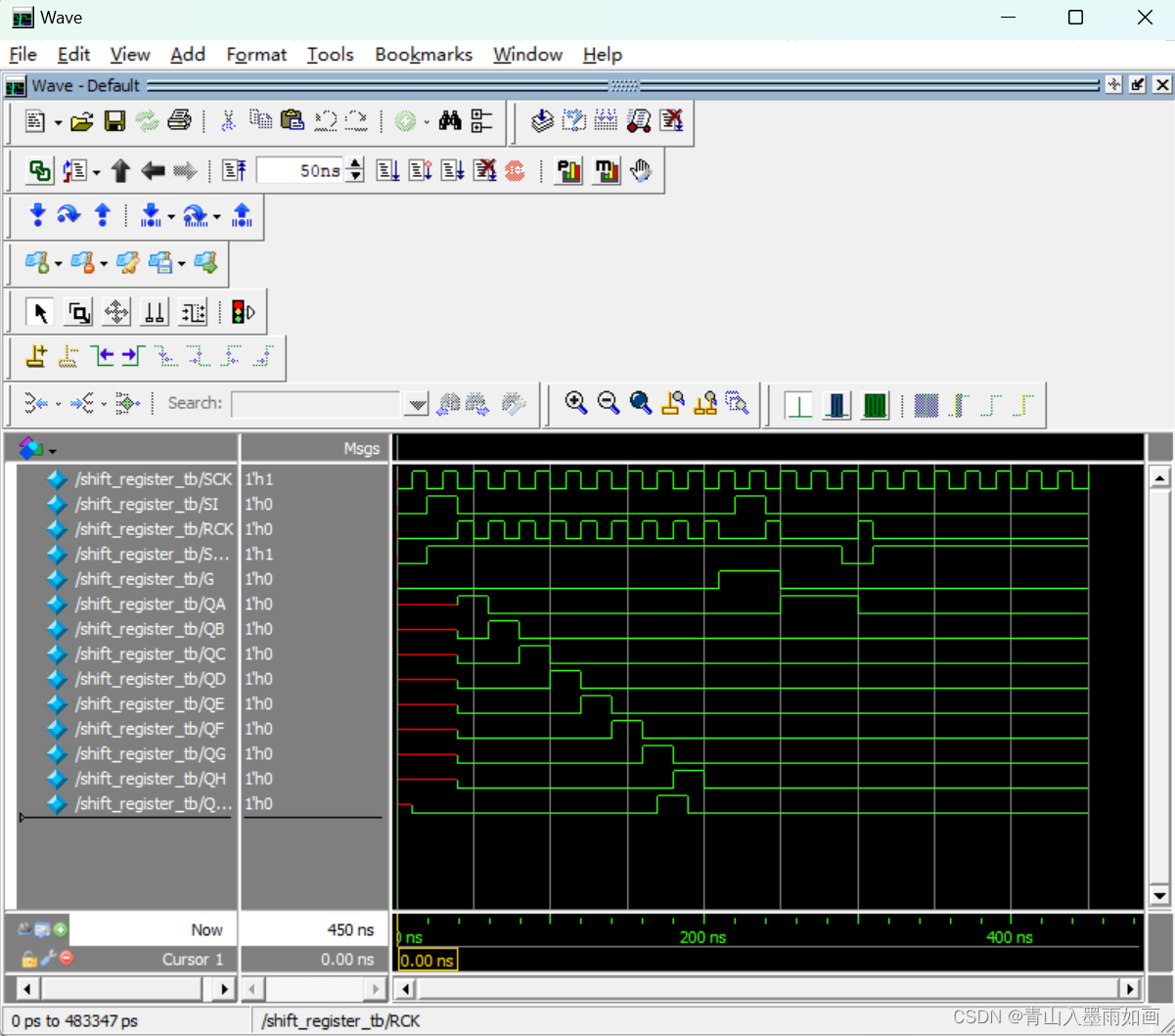

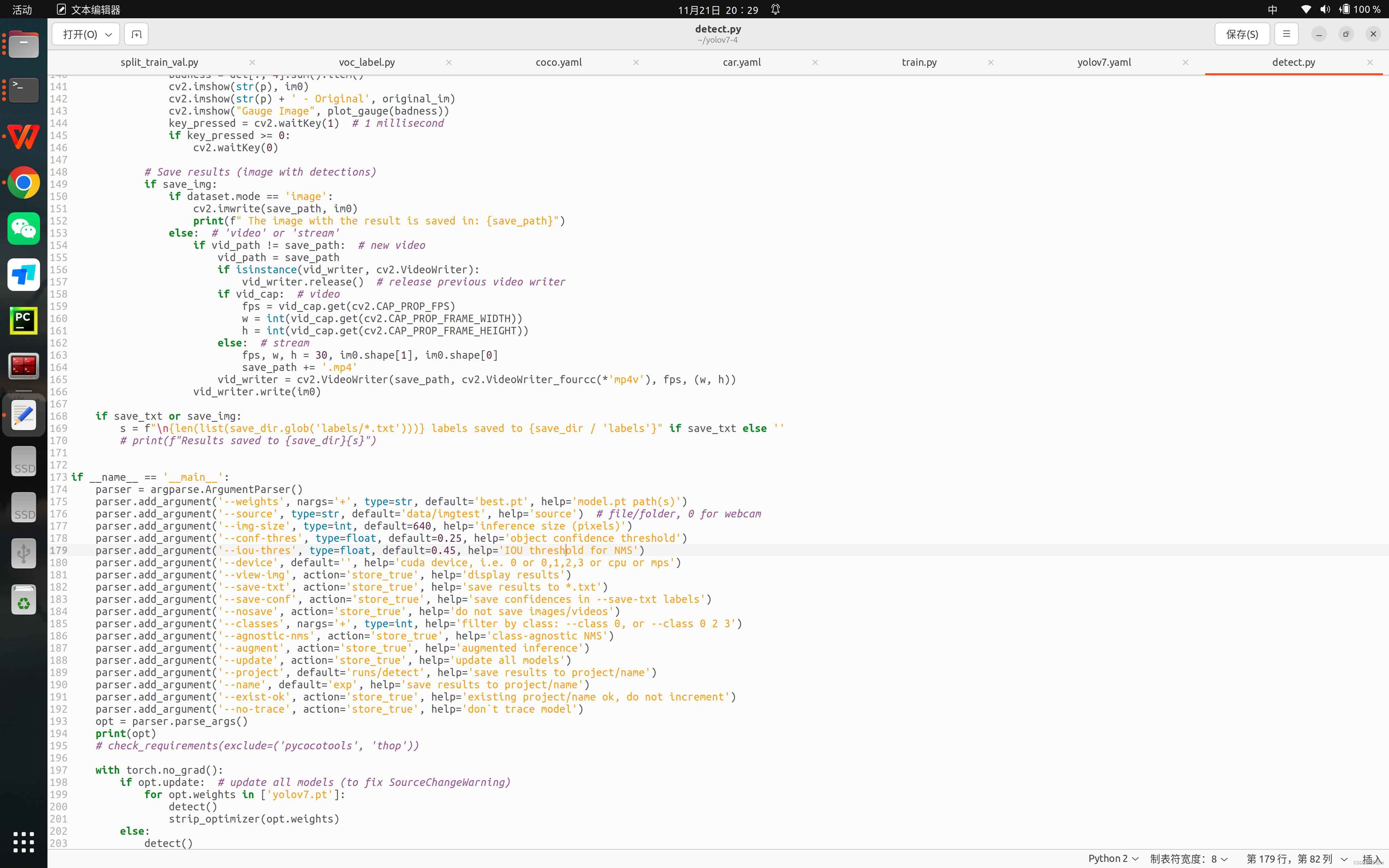

二.仿真验证结果