VDMA彩条显示实验之二

这一篇紧接上一篇文章

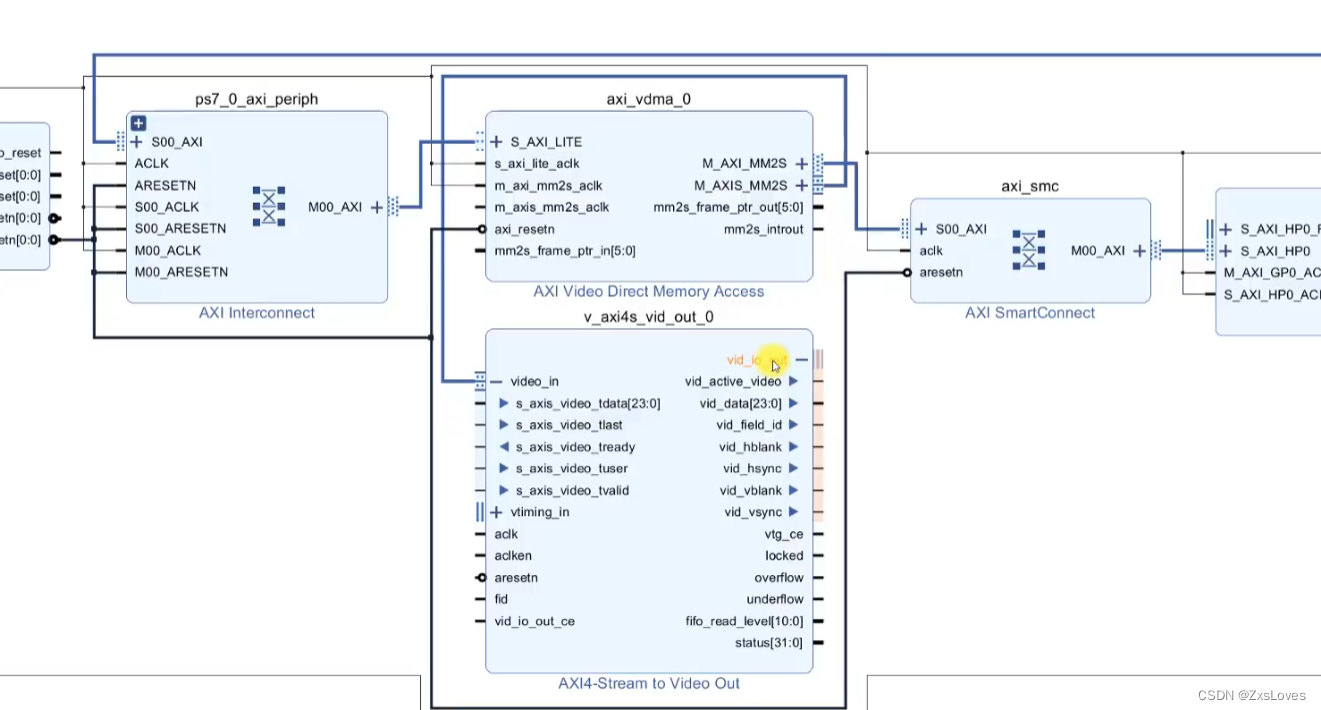

我们添加一个 VID_out 的 IP核

其实 相对来说 就是我们把 传进来的串行信号 转化成并行输出各个信号 (把 Stream 的 输出信号流转化成在 RGB上 输出的 格式 )

下面是对IP核的简介

AXI4-Stream to Video Out IP核 被用来设计成 连接 AXI-Stream 接口 和 video sourse(包含了关于视频的一系列数据) 接口

video out IP 核 在视频处理和 视频之间提供了一个桥梁

这个 IP核 一般来说是和 VTC 一起使用的

我们先来讲述一下 video out这个 IP的 使用方法

但是在 系统里面 视频通常使用 独立的 消影 同步信号进行传输的

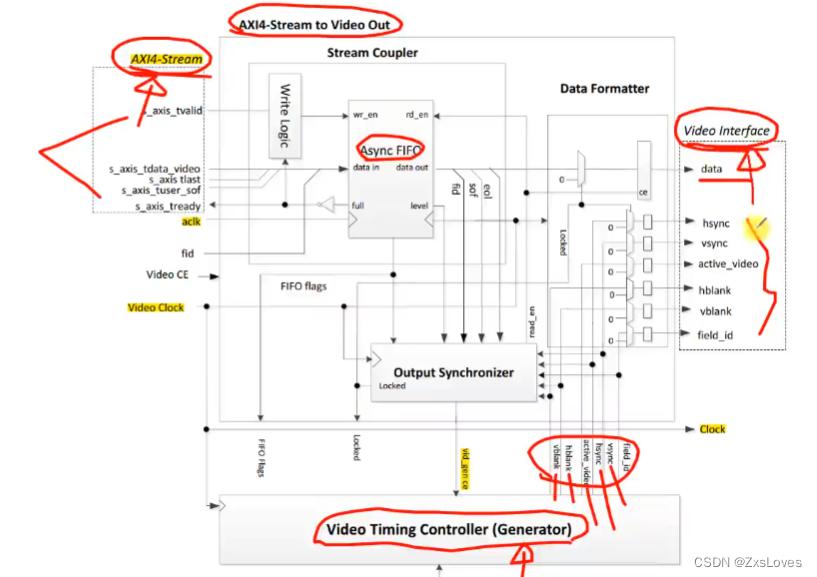

这个 说的是 在 xilinx IP之间用的是 AXI stream 接口的 协议

但是在 系统 内部 使用的 独立的 消影 同步信号进行传输的

AXI Stream video out IP 核 作用是 把 AXIstream 协议的数据转化成 独立 的 视频所能用的 数据输出形式

输入我们了解了 现在我们了解一下 视频的输出

这是转化成 视频 所能 接收的 格式

这个IP被设计出来是个 VTC - generator一起使用的

VTC 给我们 的 video提供了一个 video的时序信息

在整个 IP中 其实有一个 异步FIFO 用来实现 跨时钟域的输出

内部还有一个同步系统

同步系统的作用是把传递的 AXI Stream 接口 本来有的 eol sof 接口全部同步到 VTC 接口的 行列 信号

因为最后 输出的 是行 列 标志 来指示最后一个输出

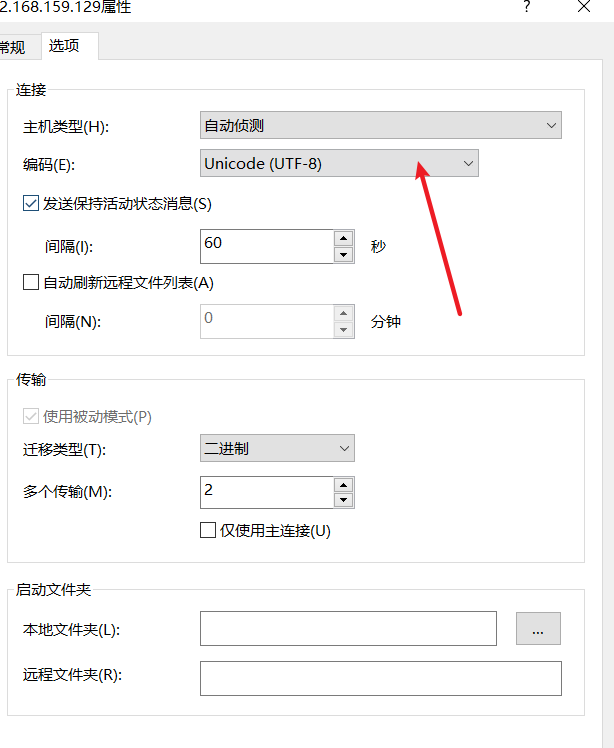

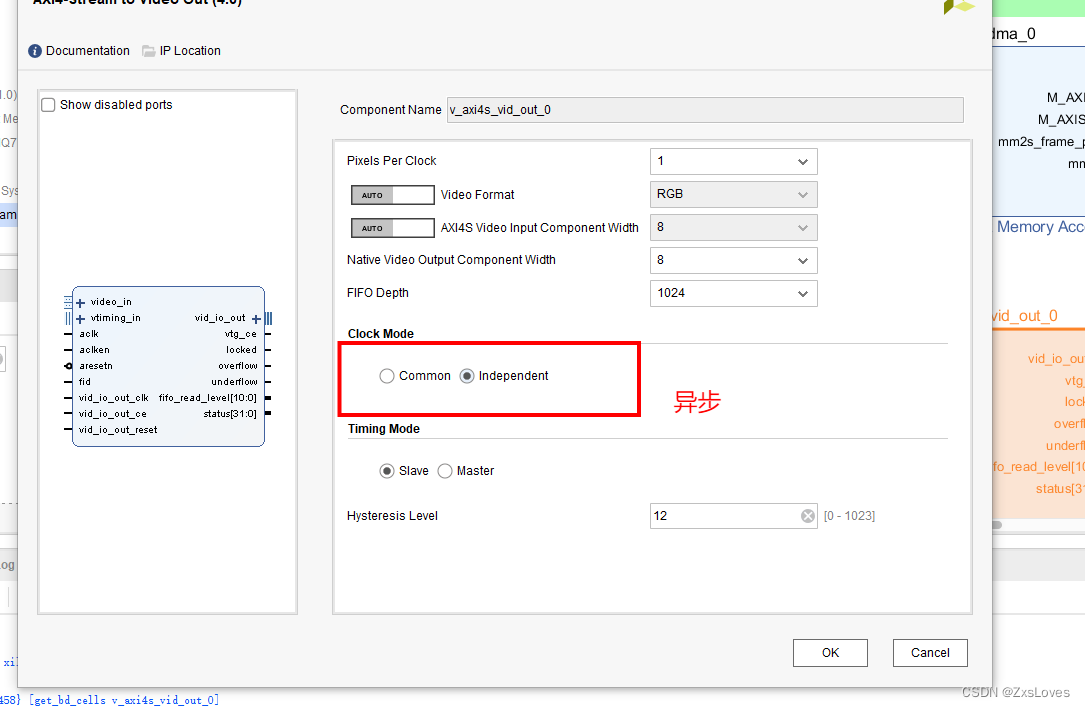

AXI 4 Stream Video out 有两种时序模式 一个是 slave 另一个是 master 模式

这个 Slave 和 master是相对于 VTC来说的

举例 : 如果在 slave模式下 就可以控制 AXI stream 和 VTC 之间的相位差

我们从 stream 输入进来的视频流的时间 最终要同步于 VTC 提供的时间 它们之间会存在一个相位差

如果我们需要同步的话 就需要想方法 更合理的控制相位差 控制视频什么时候输入 VTC的时序什么时候产生 就现在来说 如果用Video out IP 核 控制 VTC 这样 VTC 就是 在 slave模式下

VTC 工作在 master 模式 就相当于 VTC放飞自我了 我们要尽量去贴近 VTC的 输出时序

所以 通常模式 下 我们推荐使用 slave模式 的 VTC 去减小 缓冲和延时

实际上的控制信号是 vid_gen ce 这个信号拉高VTC 才输出 信号

Hysteresis Level 表示的是 缓存的数 我们 缓存了多少数后才开始同步

下面介绍 Buffer Requirements 这是 buffer缓冲的大小

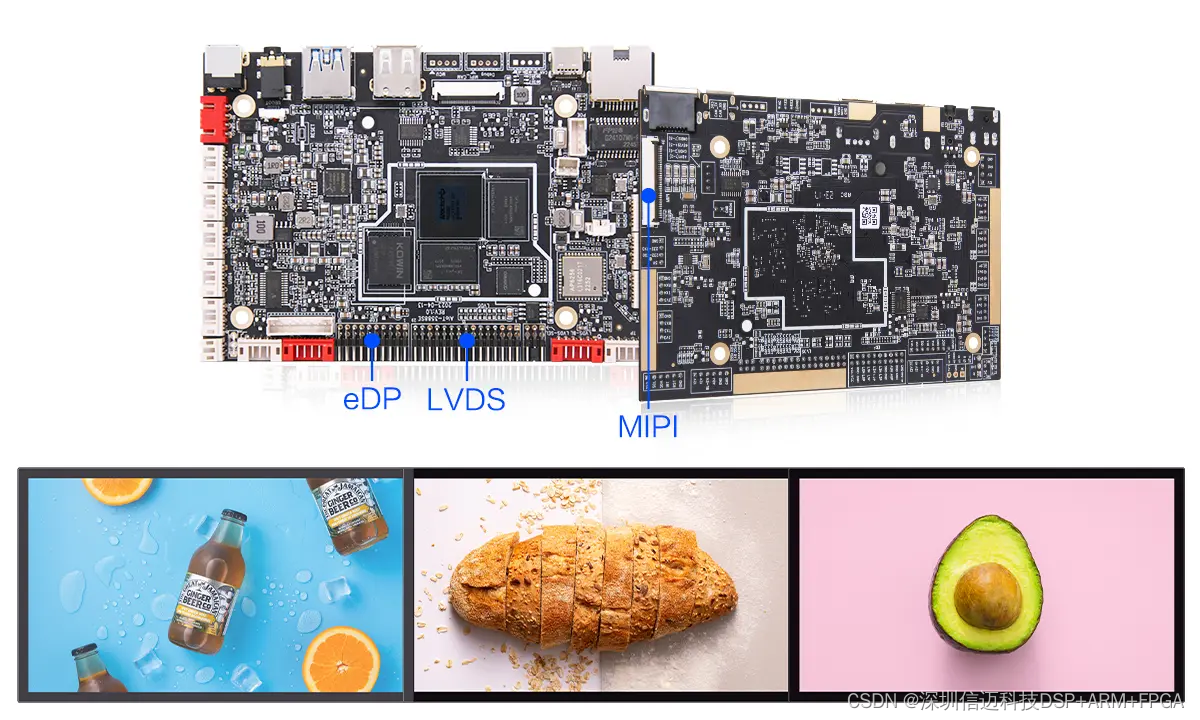

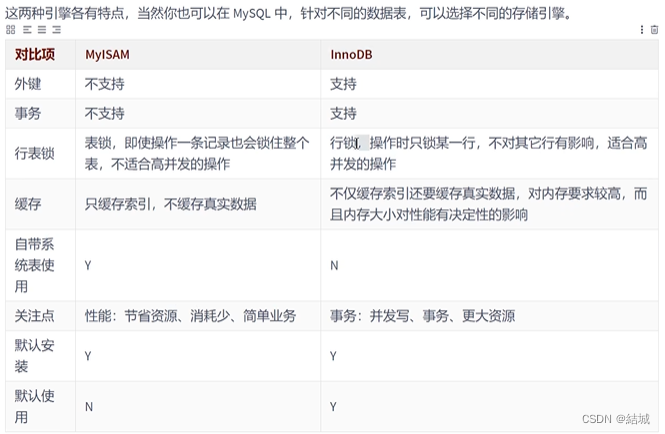

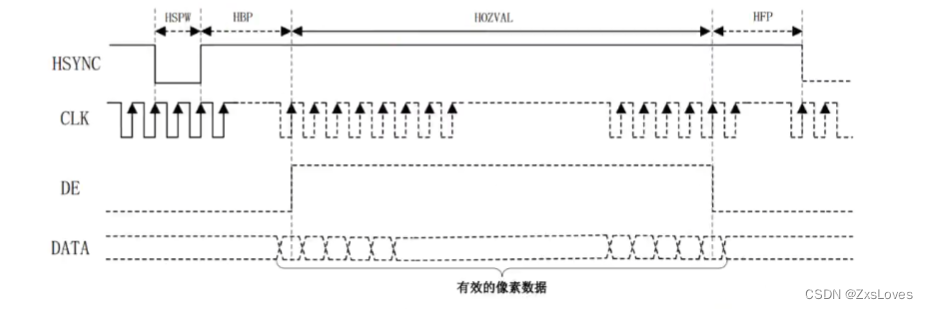

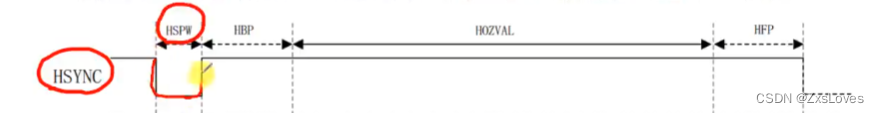

我们先来学一下 RGB LCD的屏幕时序信息

行同步 低电平的同步时间 然后是 消影 时间 中间一部分是 像素的有效时间

整个像素的有效时间 也可以用 DE 信号来表示 在DE信号拉高的时候 整个数据DATA 才会传输

当DE拉低的时候 DATA 不会传输

我们举例出现的一个问题

当DE信号拉高的时候 数据 必须 源源不断的输入过去

但是 FIFO会有 空和满 的 不同情况

我们先考虑 FIFO是 空的情况下 输入进来的数据跟不上

FIFO 为满的情况下 是 告诉前面 ready 不要传了

所以我们更需要注意的 是 FIFO 为 空的情况

buffer 主要考虑 上游输出的速率 和下游输出的速率 让其 大致上相等