专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

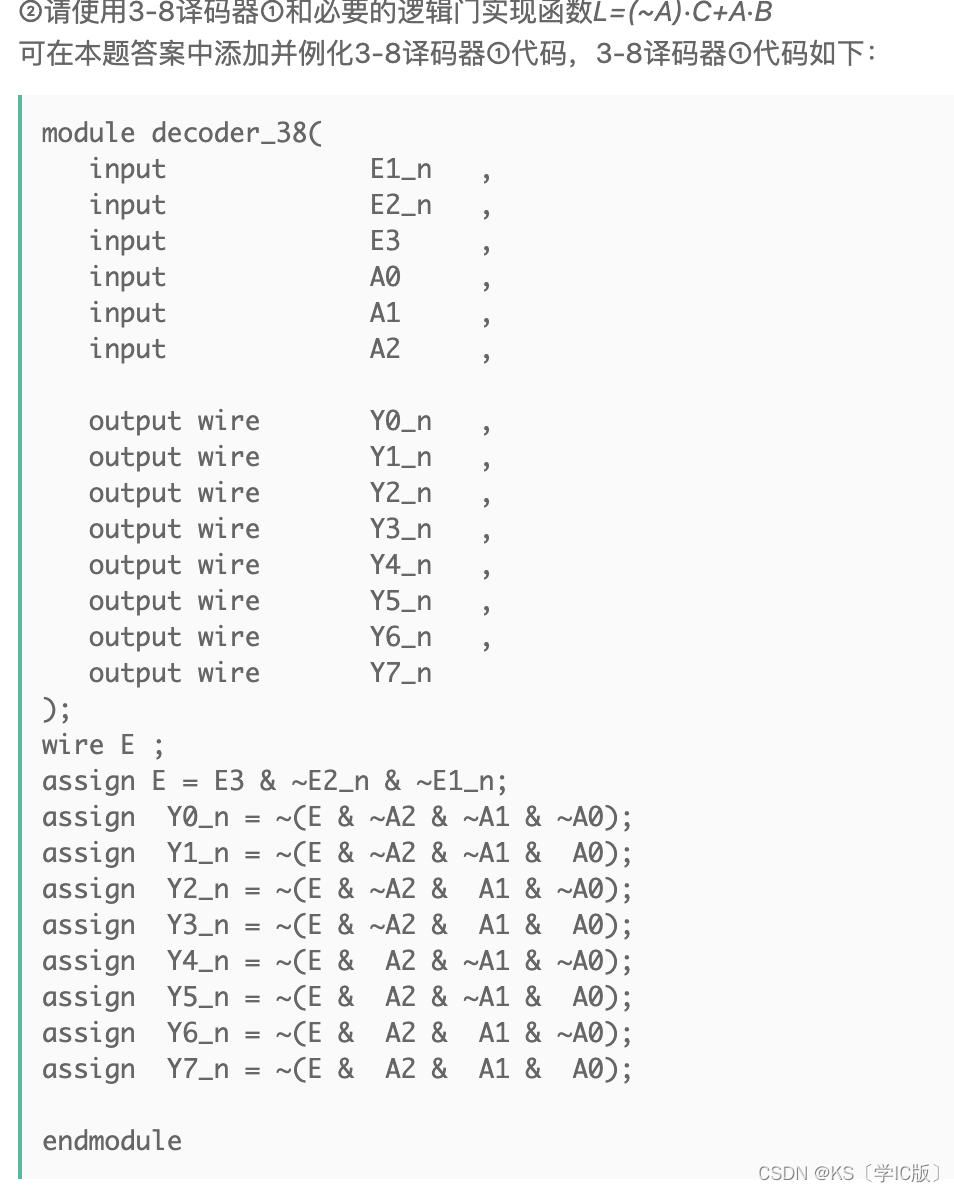

`timescale 1ns/1ns

module decoder_38(

input E1_n ,

input E2_n ,

input E3 ,

input A0 ,

input A1 ,

input A2 ,

output wire Y0_n ,

output wire Y1_n ,

output wire Y2_n ,

output wire Y3_n ,

output wire Y4_n ,

output wire Y5_n ,

output wire Y6_n ,

output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);

endmodule

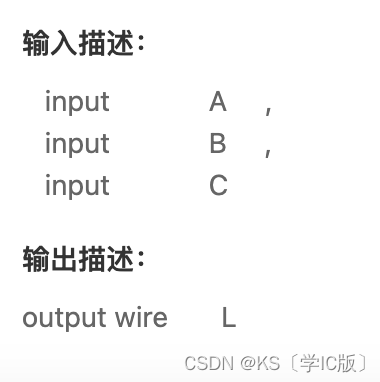

module decoder0(

input A ,

input B ,

input C ,

output wire L

);

wire [7:0] Y ;

decoder_38 d(

.E1_n(0 ),

.E2_n(0 ),

.E3(1 ),

.A0(C ),

.A1(B ),

.A2(A ),

.Y0_n(Y[0]),

.Y1_n(Y[1]),

.Y2_n(Y[2]),

.Y3_n(Y[3]),

.Y4_n(Y[4]),

.Y5_n(Y[5]),

.Y6_n(Y[6]),

.Y7_n(Y[7])

);

assign L = ~(Y[1] & Y[3] & Y[6] & Y[7]) ;

endmodule

![oracle21c安装报错【[INS-32014] 指定的 Oracle 基目录位置XXX无效】](https://img-blog.csdnimg.cn/780ae402290d491184a462acadc1c5f3.png)