目录

0x00 便签存储器(Scratchpad memory)

0x01 缓存锁定(Cache lockdown)

0x02 读取 DRAM 内存

0x03 DREM Banking

0x04 DRAM 猝发(DRAM Burst)

0x00 便签存储器(Scratchpad memory)

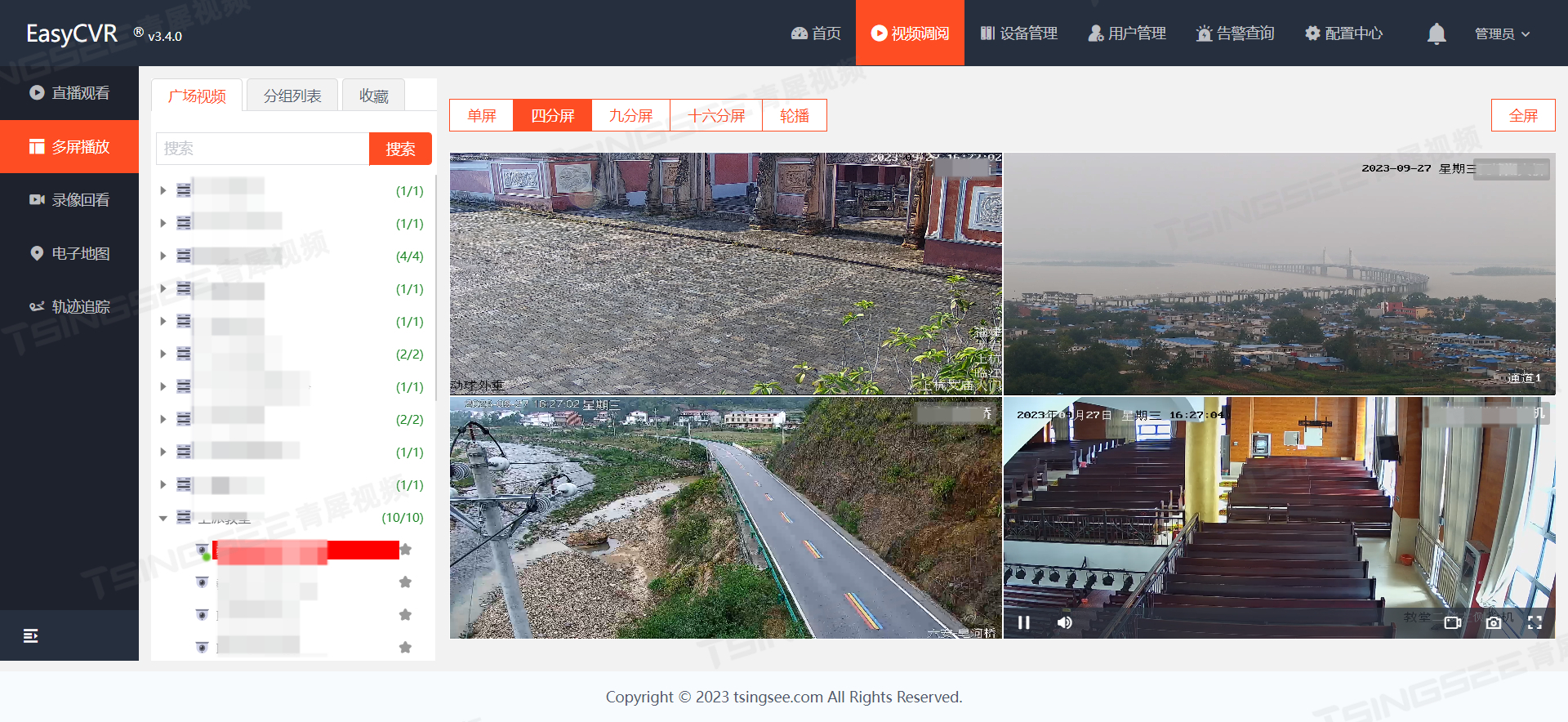

便签存储器(Scratchpad memory, SPM)是一种内存,用于存储占用部分地址空间的数据或指令。用来暂时存放部分数据或中间结果的存储器,一般是高速缓冲存储器的一部分,也可以是主存储器或外存储器的一部分。

与高速缓存不同的是,数据或指令一开始就被移入 Scratchpad 内存中,并一直保留到应用完成。因此,数据或指令在便签存储器中的访问速度是固定的。

- 便签存储器的主要用途是嵌入式系统,在这种系统中,应用程序中使用的程序或数据是事先已知的。

- 近年来由于体系结构和编译器研究的进步,出现了许多不同的便签存储器。

0x01 缓存锁定(Cache lockdown)

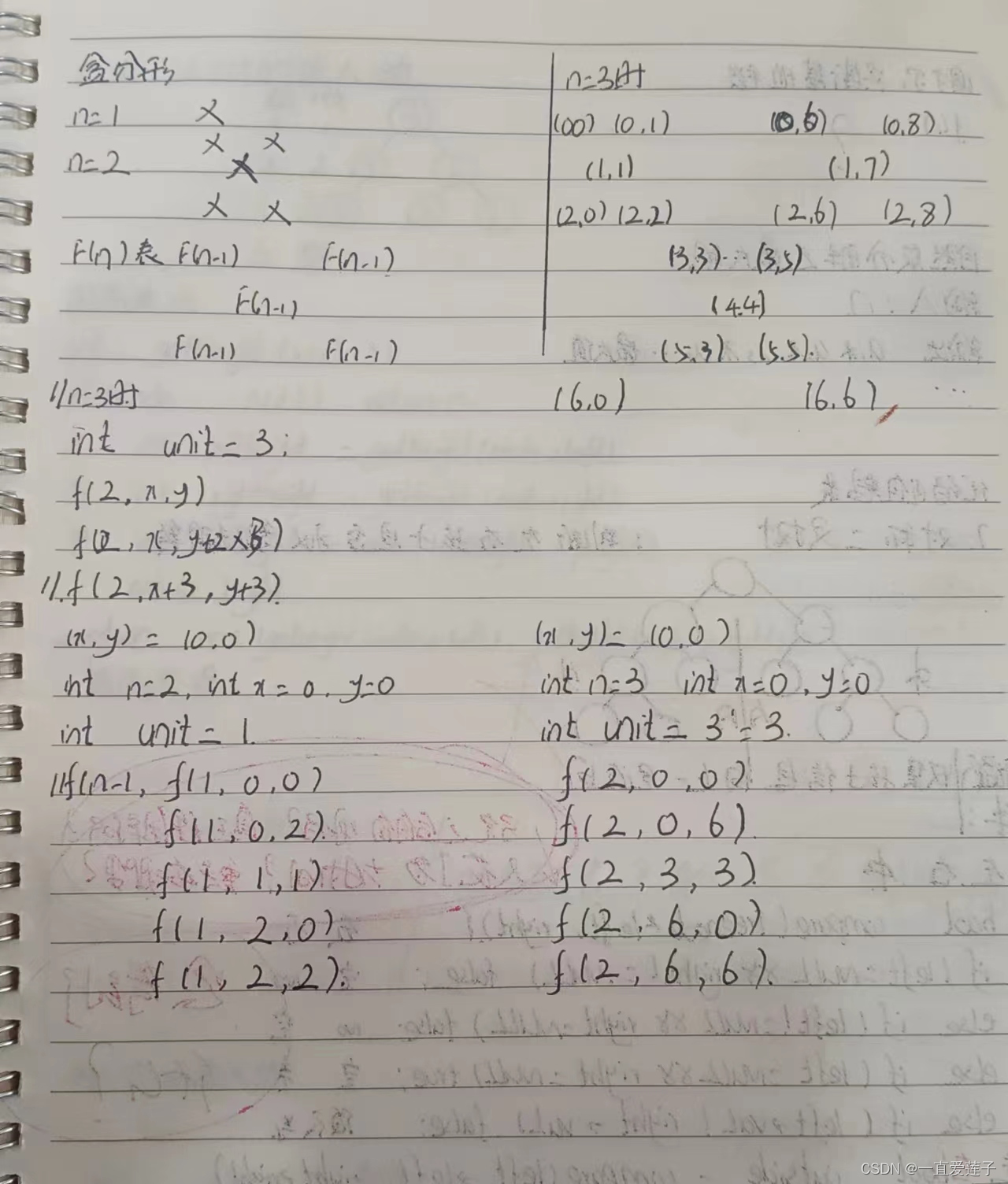

ARM 中的缓存锁定,该功能可使程序将时间关键的代码和数据加载到缓存内存中,并将其标记为免逐出 (eviction) 。锁定中的代码或数据可加快系统响应速度,避免不可预测的响应时间。

ARM 内核在锁定状态下分配的单位大小是一种方式。

例如,四向集关联缓存的出路允许将代码或数据锁定在缓存大小 的单位中。

锁定使用示例:矢量中断表、中断服务例程、大量使用的关键算法、常用全局变量。

0x02 读取 DRAM 内存

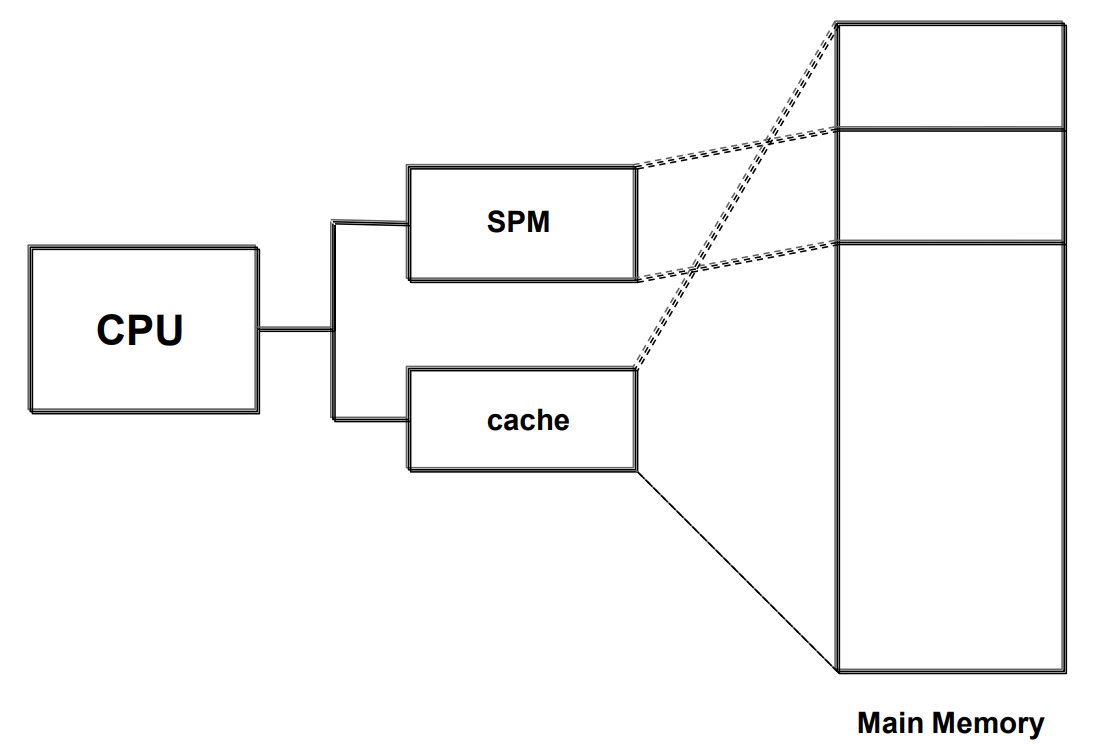

每个部件提供 8 bit 数据,8 个部件 x 8 bit = 每个 DIMM (或通道) 64 bit。

两个通道提供 126 bit 数据。

由于内核(如 GPU)不断增加,应用对内存带宽的要求也越来越高。应用需要不同的服务质量(即低延迟、高带宽、低延迟、低延迟)。

如何增加带宽 (bandwidth) 并减少延迟 (latency) ?Channel、bank 和 Burst。3D 集成技术可以改善带宽和延迟问题。通过垂直堆叠多个存储层,提高内存容量的同时,也减少了数据传输的距离,这可以减少延迟。此外,更多的层次可以提供更多的通道,进一步增加内存带宽。

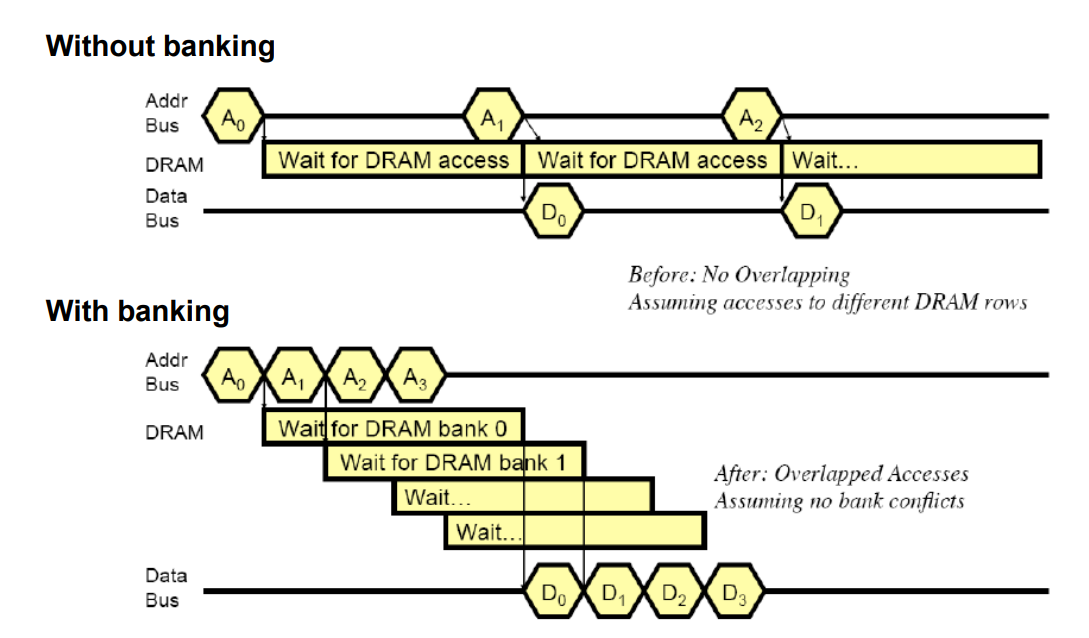

0x03 DREM Banking

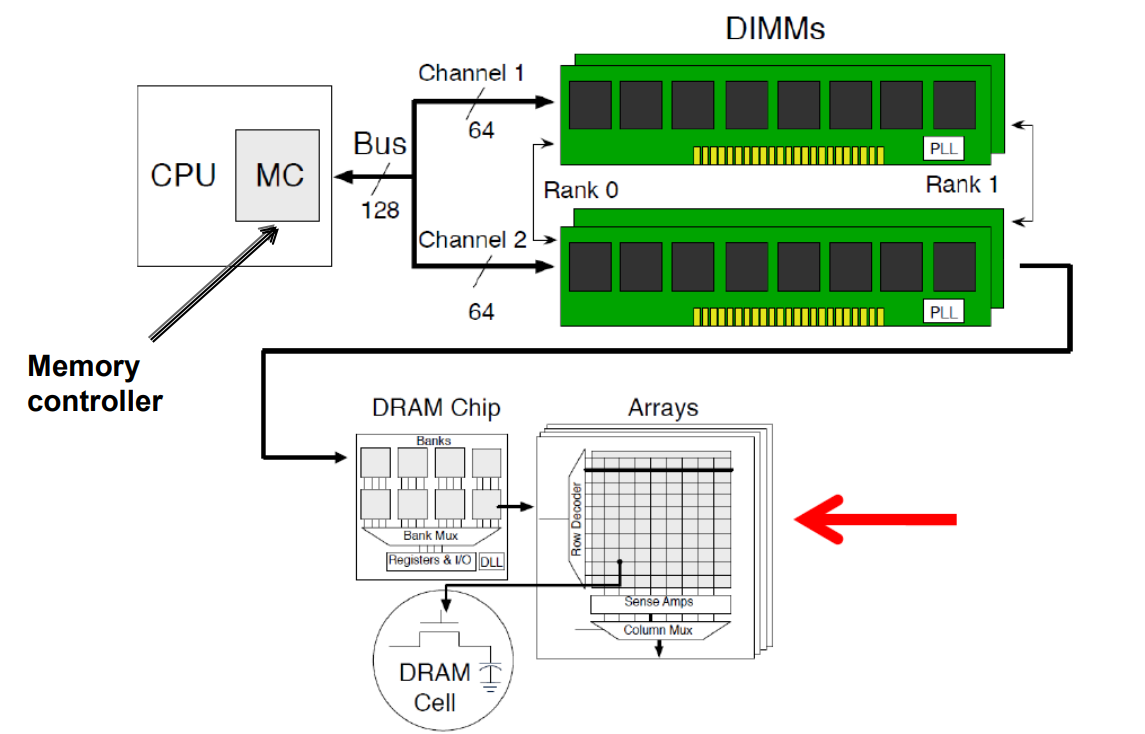

Micron 的 2Gb x8 DDR3 芯片:总容量 = 2Gb,存储组数 = 8,双倍数据速率。

主要思想:访问地址必须均匀分布在不同的库中。

库冲突:访问映射到单个库 → 退化为单个库的性能,单个存储体的性能

0x04 DRAM 猝发(DRAM Burst)

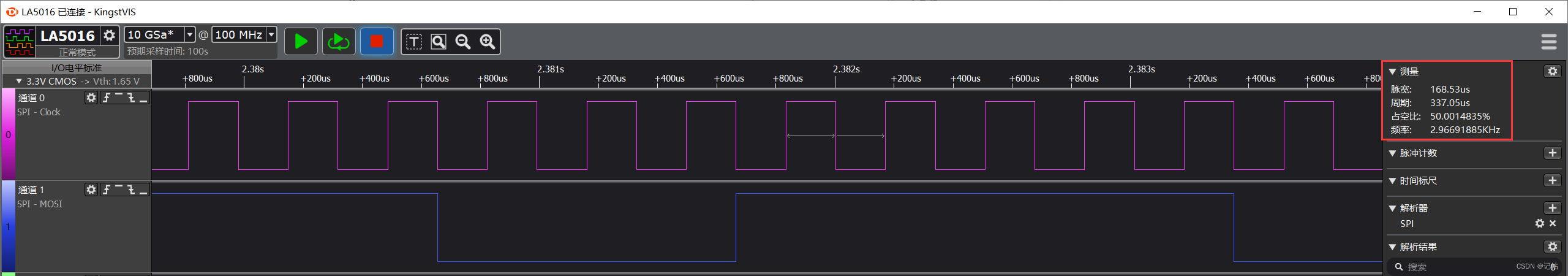

DRAM Burst 是指在 DRAM 存取数据时的一种优化方式。它利用了 DRAM 的内部结构,允许在一个存取周期内连续传输多个数据。这样做可以提高内存的效率,因为DRAM存取数据时,会有一定的固定开销,比如预充电和访问延迟。Burst模式通过在一个存取周期内传输多个数据项,减少了这些固定开销的重复发生,从而提高了整体数据传输速率。

在一个 burst 传输中,DRAM控制器首先发出一个存取请求,然后 DRAM 芯片会顺序传输请求的数据,而不需要每次请求都单独传输。这个连续的数据传输过程可以是按行(row)或列(column)的方式,取决于 DRAM 的内部结构和控制器的设置。

Burst 模式能够有效地利用内存系统的带宽,提高数据传输速率,特别是在需要连续读取大量数据时,能够显著减少存取延迟,提升系统性能。

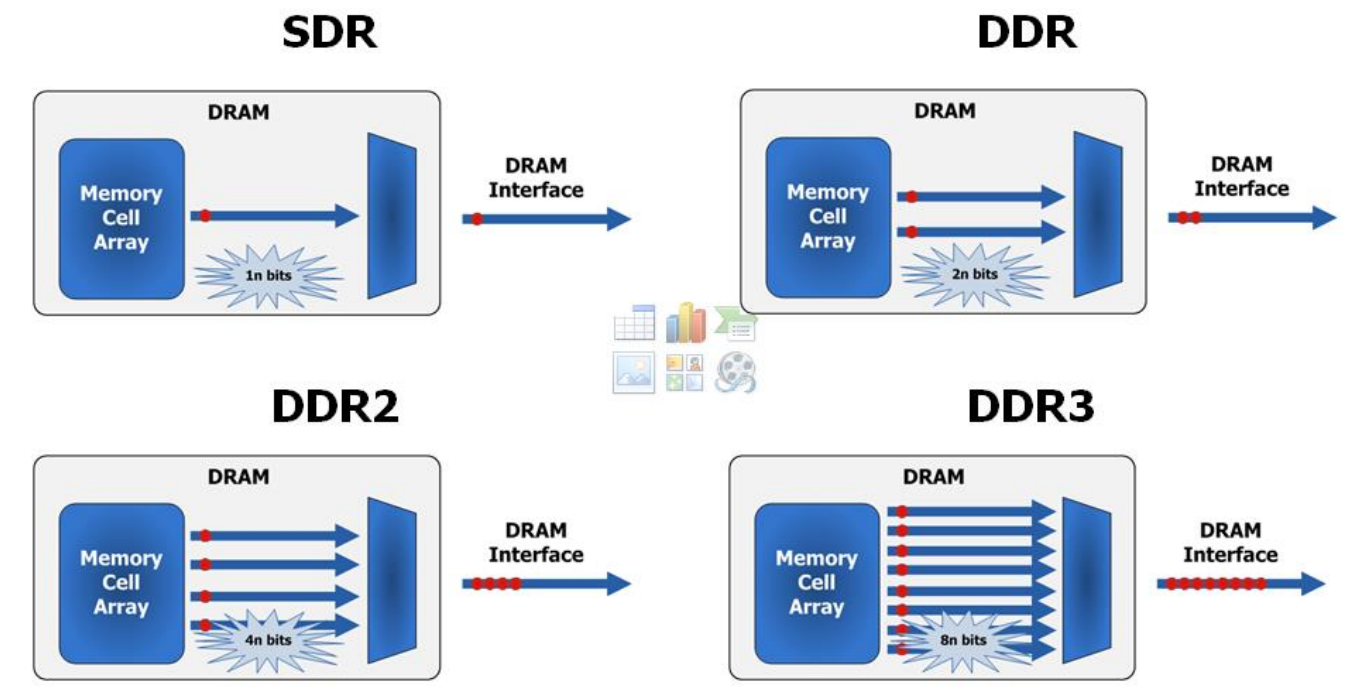

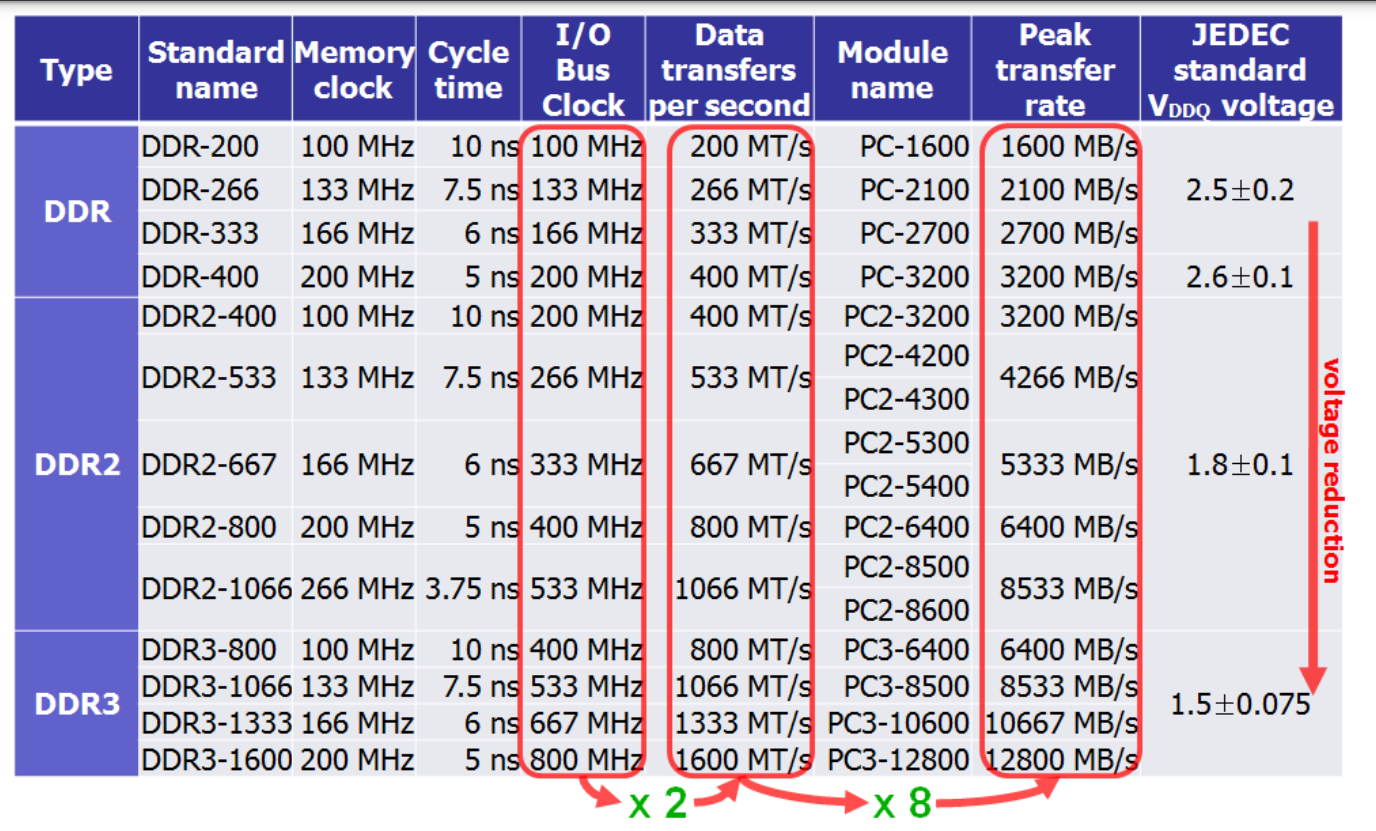

从 DRAM 阵列中读出多少数据?

基于 DDR 信息的 DRAM 规格:

📌 [ 笔者 ] 王亦优 | 雷向明

📃 [ 更新 ] 2023.3.

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考文献: - Computer Organization and Design, D. Patterson and J. Hennessy, (ARM edition), Elsevier (or Morgan Kaufmann), 2010. - J.L. Hennessy and D.A. Patterson, Computer Architecture: A Quantitative Approach, 4th edition, Morgan Kaufmann, 2006 - ARM System Developer’s Guide, A. Sloss, D. Symes, and C. Wright, Morgan Kaufmann,2004 |