一、概述

本文主要介绍GPIO 作为输出时的寄存器配置。包括时钟配置,输出模式配置。以STM32F10xxx系列为例,配置PA8、PD2端口作为输出,输出高/低电平。

二、配置流程

1)GPIO外设时钟

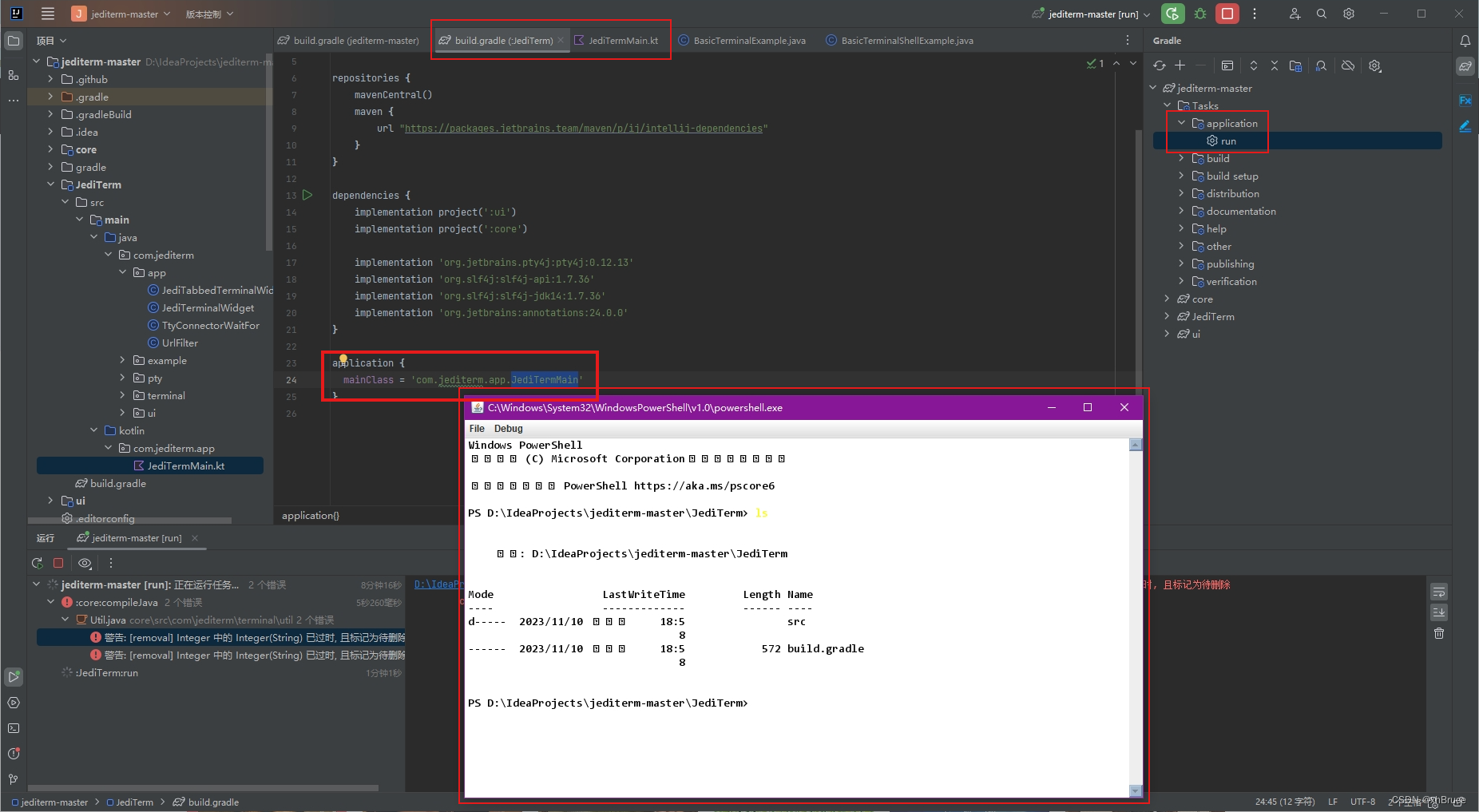

通过查找STM32F10xxx中文参考手册得知,GPIO PORT口的时钟配置在RCC_APB2ENR寄存器的第2~6位,如下图:

使能PORTA 和 PORTD 的时钟:

RCC->APB2ENR |= 1 << 2;//enable portA clk

RCC->APB2ENR |= 1 << 5;//enable portD clk2) 配置GPIO模式

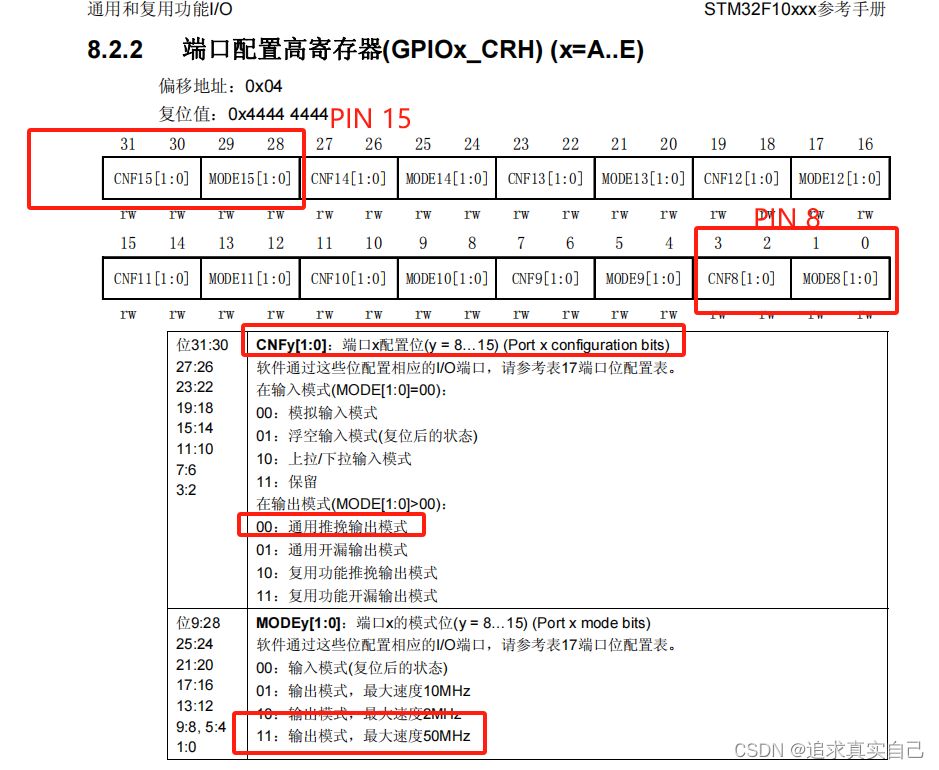

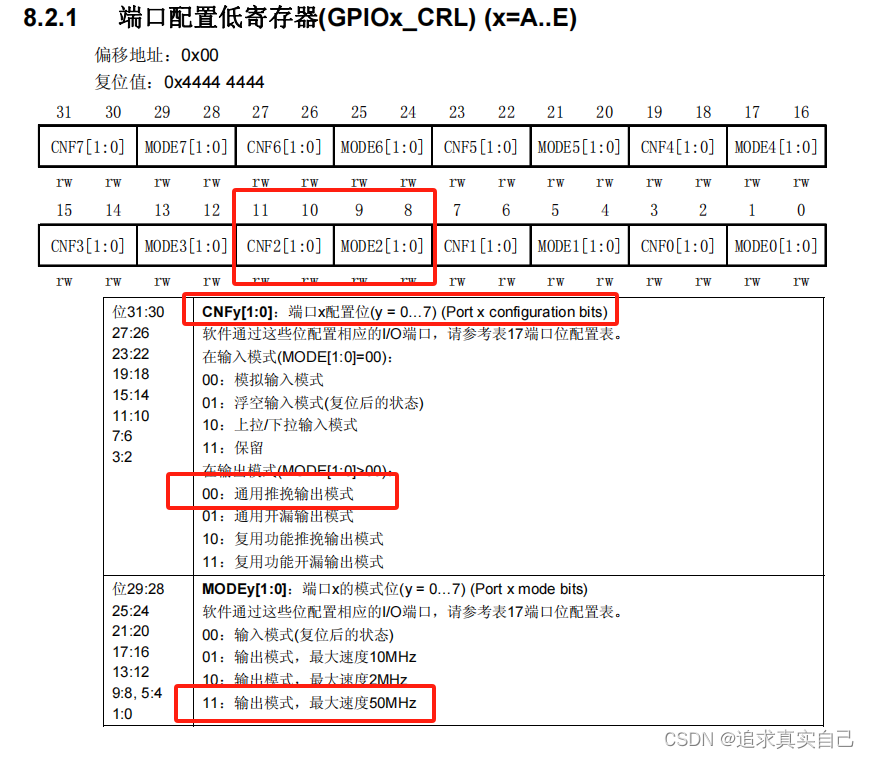

PORT A的PIN 8和PORT D的PIN 2配置为通用推挽(PP)输出模式,GPIO速度配置为50MHZ。CRL寄存器配置的是PIN0~7,CRH寄存器配置的是PIN8~15。

GPIOA->CRH &= 0xFFFFFFF0;

GPIOA->CRH |= 0x3; //GPIO PORTA PIN 8 cfg PP & output 50MHZ

GPIOD->CRL &= 0xFFFFF0FF;

GPIOD->CRL |= 0x3 << 8; //GPIO PORTD PIN 2 cfg PP & output 50MHZ3)配置 IO口输出电平

有如下几种方式:

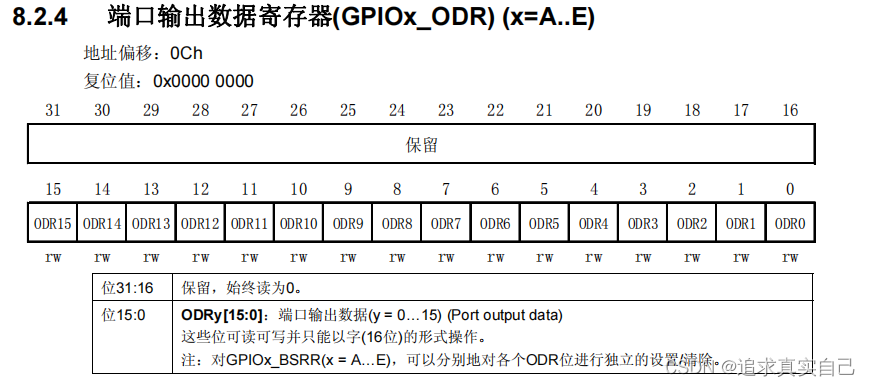

a)配置ODR寄存器

GPIOA->ODR |= 1 << 8;//GPIO PORT A PIN8 cfg output level '1'

GPIOA->ODR &= ~(1 << 8);//GPIO PORT A PIN8 cfg output level '0'

GPIOD->ODR |= 1 << 2;//GPIO PORT D PIN2 cfg output level '1'

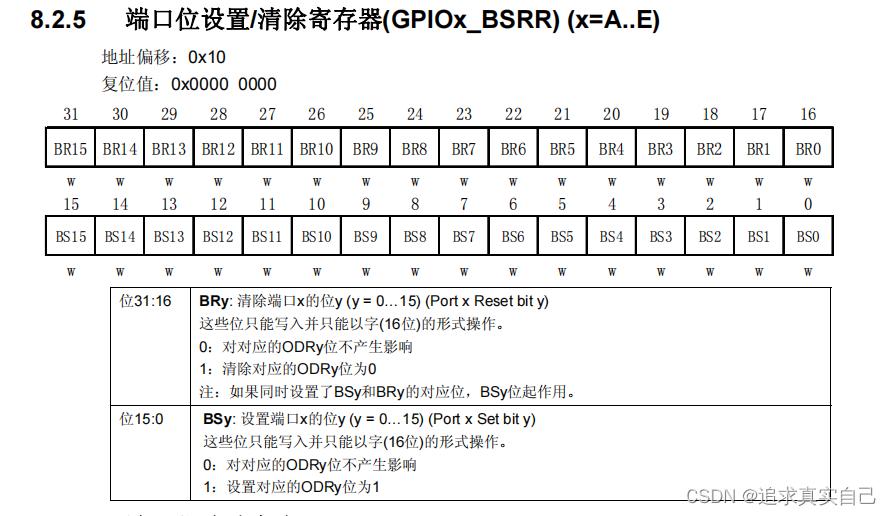

GPIOD->ODR &= ~(1 << 2);//GPIO PORT D PIN2 cfg output level '0'b)配置BSRR和BRR寄存器

GPIOA->BSRR = 1 << 8; //GPIO PORTA PIN8 cfg output level '1'

GPIOA->BSRR = 1 << 24; //GPIO PORTA PIN8 cfg output level '0'

GPIOD->BSRR = 1 << 2; //GPIO PORTD PIN2 cfg output level '1'

GPIOD->BSRR = 1 << 18; //GPIO PORTD PIN2 cfg output level '0'注:如果出现同时配置BR2和BS2为1即端口需要置位且需要复位,则此时置位生效,电平输出为1。

GPIOA->BRR = 1 << 8; //GPIO A PIN 8 cfg output level '0'

GPIOD->BRR = 1 << 2; //GPIO D PIN 2 cfg output level '0'三、ODR和BSRR、BRR的区别

ODR 可读写,相对耗时序,BSRR和BRR只能写,但不耗时序。由上可知配置PA8输出电平。

ODR寄存器,配置的时候只需配置端口8,其它bit位要保持原样。因此操作如下:

GPIOA->ODR |= 1 << 8;

读取ODR寄存器->或运算->写入

(GPIOA->ODR |= 1 << 8

->

GPIOA->ODR = GPIOA->ODR | (1 << 8))而BSRR和BRR寄存器只需:

GPIOA->BSRR = 1 << 8;

GPIOA->BRR = 1 << 8;赋值即可,因为如下特性:

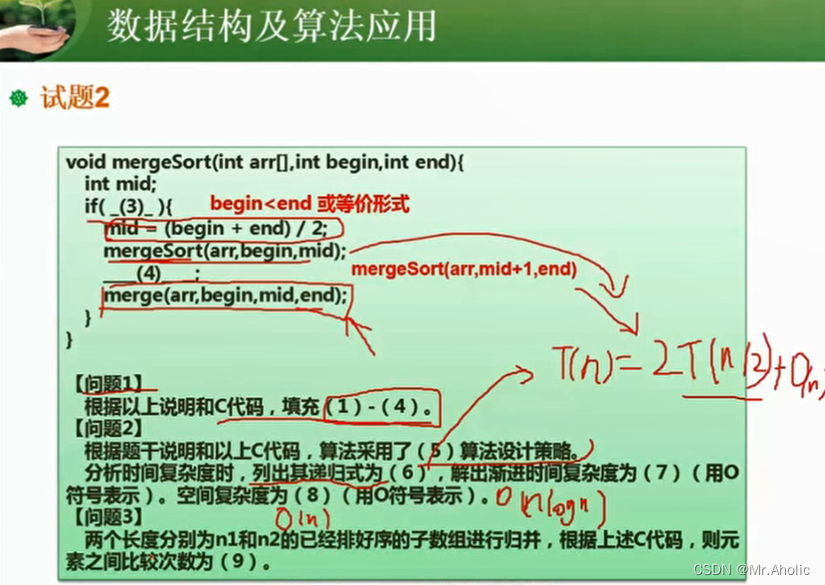

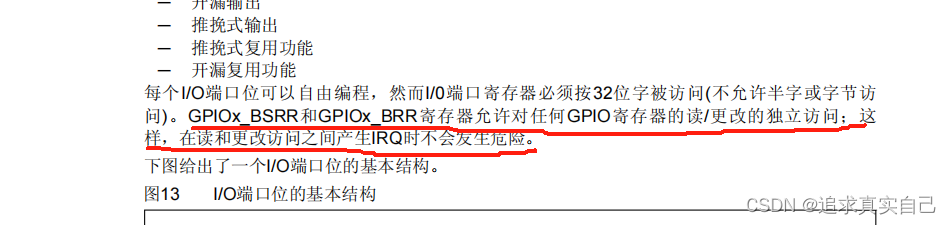

在手册上有如下描述:

即用BSRR和BRR去改变管脚状态的时候,没有被中断打断的风险。也就不需要关闭中断。因为BSRR寄存器的操作只有一个动作赋值。