*本文信息主要来源于书籍《鲲鹏处理器架构与编程》以及论文《Kunpeng 920: The First 7-nm Chiplet-Based 64-Core ARM SoC for Cloud Services》 *

笔者已然写了一篇上述论文的分析博客,但尚觉论文内容对chiplet架构描述不够清晰,因此查阅《鲲鹏处理器架构与编程》一书,借此文以记录补充内容。

由于书是2020年出版,论文是由鲲鹏设计团队于2021年发表,很多命名、表述不相一致,鄙人觉得以论文描述为主,论文分析请移步:

论文解析——Kunpeng 920…

指令集架构

待补充

处理器chiplet架构

鲲鹏920分为CCL集群和ICL集群,两类集群可组成超级集群,每个超级集群均是一个die,通过集群的组合可以构成不同系列的产品。

超级集群内通过片上总线互连,die间通过SLLC互连,而整个芯片互连则通过Hydra接口连接。由于超级内核集群(CPU-compute die)没有Hydra接口,因此如果由芯片间互连需求,则必须有一个超级IO集群(Compute-IO die)。

超级内核集群(CPU-compute die)

CCL(core cluster)

POE_ICL

系统配置的硬件加速器,一般用作分组顺序整理器、消息队列、消息分发或者实现某个处理器内核的特定任务。

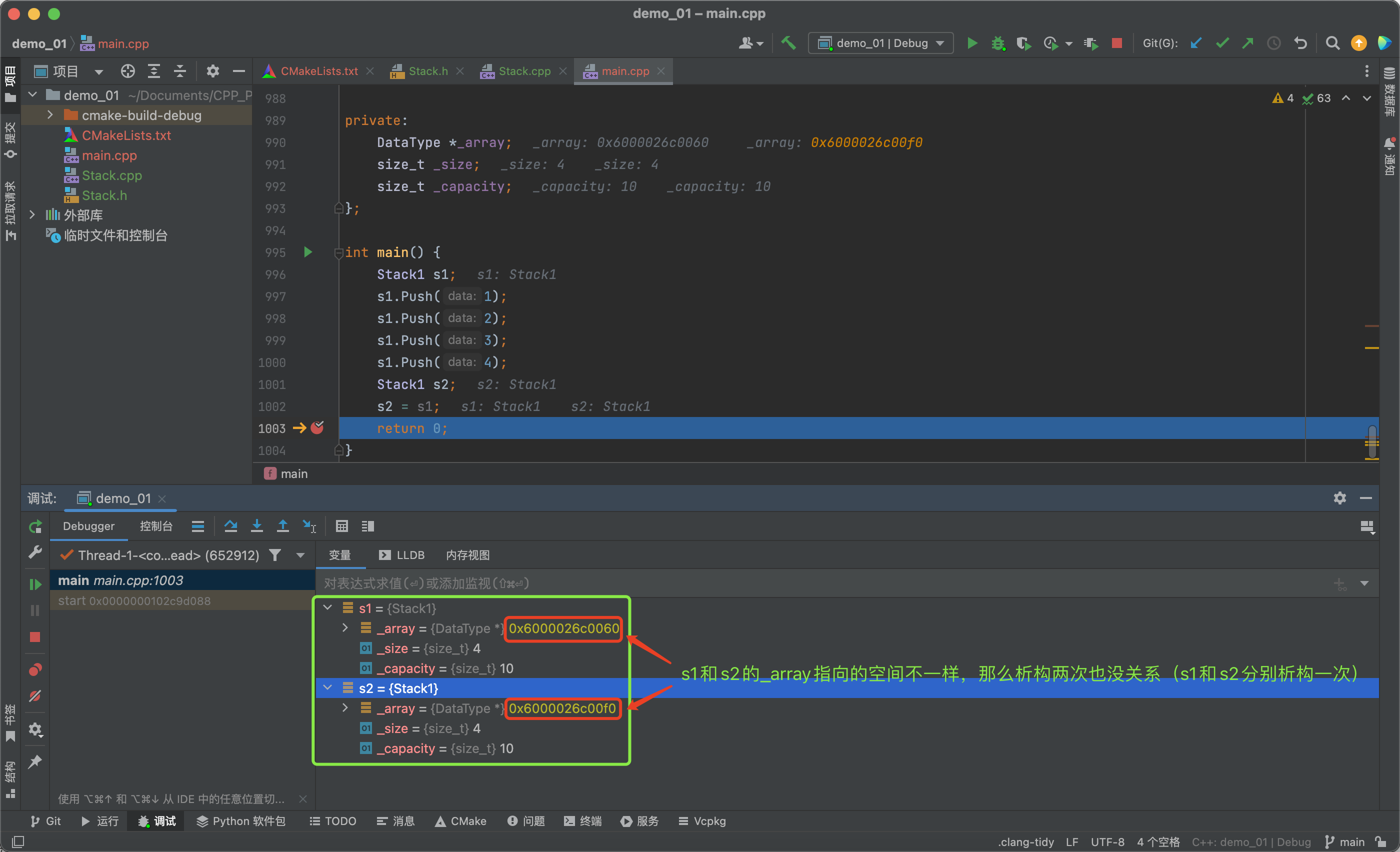

主存系统:DDR控制器 + Hydra根代理(HHA)

在鲲鹏处理器架构中,由主存系统维护die间和片间数据一致性,该一致性的协议标准即为HCCS。

超级IO集群(Compute-IO die)

超级IO集群由4个ICL、1个Hydra接口模块、一个独立的智能管理单元(IMU)组成。

一个超级IO集群中包含多个类型的ICL,如网络ICL、PCIe ICL等

ICL的内部结构

每个ICL包含系统总线接口、系统存储管理单元SMMU(可选)、用于初始化的系统控制部件(由firmware使用)、若干调度器、分发器等

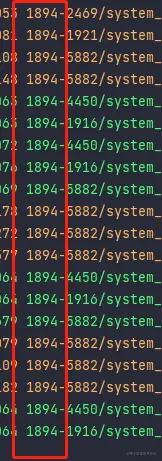

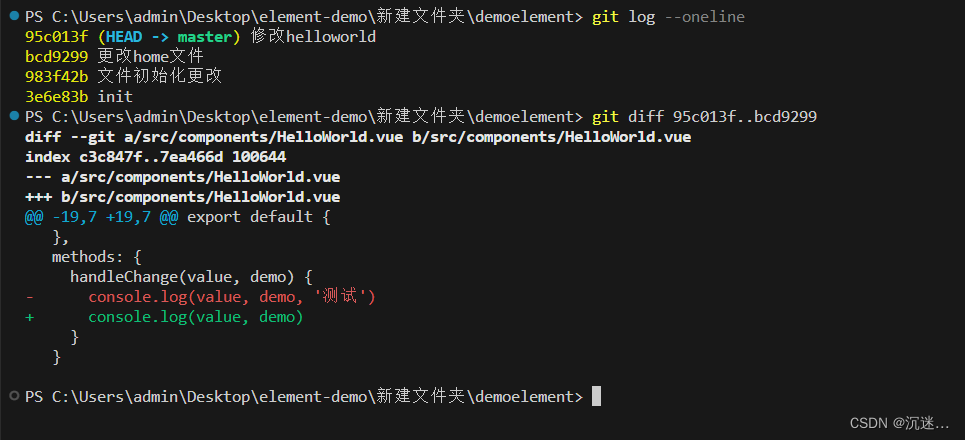

如图是compute-IO die的ICL数据流

HAC_ICL:海思自研加速控制器

除了ICL的基本模块,主要集成了硬件安全加速引擎、压缩/解压加速引擎等

IO_MGMT_ICL:集成了USB、RAS等加速引擎的组合部件

IMU

智能管理单元,负责整个芯片管理的部件,独立于鲲鹏处理器的计算应用系统。

die内互连网络(NoC)

每个超级集群内的子系统通过ring Bus互连互通,结合各类数据传输接口、管理单元共同构成了片上网络。

完整的片上网络由环总线、SLLC、调度器(scheduler)和分发器(Dispatch)等模块组成。

环总线

环总线通过交叉站(Cross Station, CS)的节点互连而成,每个交叉站保证片上系统内部个设备的传输通道按一定的顺序正确且高效的传输。CPU-compute die和Compute-IO die均通过ring bus互联。

上电后环总线无需配置即可工作。

调度器

ICL特有器件,调度以及汇集ICL内多个设备的访存请求并有序传递到SMMU中,经过地址转换后接入ring bus的CS,将数据流量映入片上系统的其他部件。调度器也可以调整设备下发命令的服务质量,也可以对设备流量进行限制。

例如若设备需进行DMA访问,则则系统地址空间主动发起读写操作请求,并向调度器发出汇聚这些操作的请求,系统管理单元处理这一请求后使用物理地址访问总线。

分发器

ICL特有器件,对物理地址译码,以便每个设备访问设备寄存器空间。

和调度器相对应,从NoC中其他设备来的访问请求经分发器分发至正确的设备进行处理;分发器可以通过内部的数据缓冲器平滑高速访问与低俗设备间的速率差异。

die间互连:SLLC接口

超级集群(die)间通过超级集群链路层连接器(SLLC)互连。

SLLC连接多个die的环总线通路,将一个die的环总线数据按照约定的路由传输到另一个die的环总线中。

由于die内数据流量大于die间的流量,因此SLLC的带宽一般小于ring bus提供的最高带宽。

由于ring bus的data width更大,因此SLLC需要将数据分组打包并压缩后才进行传输。

片间互连:Hydra接口

Hydra是支持片间扩展的华为私有高性能接口,实现多芯片在PCB板上互连,并实现多芯片间的数据一致性高效互连互通。

该接口由协议适配层和链路层两部分模块组成,同时集成了华为自研的维护多集群数据一致性的协议(Huawei Cache Coherency System,HCCS),物理层则使用高速serdes通道实现。

协议适配层(Protocol Adapter, PA)

PA模块主要完成ARM架构CHI协议和Hydra之间的适配功能。

CHI协议是die间和片间使用的总线协议。

PA模块的主要特征

- CHI和Hydra间数据格式的转换

- 片间发送端请求缓冲区管理

- 片间接收端地址相关性检测

- 片间数据一致性处理

- 与环总线以及链路层(HLLC)间的流控处理

- 片间流量统计

Hydra接口链路层控制器(HLLC)

完成Hydra协议数据在serdes物理通道上的数据格式适配;在发送端完成Hydra协议中个逻辑通道的数据调度和CRC嵌入;在接收端完成CRC校验和来自发送端各通道的数据分发

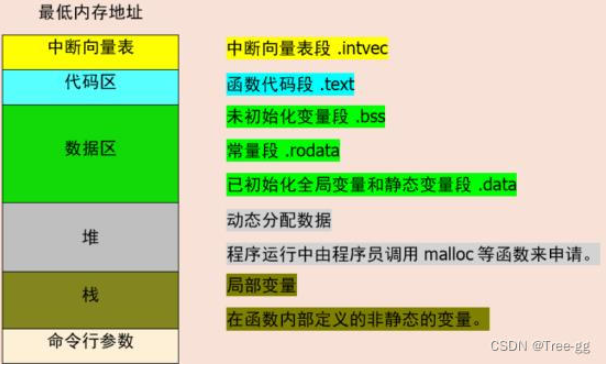

NoC中的地址译码组件

为了保证各集群间的互访能正确实现,由ring bus中各节点中的地址译码器组成了映射和译码组件。

该组件可以根据访问的属性和地址识别传输目的地,并产生正确的目标表示(TgtID)用于片上网络的路由判断,以保证请求的正确传输。

鲲鹏架构将寻址译码分为3个层次,逐级的将访问分配到对应设备

- 一级译码集成在访问请求进入ring bus接口前,译码指示正确的环总线端口

- 二级译码集成在各ICL的分发器内,译码指示ICL内正确的分发器出口

- 三级译码继承咋使用共享总线的分发器出口处,译码结果指示具体的设备

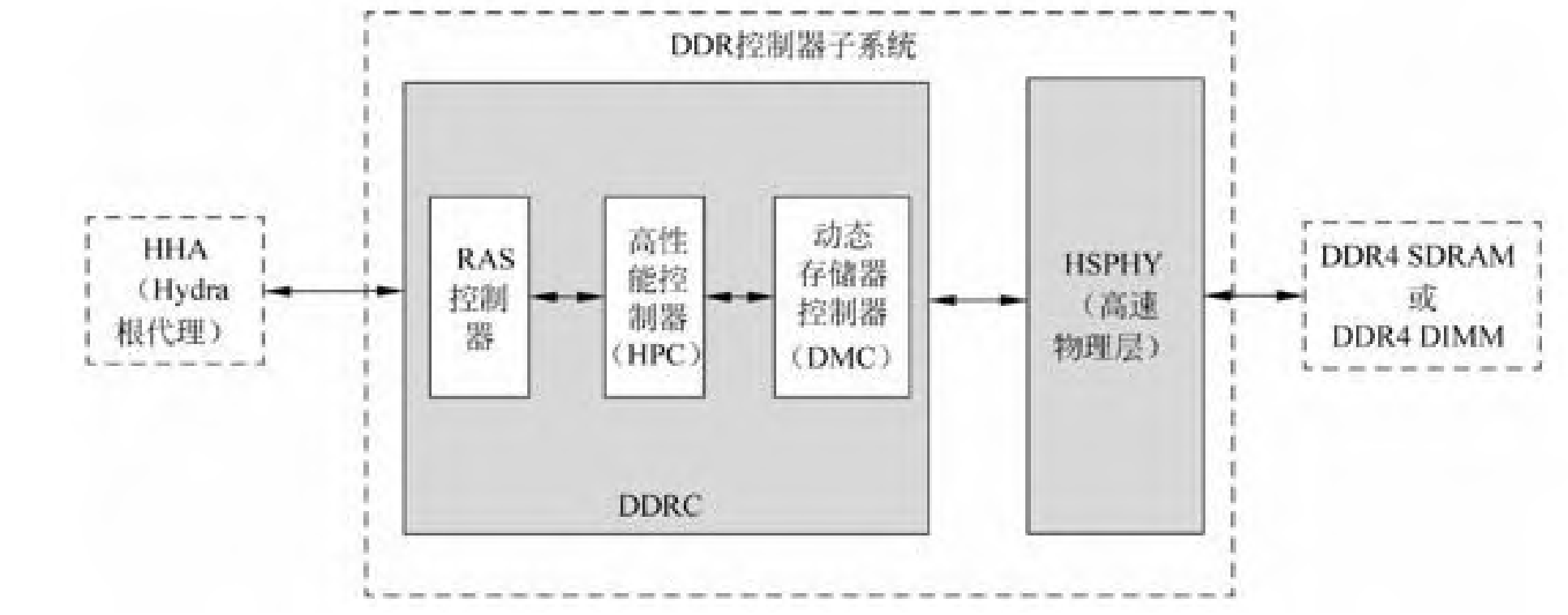

chiplet封装

采用CoWoS封装,die间双向通信带宽高达300GB/s以上

处理器的NUMA架构

待补充