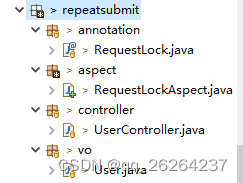

1 xilinx原语

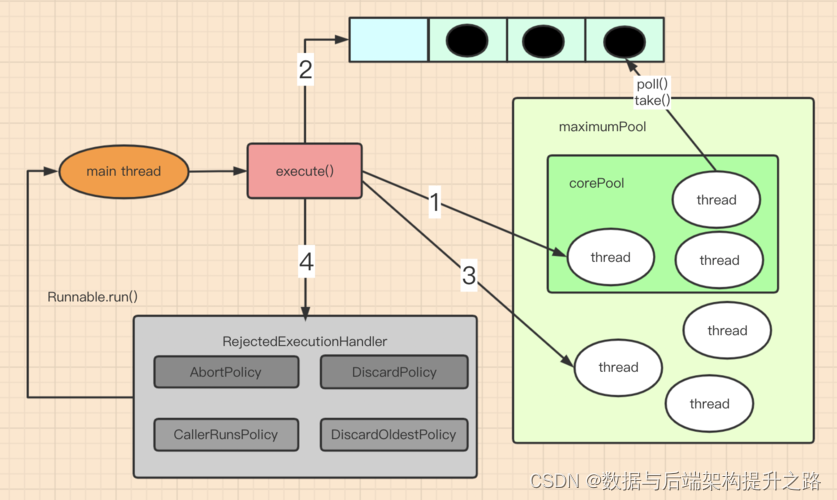

在 7 系列 FPGA 中实现 RGMII 接口需要借助 5 种原语,分别是:IDDR、ODDR、IDELAYE2、ODELAYE2(A7 中没有)、IDELAYCTRL。其中,IDDR和ODDR分别是输入和输出的双边沿寄存器,位于IOB中。IDELAYE2和ODELAYE2,分别用于控制 IO 口输入和输出延时。同时,IDELAYE2 和 ODELAYE2 的延时值需要使用原语 IDELAYCTRL 来进行校准。另外,需要注意的是,在 7 系列器件的 HR Bank 中没有 ODELAYE2,只有在 HP BANK 中才有 ODELAYE2。1).IDDR IDDR将输入的双边沿DDR信号,在输出端恢复为两个并行单边沿SDR信号。IDDR的原语如下。详细参数可参考UG471。

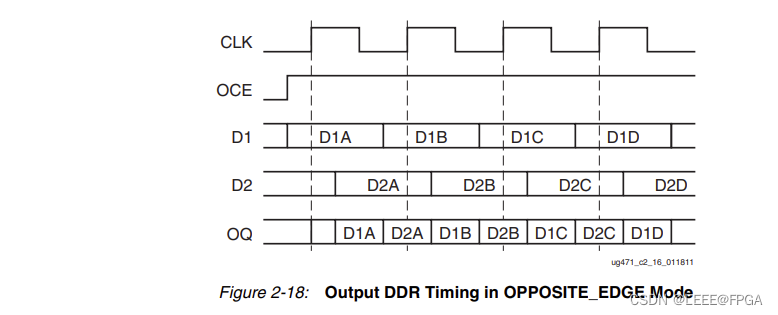

2 ODDR

ODDR 使用 ODDR 将 TXC 同一个时钟周期内的两个 SDR 信号分别通过上升沿和下降沿输出为 DDR 信号。

3 OPPOSITE_EDGE Mode

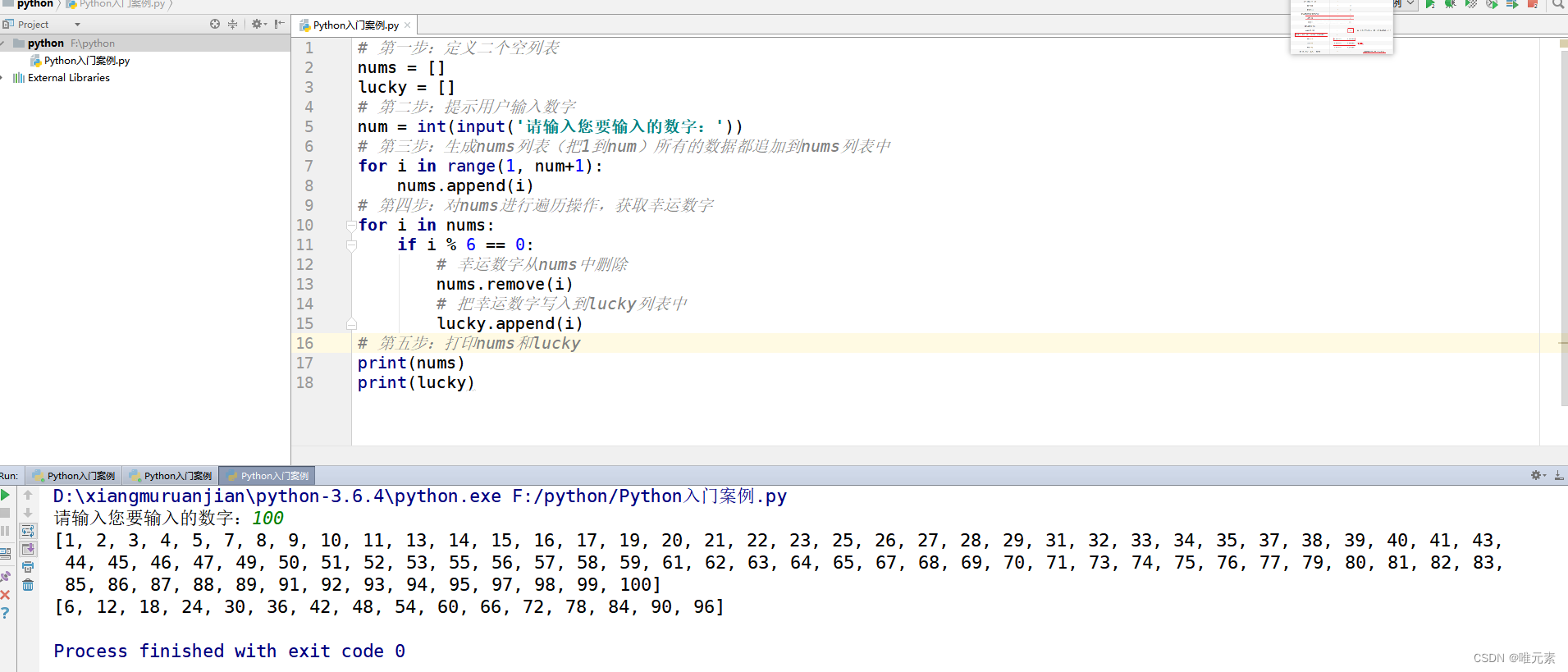

在OPPOSITIE_EDGE模式中,时钟(CLK)的两个边沿用于以两倍的吞吐量从FPGA逻辑捕获数据。这种结构类似于Virtex-6的FPGA实现。两个输出都提供给IOB的数据输入或三态控制输入。使用OPPOSITIE_EDGE模式的输出DDR的时序图如图2-18所示

4 SAME_EDGE Mode

在SAME_EDGE模式下,数据可以在同一时钟边缘上呈现