背景

在 RISC-V指令集中,一共有 6 条有条件跳转指令,分别是 beq、bne、blt、bltu、bge、bgeu。如下是它们的定义与接口

= BEQ rs1, rs2, imm

≠ BNE rs1, rs2, imm

< BLT rs1, rs2, imm

≥ BGE rs1, rs2, imm

< unsigned BLTU rs1, rs2, imm

≥ unsigned BGEU rs1, rs2, imm

场景分析

在现代计算密集型任务的芯片架构设计中,SIMD, SIMT体系非常常见,比如我们会先把某个计算任务拆解为一系列的芯片指令,然后分配给芯片的不同core,不同thread来执行这些指令,即同一套指令,多个不同线程执行。但是某些输入数据情况下或者某个指令中只需要其中某个core或thread执行,其它则跳转到另外的分支执行,这时候我们就需要增加跳转指令来实现这个操作。

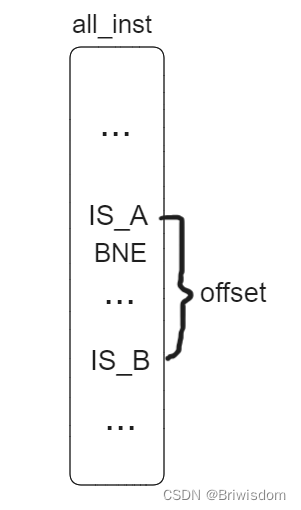

假设指令A和指令B中间差了offset条指令,我们想要core_id%4=0的core从指令A地方往下顺序执行到指令B,而core_id%4 !=0的core则从指令A直接跳到指令B处再顺序执行剩余指令。这时候我们应该怎么写跳转指令呢?需要考虑下面两个问题:

1)在哪里加跳转指令?

当然是在指令A结束后执行跳转指令,如果符合跳转条件,就跳过A,B之间的指令。

2)怎么加跳转指令?

跳转指令实际就是判断语句,因为这个场景需要不相等时候跳转,所以用到的是BNE指令。

然后我们需要考虑BNE的指令接口:rs1, rs2, imm。BNE的这3个参数是指如果rs1 != rs2, 则传进来一个imm立即数。imm在这里对应的就是指令A,B之间的偏移指令条数offset。

接下来,根据实际场景,rs1, rs2可以是寄存器的id号,一般芯片设计中会有两种寄存器:GPR(通用寄存器)、CSR(条件状态寄存器)。我们可以通过CSR获得当前运行状态下的core_id号,通过GPR寄存器放置判断的取模数字4。

最后,跳转指令就是这样实现:

(offset在生成指令集时候得到,然后作为立即数传递给BNE指令。实际生成代码时候,可以在指令B开始位置计算一下中间跳转的offset, 然后修改到前面生成的跳转指令参数里)

BNE src1, src2, offset

CSR[src1] = core_id,

GPR[src2] = 4,

inst_set[core_num, inst_len] 表示当前core_id执行到第几条指令, 假设idx指到指令A位置。

翻译如下:

if CSR[src1] != GPR[src2]

inst_set[core_id, idx] = inst_set[core_id, idx] + offset示意图如下: