AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

JESD204B相关IP端口信号 : AD9371 官方例程HDL JESD204B相关IP端口信号

裸机程序配置 AD9528、AD9371、FPGA IP: AD9371 官方例程裸机SW 和 HDL配置概述(一)

裸机程序配置 AD9528、AD9371、FPGA IP: AD9371 官方例程裸机SW 和 HDL配置概述(二)

裸机程序配置 AD9528、AD9371、FPGA IP: AD9371 官方例程裸机SW 和 HDL配置概述(三)

文章目录

- 前言

- 一、xilinx platform

- 二、AD9528

- 三、CLKGEN IP

- 四、JESD 链路层初始化

- 五、ADXCVR 物理层初始化

前言

官方例程主函数需要配置和初始化 AD9528、AD9371、FPGA IP,打开DDS 或者通过DMA 搬运发送和接收数据

一、xilinx platform

打开 指令和数据 Cache ,初始化 platform(包含 SPI 和 GPIO)

Xil_ICacheEnable();

/* Enable the instruction cache. */

Xil_DCacheEnable();

ret = platform_init();

if (ret != 0) {

printf("error: platform_init() failed\n");

goto error_0;

}

二、AD9528

通过AD9528复位引脚,复位 AD9528

通过 VCXO REFA outFrequency_Hz[1] ,得到 PLL1 PLL2 output 0-13 和 sysref 各个配置参数,存入 clockAD9528_device

通过 SPI 初始化 AD9528 的 PLL1 PLL2 output 和 sysref

error = AD9528_resetDevice(clockAD9528_device);

if (error != ADIERR_OK) {

printf("AD9528_resetDevice() failed\n");

error = ADIERR_FAILED;

goto error_1;

}

error = AD9528_initDeviceDataStruct(clockAD9528_device,

clockAD9528_device->pll1Settings->vcxo_Frequency_Hz,

clockAD9528_device->pll1Settings->refA_Frequency_Hz,

clockAD9528_device->outputSettings->outFrequency_Hz[1]);

if (error != ADIERR_OK) {

printf("AD9528_initDeviceDataStruct() failed\n");

error = ADIERR_FAILED;

goto error_1;

}

/* Initialize the AD9528 by writing all SPI registers */

error = AD9528_initialize(clockAD9528_device);

if (error != ADIERR_OK)

printf("WARNING: AD9528_initialize() issues. Possible cause: REF_CLK not connected.\n");

三、CLKGEN IP

通过axi_clkgen_init 赋值给 rx_clkgen 等

通过参考时钟和需要生成目标时钟,得到配置参数,配置到 IP的MMCM中,利用 MMCM 得到所需时钟,详见第二部分

status = axi_clkgen_init(&rx_clkgen, &rx_clkgen_init);

status = axi_clkgen_init(&tx_clkgen, &tx_clkgen_init);

status = axi_clkgen_init(&rx_os_clkgen, &rx_os_clkgen_init);

status = axi_clkgen_set_rate(rx_clkgen, rx_div40_rate_hz);

status = axi_clkgen_set_rate(tx_clkgen, tx_div40_rate_hz);

status = axi_clkgen_set_rate(rx_os_clkgen, rx_os_div40_rate_hz);

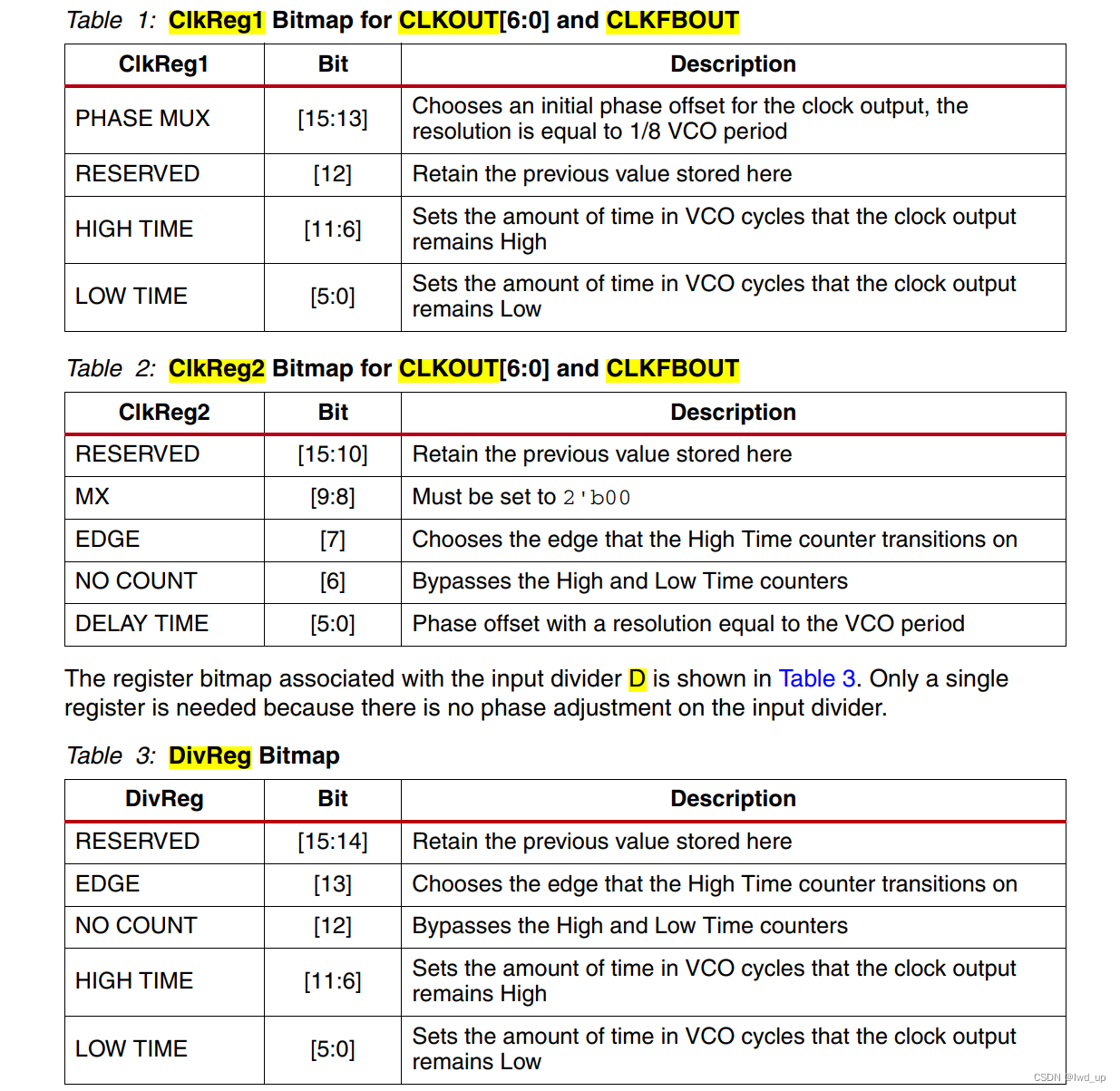

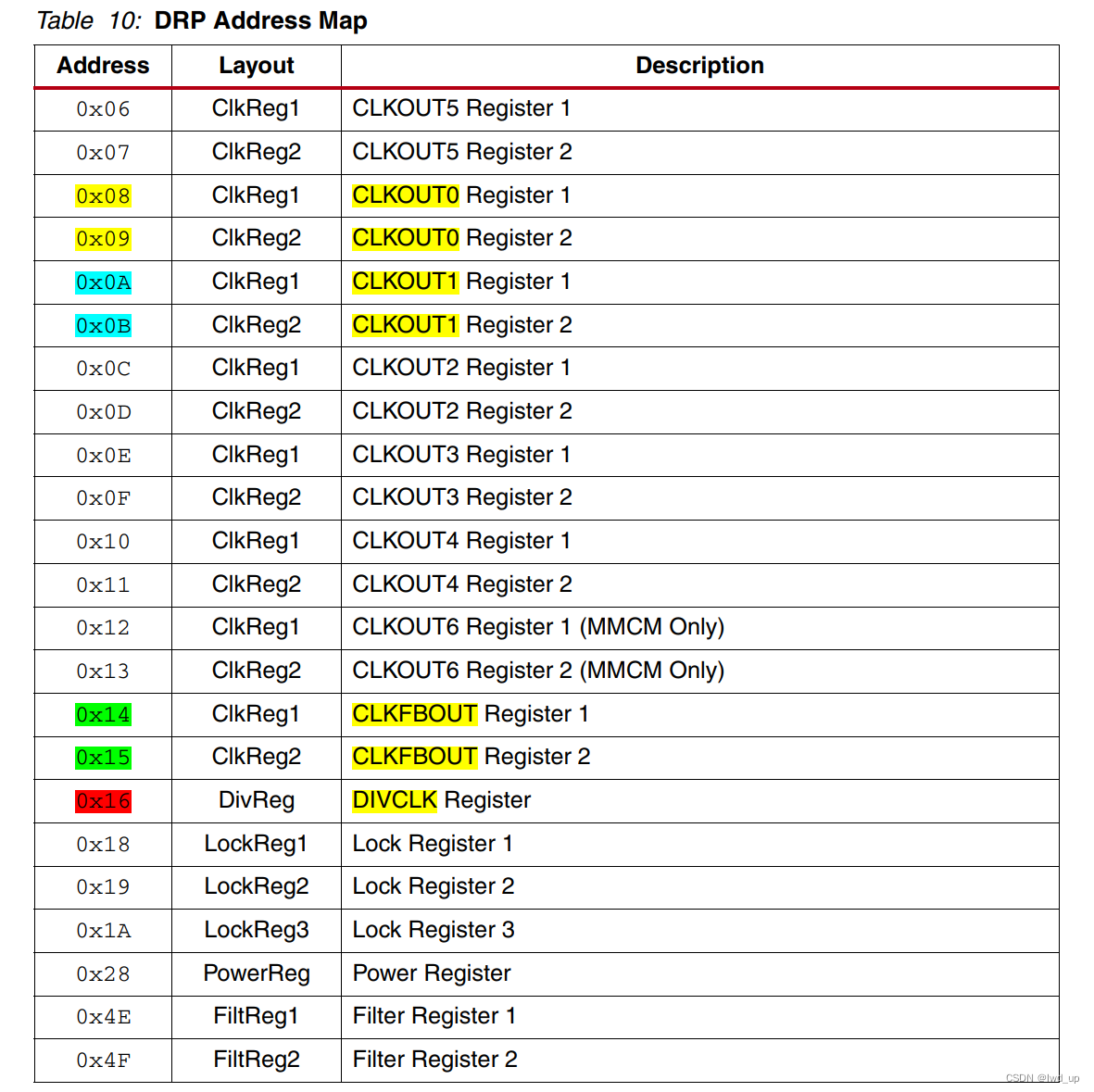

利用axi_clkgen_calc_params(clkgen, clkgen->parent_rate, rate, &d, &m, &dout); 计算MMCM中的 M、 D、 O

将 dout ,也就是 O0 写入 MMCM_REG_CLKOUT0_1 和 MMCM_REG_CLKOUT0_2 (0x08 和 0x09,OUT0的DRP地址)

axi_clkgen_calc_clk_params(dout, &low, &high, &edge, &nocount);

axi_clkgen_mmcm_write(clkgen, MMCM_REG_CLKOUT0_1, (high << 6) | low, 0xefff);

axi_clkgen_mmcm_write(clkgen, MMCM_REG_CLKOUT0_2, (edge << 7) | (nocount << 6),0x03ff)

得到的 D 和 M 类似 O0,写入相应的寄存器中

参考 XAPP888

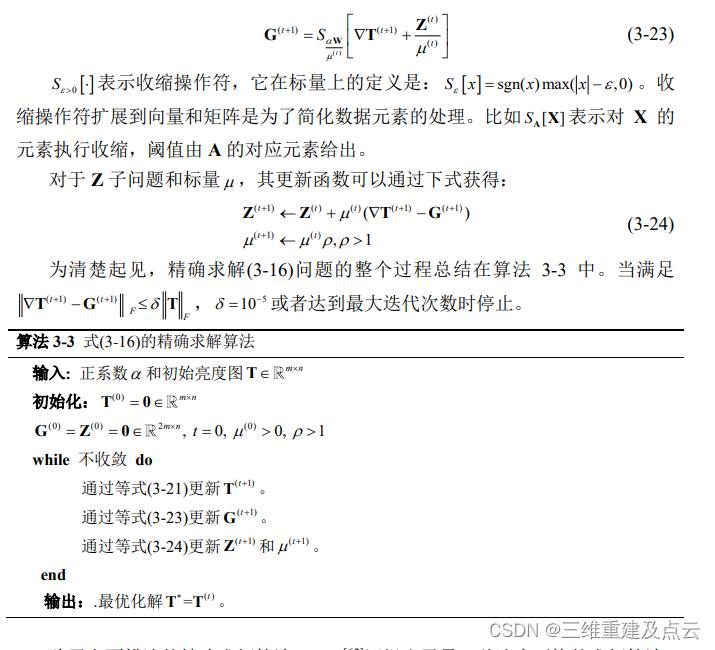

四、JESD 链路层初始化

初始化 tx_jesd 、rx_jesd 等,并把 octets_per_multiframe 和 octets_per_frame 配置给IP核,octets_per_multiframe 除以 4,得到 up_cfg_beats_per_multiframe ,在链路层的LMFC中使用

status = axi_jesd204_rx_init(&rx_jesd, &rx_jesd_init);

status = axi_jesd204_tx_init(&tx_jesd, &tx_jesd_init);

status = axi_jesd204_rx_init(&rx_os_jesd, &rx_os_jesd_init);

五、ADXCVR 物理层初始化

初始化 tx_adxcvr、rx_adxcvr 等,配置物理层 sys_clk_sel、 out_clk_sel 、LPM_DFE_N 等参数,通过 adxcvr_clk_set_rate(xcvr, xcvr->lane_rate_khz, xcvr->ref_rate_khz) 计算并配置(通过DRP) QPLL 、CPLL、 t/rx_out_div 和 clk25M ,得到正确的 lane rate

status = adxcvr_init(&rx_adxcvr, &rx_adxcvr_init);

status = adxcvr_init(&tx_adxcvr, &tx_adxcvr_init);

status = adxcvr_init(&rx_os_adxcvr, &rx_os_adxcvr_init);