文章目录

- 0 前言

- 1 如何显示信号高位的0

- 2 统计信号的上升沿、下降沿

- 3 合并信号

- 4 将多个fsdb文件合并成一个

0 前言

分享几个这段时间学到的verdi操作

1 如何显示信号高位的0

这个可能对一些有强迫症的有帮助吧

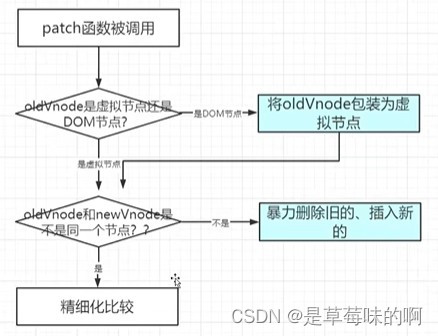

nand相关的操作,有一些特定的cmd,比如 read cmd是 00-30h,我希望波形上显示的就是 00,可以这样操作

随便截取一段波形,如下

框的部分值显示了一个 a

在 nWave 菜单栏依次点击 View --> Leading Zeros,之后就可以补全高位的 0

看看效果

a变成了0a

2 统计信号的上升沿、下降沿

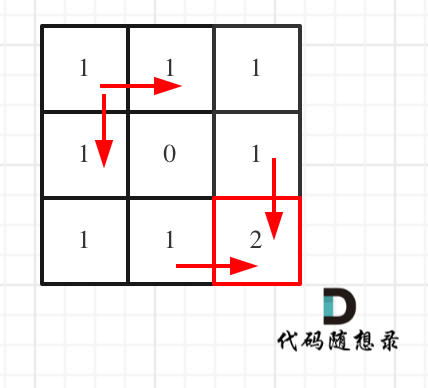

对于nand的读写,有时候可能需要量一个往nand读写了多少的data,刚开始是先量一下clk的周期,再量一下一段读或者写的时间是多长,做个除法计算数据量

但这有两个问题(我目前能想到的哈):

- 有时候中途clk可能会停掉,那要是一段一段拉波形确认简直灾难

- 有时候时钟不一定是均匀的(也就是每个周期的时长都相同),这个情况在时钟分频的时候遇到过,感兴趣的话可以自行搜索,记得是计算多个clk周期的平均数作为最终clk的周期

verdi有提供统计信号上升沿/下降沿的操作

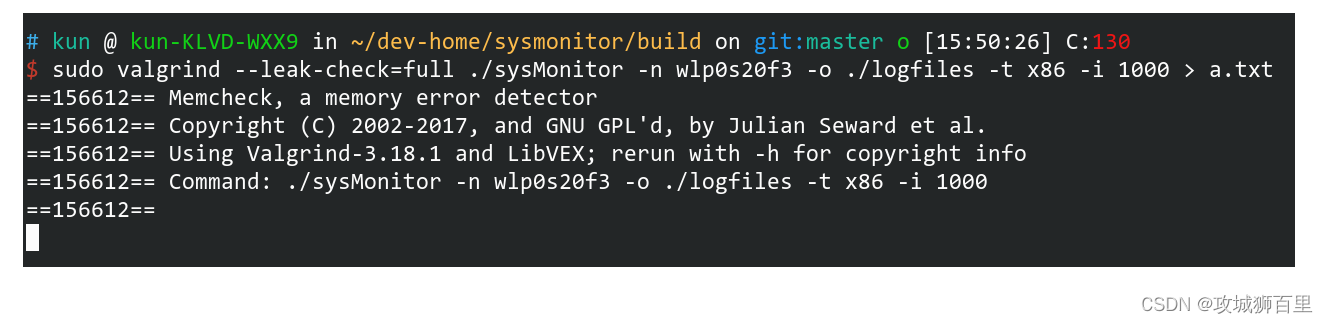

比如下面这段波形

- 先选中要统计的信号(这里选中的是DQS)

- 选中要统计的区间(鼠标左键和鼠标中建)

- 在 nWave 菜单栏依次点击 View --> Signal Event Report

弹出如下界面,分别给出上升沿和下降沿出现的次数

这个例子中上升沿有4个,下降沿有3个,因为是DDR,所以总共有7个数据,和上图的波形图一致

3 合并信号

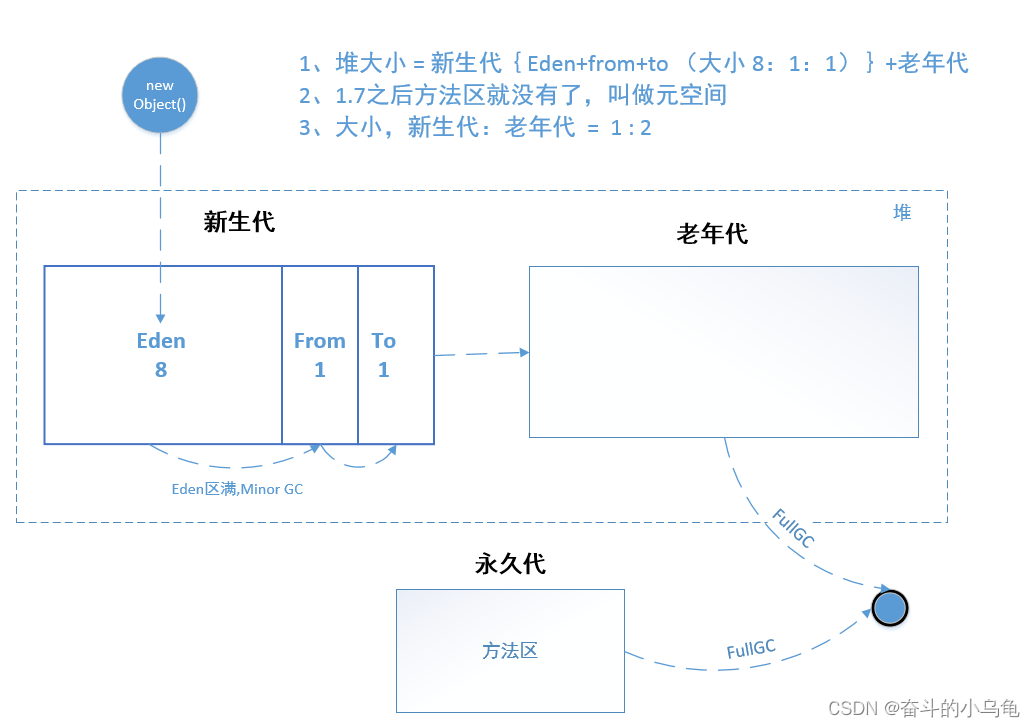

在写verilog是,有些if语句中的条件真的是又臭又长,比如下面这个例子

if((a == 1) && (b == 2) && (c != 3) && (d == 5) && (!e) && (f == 1) && (g == h ))

statement 1;

其实我只是想知道 if语句中的条件是true还是false,并不关心里面每个信号的值是多少,可以用如下方法

选中要合并的信号,在信号处点击鼠标右键,在弹出的界面中选择 Logical Operation

之后会弹出如下界面,在这个界面可以给信号之间添加上逻辑,添加完逻辑后,点击红框圈住的地方

生成了一个新的信号,只有在 CLE == 1 && DQS == 1时,logical_expression才为1

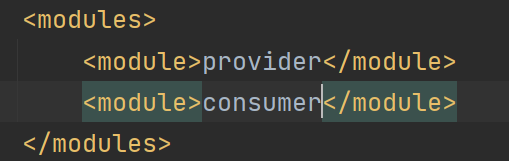

4 将多个fsdb文件合并成一个

这段时间遇到一个情况,dump信号时不能把所有的信号一次性全部dump下来,每次只能dump部分信号

这分析起来显得很麻烦,找了很久终于找到可以把不同hire的fsdb合并成一个fsdb的方法,但这种方法要保证起点和终点的时间一致??

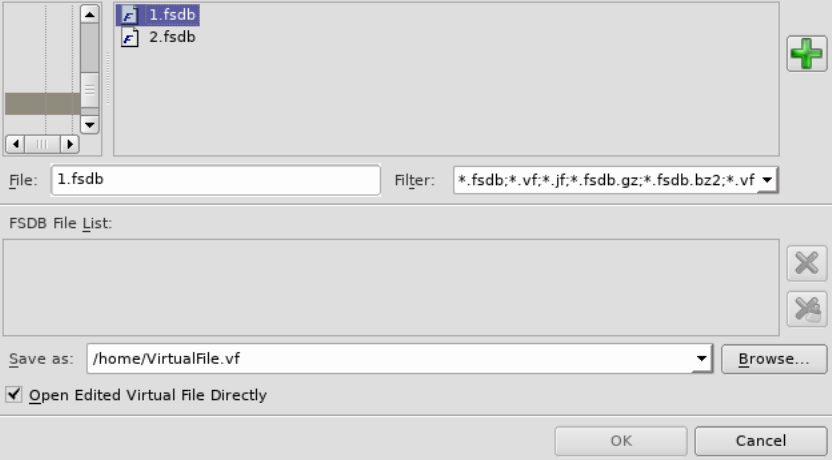

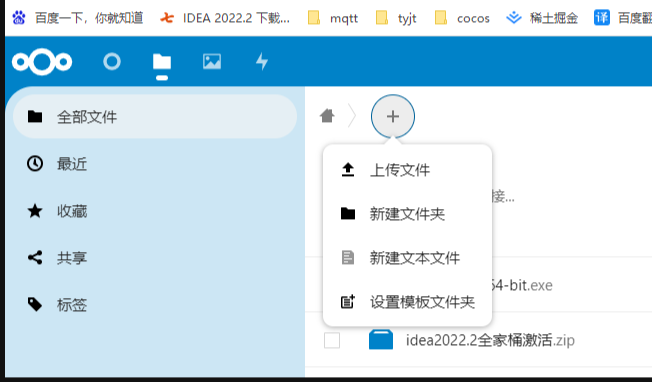

在 nWave 菜单栏依次点击 File --> Edit Virtual File

在弹出的界面中,依次双击要需要merge的fsdb文件,在 save as那一栏选择导出的目录,最后点击 OK ,就会生成一个vf文件

在 nWave 窗口选择 vf 文件,就可以拉出 两个fsdb文件中的信号了