设计流程

- 首先对项目要有一个全局的考虑,分析项目需要几个模块构成,确定各个子模块的关系和信号之间 的相互关系,然后确定模块的端口信号有哪些;

- 根据每个模块的功能并结合芯片、接口的时序手册画 出该模块能正常工作的时序波形图;

- 根据所画的波形图严格设计代码,保证设计代码的仿真结果要和 所画的波形保持一致;

- 代码编写完成后对代码进行编译,目的是检查代码中的语法错误。若代码存在语法 错误,对代码进行修改,再次编译,直至通过编译;

- 根据 RTL 代码设计合理的 Testbench 进行逻辑仿真(也称为前仿真、功能仿真);

- 使用仿真工具进行仿真,并将仿真出来的波形和 画出 的时序波形图进行对比,如果对比有差别则修改代码直至相同;

- 绑定管脚后进行分析综合、布局布线,然后下载到硬件板卡中,此时如果硬件板卡 能够正常工作,则说明前期的设计和编写的代码都正确;如果硬件板卡不能够正 常工作,查找并解决问题,反复迭代直至正确实现功能。

功能

通过按键控制一个 led 灯的亮灭,按键未被按下时 led 灯处 于熄灭状态,按键被按下时 led 灯处于点亮状态

模块设计

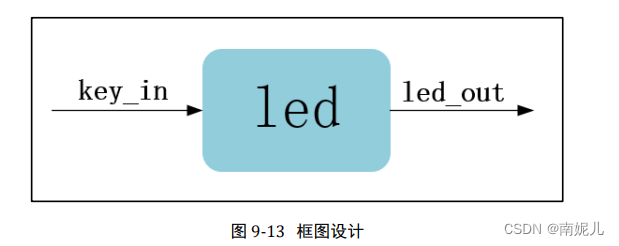

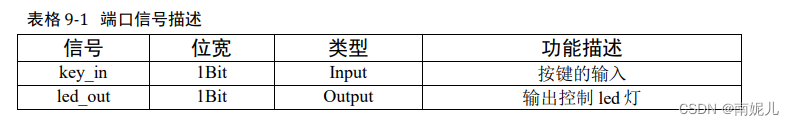

在这一部分,需要根据功能设计模块的结构和分析端口信号。

点亮LED灯,需要两个端口,一个端口负责接在按键上,接收输入信号,一个负责接在LED上,输出信号到LED等上。

点亮LED灯,需要两个端口,一个端口负责接在按键上,接收输入信号,一个负责接在LED上,输出信号到LED等上。

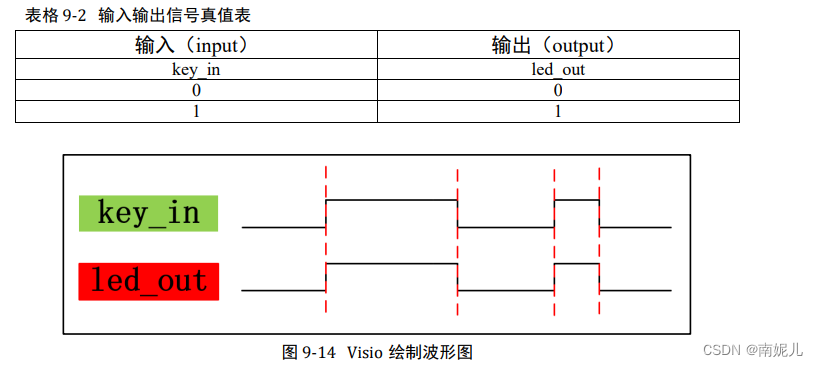

波形设计

框图结构和端口信号设计完毕后就需要设计框图结构下模块功能的实现,也就是输入 和输出之间怎么样的影响关系。输入和输出满足信号与系统的关系,这种关系是一种时序 的、逻辑的关系,即既有时间上的关系又有逻辑上的关系。

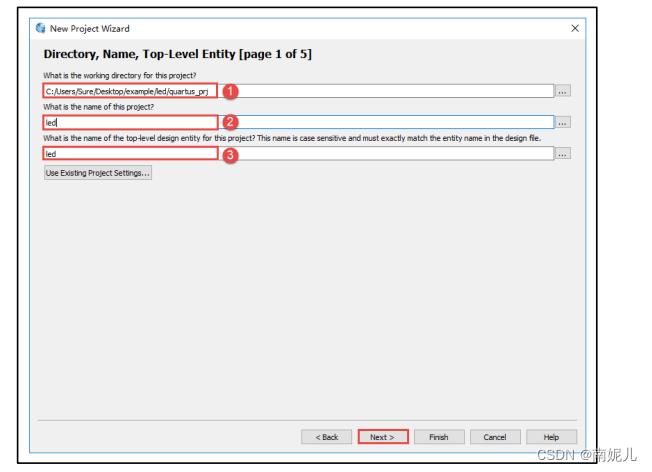

新建工程

1 是这个新建的工程的位置 2 是这个工 程的名字 3 是整个工程设计顶层的文件名,这个名字保持和 2 中的命名一 致即可。

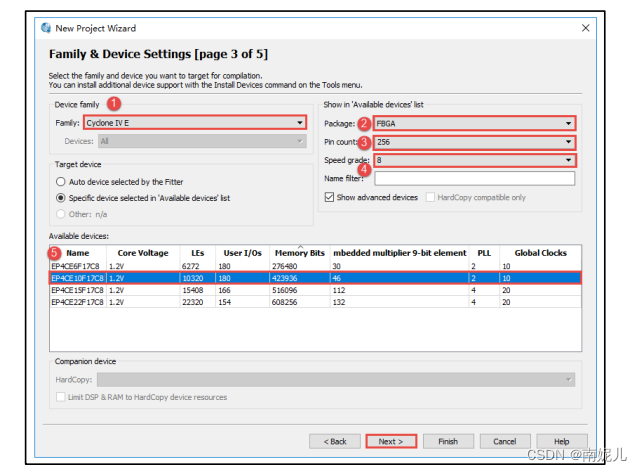

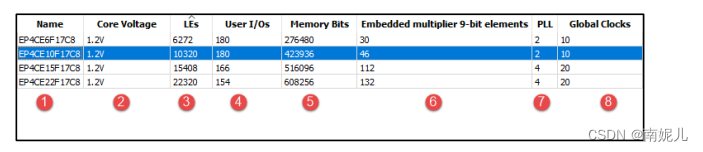

1 框是选择使用哪个系列的芯片

2 框是选择该芯片的封装类型

3 框是管脚数量,选择 256;

4 框是速度等级,选择 8

REL代码的编写

REL代码的编写

RTL 代码编写出的模块叫 RTL 模块(可综合模块)。RTL 代码能够综合出真实的电路。

module led

(

input wire key_in, //输入按键

output wire led_out //输出控制led灯

);

assign led_out=key_in;

endmodule

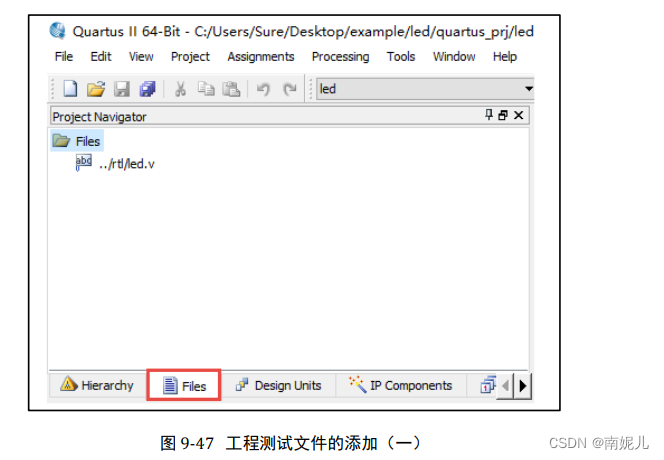

切换到Files ,将文件添加到工程中。

代码的分析和综合

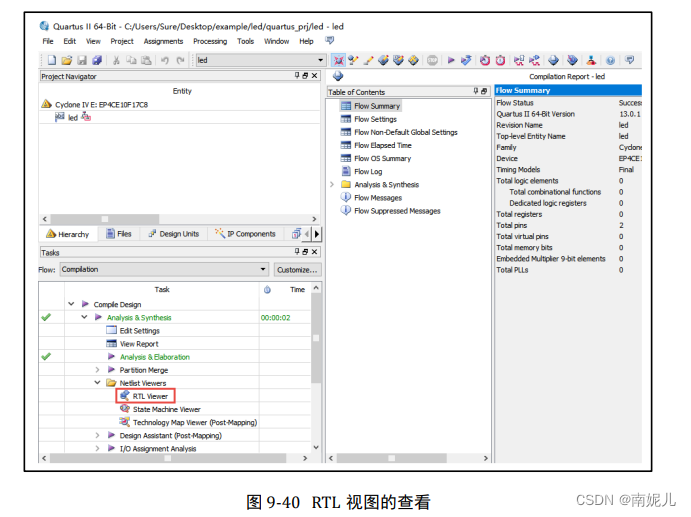

点击如图 9-38 所示的图标进行代码的分析和综合,该步骤的目的是首先检查语法是否 有错,其次是综合器将代码解释为电路的形式。

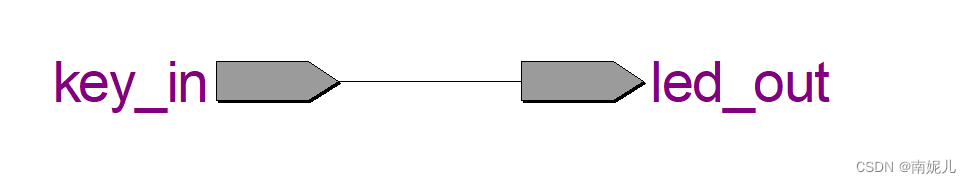

RTL 视图的查看

打开后的界面如图所示,这就是我们设计的硬件电路结构,可见输入是 key_in,然后 通过一根线连接到输出 led_out

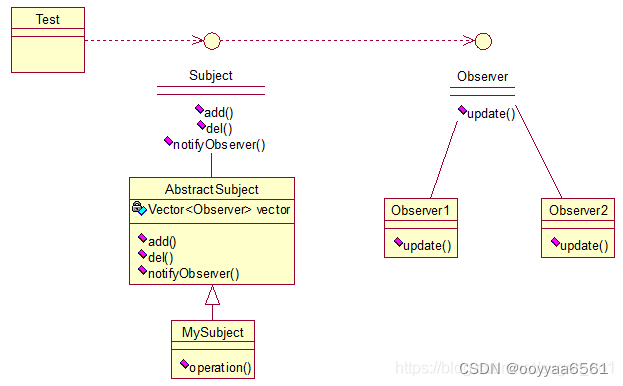

Testbench 的原理

Testbench 是测试脚本.

测试设计电路的整体功能、部分性能是否与预期的目标相符.

编写 Testbench 进行测试的过程如下:

1. 产生模拟激励(输入波形);

2. 将产生的激励加入到被测试模块并观察其输出响应;

3. 将输出响应与期望进行比较,从而判断设计的正确性。

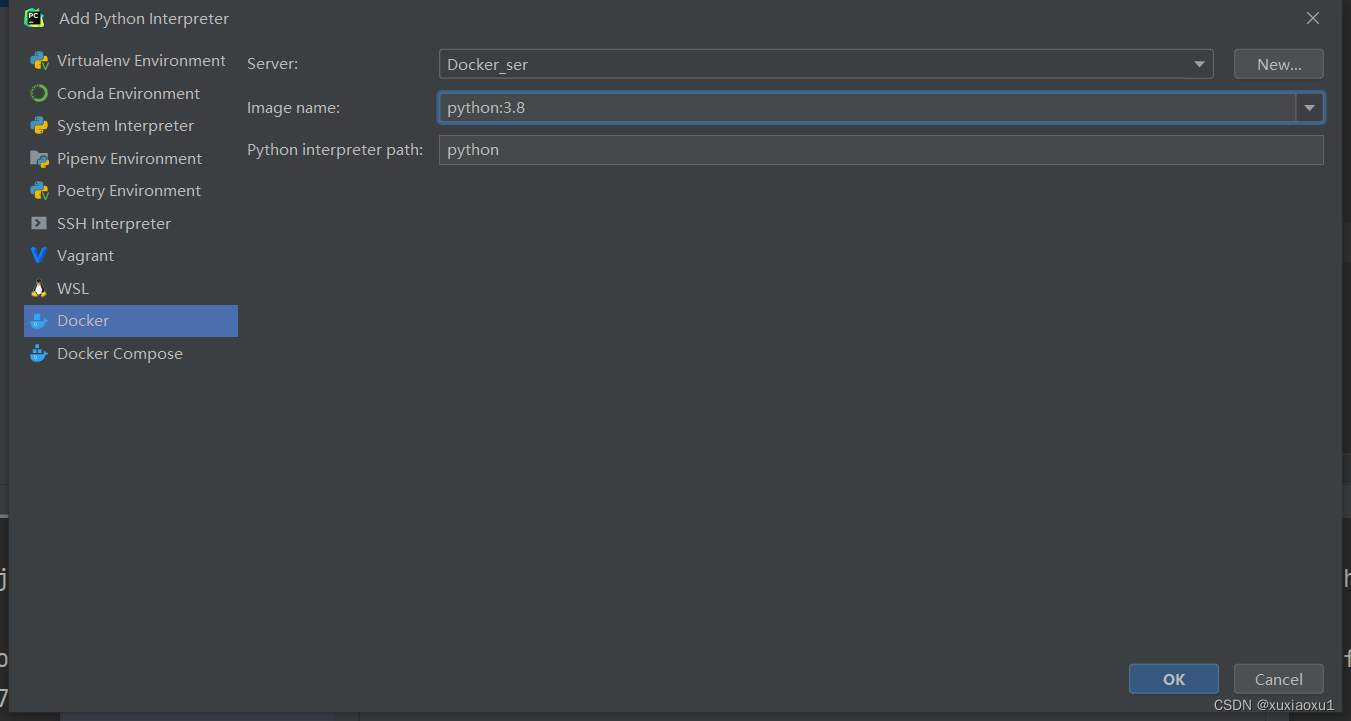

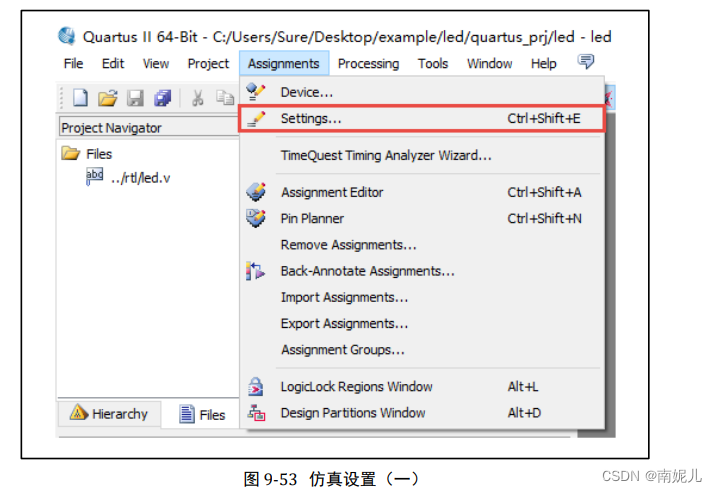

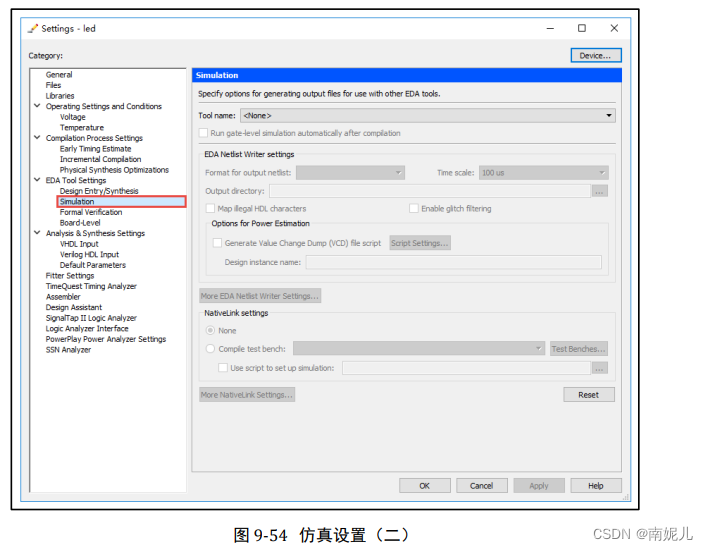

仿真设置

1 框中“Tool name:”栏选择“ModelSim”,“ModelSim”就是独立 的 ModelSim,而“ModelSim-Altera”是安装 QuartusII 时自带的 ModelSim;

2 框中“Format for output netlist:”栏是选择输出网表的语言格式,该网表主要用于后仿真,因为 我们在逻辑设计中往往不做后仿真,所以这里默认即可;

3 框中“Time scale:”栏是选择 输出网表的时间单位,所以也默认即可;

4 框中的“Output direction:”选择输出网表 的位置,这里我们默认即可。

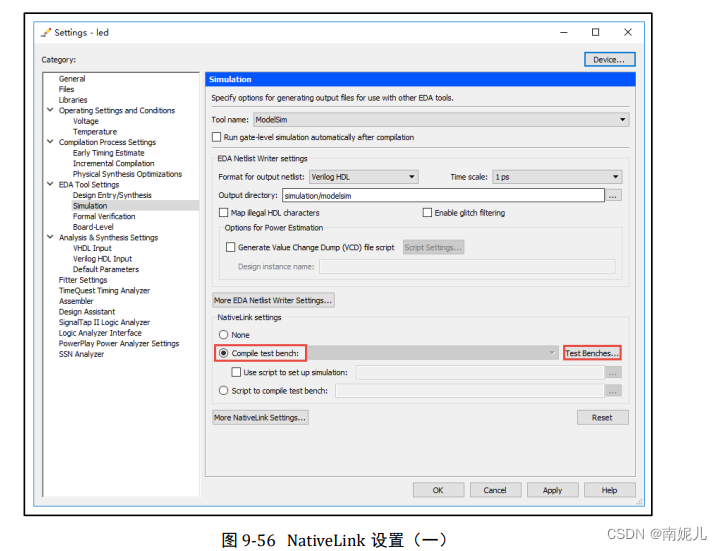

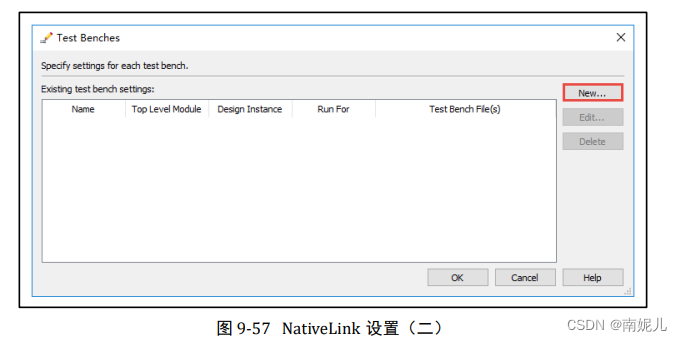

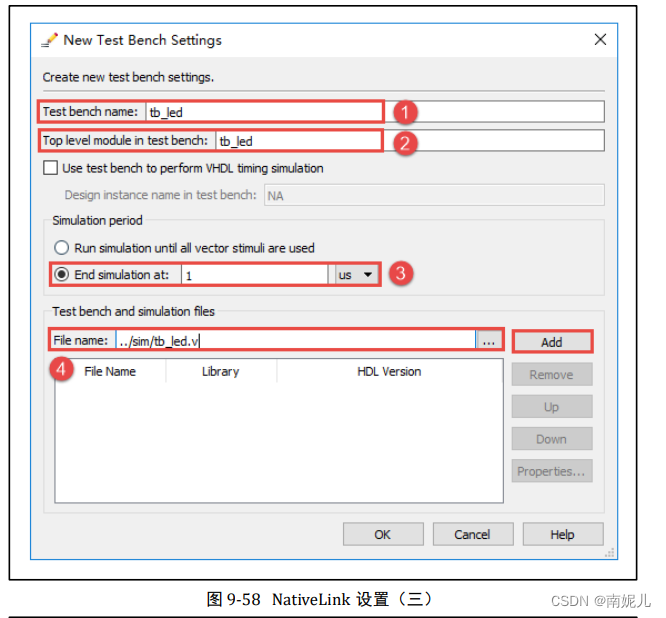

NativeLink 的设置

基于 NativeLink 的设计就是在 QuartusII 中设置好一些参数后直接打开 ModelSim 软件 可以立刻看到仿真的结果

1 框“Test bench name:”就是前面“Comple test bench:”框中的名 字,也就是上图中新建的这个 Test Benches 的名字(一般情况下框1 和框2 的名字保持一 致即可);

2 框“Top level module in test bench:”是 Testbench 顶层的名字,这里只有一个 层次那就是图 9-59 所示中的名字 tb_led;

3 是“End simulstion at:”是设置打开 ModelSim 时波形运行多久后停止,如果这里不设置就需要在仿真代码中仿真完毕的地方添加 “$stop”代码暂停仿真,或者在弹出的 ModelSim 界面中按暂停按钮,否则 ModelSim 会一 直运行。我们设置的是 1us,这个时间不长不短刚刚好,即打开 ModelSim 后运行 1us 后波形停止运行,如果所需要观察的波形 1us 时刻之后,可以在 ModelSim 中再设置运行时间后 继续运行;

4 框“File name:”选择 sim 文件夹下的 tb_led.v 文件。都设置好后点击 “Add”将 tb_led.v 文件添加进来。

`timescale 1ns/1ns

module tb_led();

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//wire define

wire led_out ;

//reg define

reg key_in ;

//初始化输入信号

initial key_in <= 1'b0;

//key_in:产生输入随机数,模拟按键的输入情况

always #10 key_in <= {$random} % 2; /*取模求余数,产生非负随机数0、1

每隔10ns产生一次随机数*/

//********************************************************************//

//**************************** Instantiate ***************************//

//********************************************************************//

//------------- led_inst -------------

led led_inst

(

.key_in (key_in ), //input key_in

.led_out(led_out) //output led_out

);

endmodule

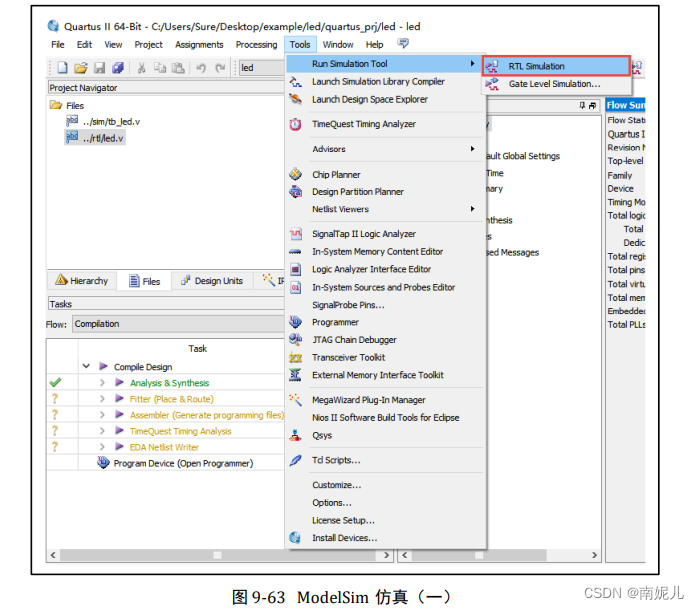

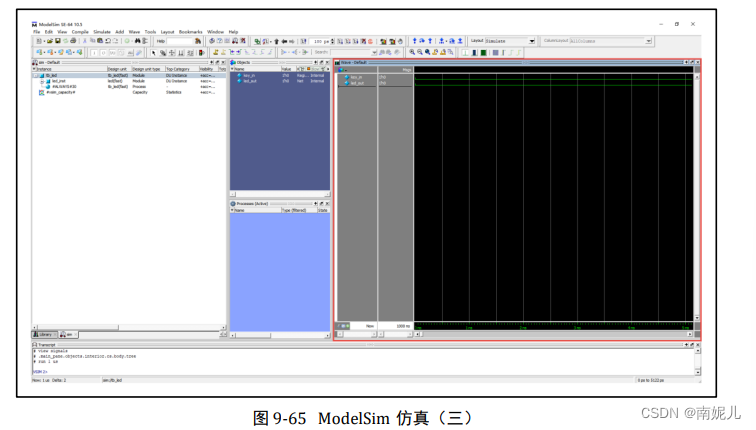

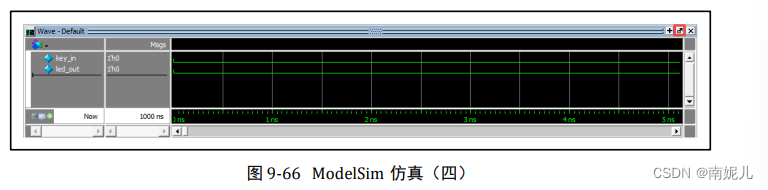

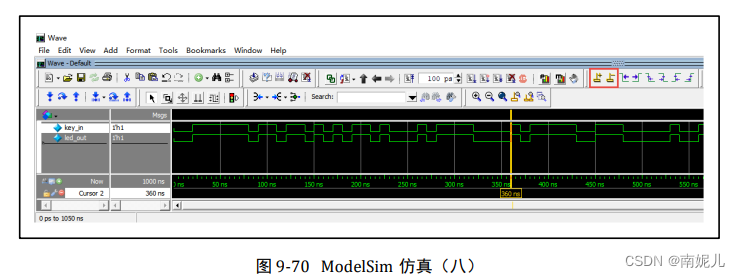

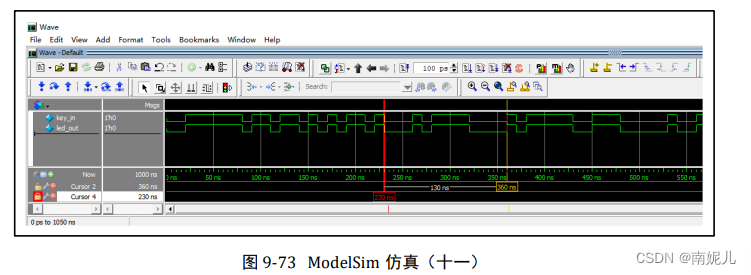

打开 ModelSim 观察波形

放大镜图标

点击框中第一个按钮即添加参考线

点击第二个按钮即去掉参考线

左下角处的“小锁”即可固定参考线,被固定的参考线显示红色

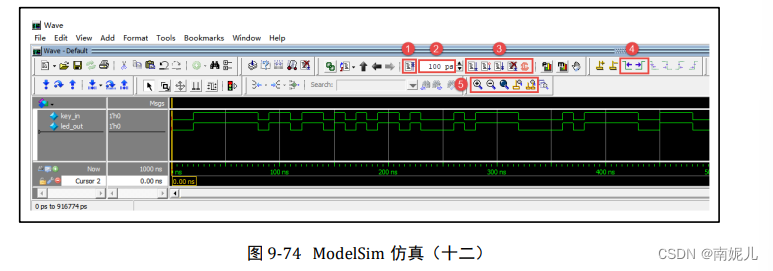

其中○1 框中的图标是波形复位

○2 框是设置运行一次仿真的时间,根据实际观察波形的需要填写相应的时间。但仿真 的时间越久所需要等待的时间也会越久,所生成的仿真文件也会越大;

○3 框中的第一个图标是运行左边设置的时间值,图中显示的是 100ps,那么点击一次 就运行 100ps,运行完 100ps 后就会自动停止,也可以手动输入其他的时间单位和时间值

3 框中的第二个和第三个图标点击一次后波形会一直运行下去,直到点击第四个和第五个 按钮时才会停止;

○4 框中的图标分别是波形的下降沿定位和上升沿定位,当选中要观察的信号时,再点 击这两个按钮时参考线就可以立刻定位到该信号的下降沿或上升沿,再次点击即跳到下一 个下降沿或上升沿;

○5 框中的第一个和第二个图标分别是波形方大和缩小(波形的放大缩小也可以按住键 盘上的“Ctrl”键同时滚动鼠标滚轮)。第三个图标是全局波形显示。第四个图标作用是 将参考线位置处的波形进行放大。第五个图标的作用是将参考线处的波形移动到波形显示 窗口的最开头处。

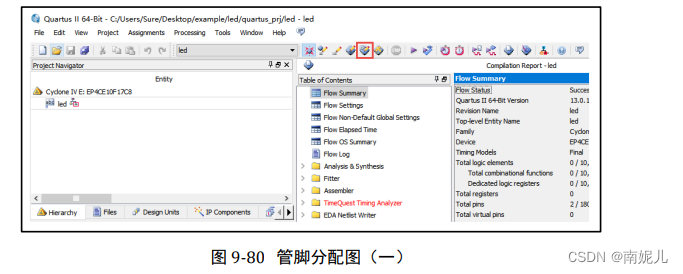

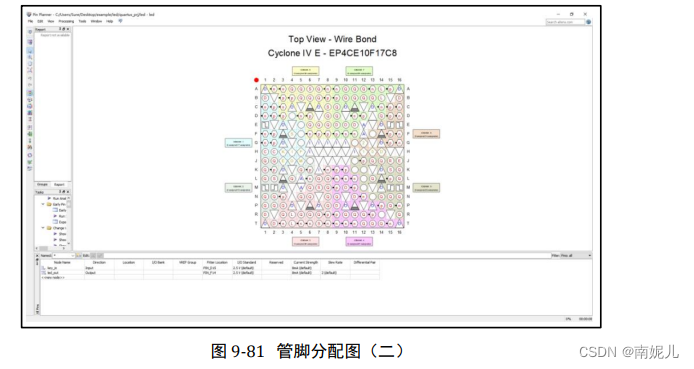

引脚约束

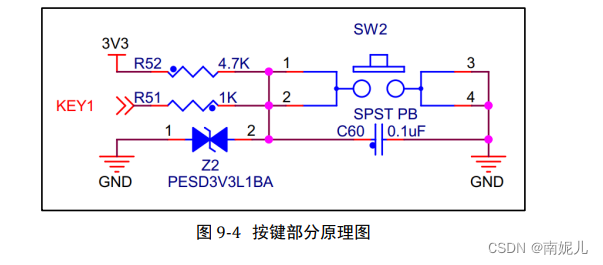

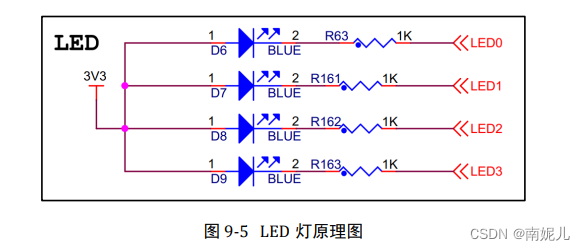

仿真结束后即验证了代码设计的正确性,也就是说可以进行上板验证了,但是在上板 之前还需要进行引脚约束,就是根据硬件原理图确定按键和 led 分别与 FPGA 芯片的哪个 引脚对应。

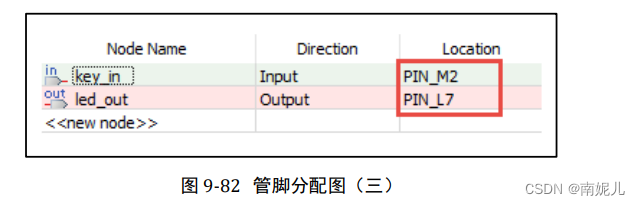

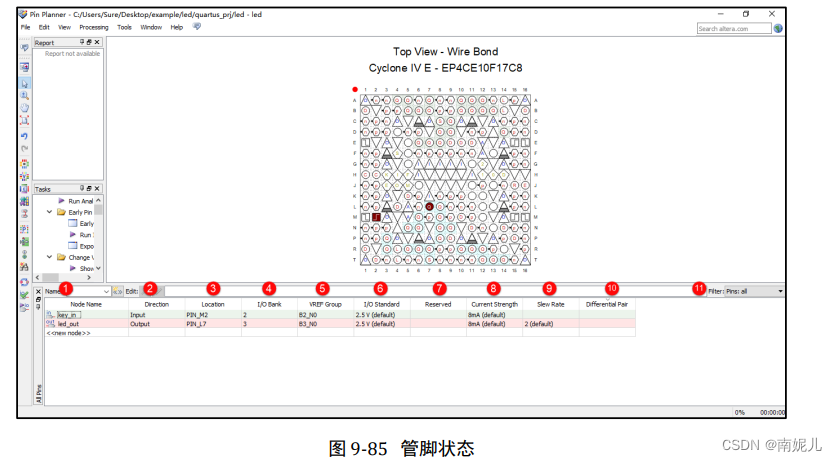

(1) Node Name:RTL 代码中定义的端口名字。

(1) Node Name:RTL 代码中定义的端口名字。

(2) Direction:管脚的输入输出方向。

(3) Location:管脚绑定的位置。

(4) I/O Bank:用于支持对应不同的电平标准,即 VCCIO。每个 Bank 只能有一种电压标 准,一般情况下选择默认值就好。一种颜色下的 I/O 口代表一组 Bank。当管脚的 Location 约束完成以后,I/O Bank 会自动进行填充。

(5) VREF Group:Bank 内部的细分区域,非修改属性,会自动填充。

(6) I/O Standard:对管脚内部的 I/O 进行不同的电平约束。FPGA I/O 的电压由 I/O Bank 上 的 VCC 引入,一个 Bank 上如果引入了 3.3V 的 TTL 电平,那么此时整个 Bank 上输出 3.3V 的 TTL 电平。设置好以后工具可以结合 Current Strength 一起计算功率。如果没 有特殊要求默认即可。 (7) Reserved:这个是对管脚内部的 I/O 逻辑进行约束的,这个约束的是 FPGA 在 I/O 端的 输入输出区域的逻辑。无特殊要求可以为空。

(8) Current Strength:是驱动电流强度,一般选择默认值。如果需要驱动大功率的电路, 可以在 FPGA 外围加驱动电路。

(9) Slew Rate:是电压转换速率,表示单位时间内电压升高的幅值,跟信号跳变时间有 关,一般选择默认值。

(10) Differential Pair:差分管脚。

(11) Filter:通过过滤选项显示指定种类的管脚。

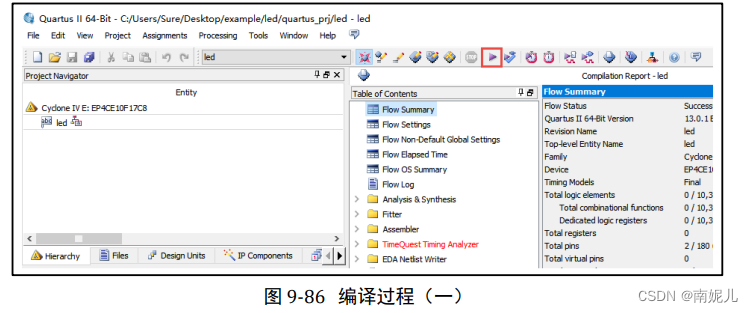

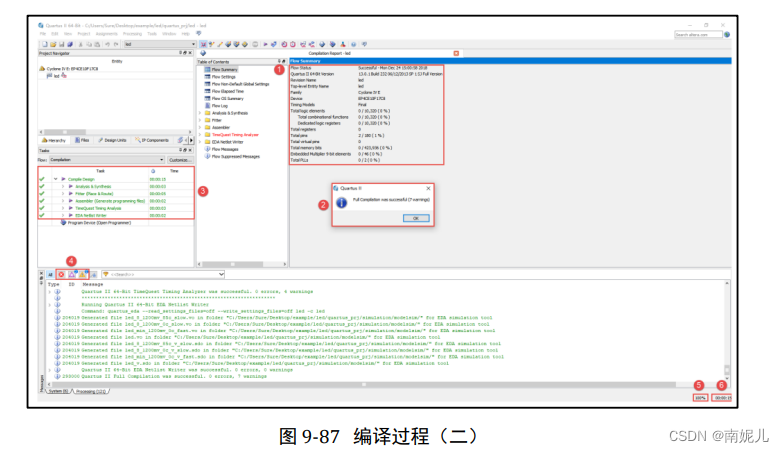

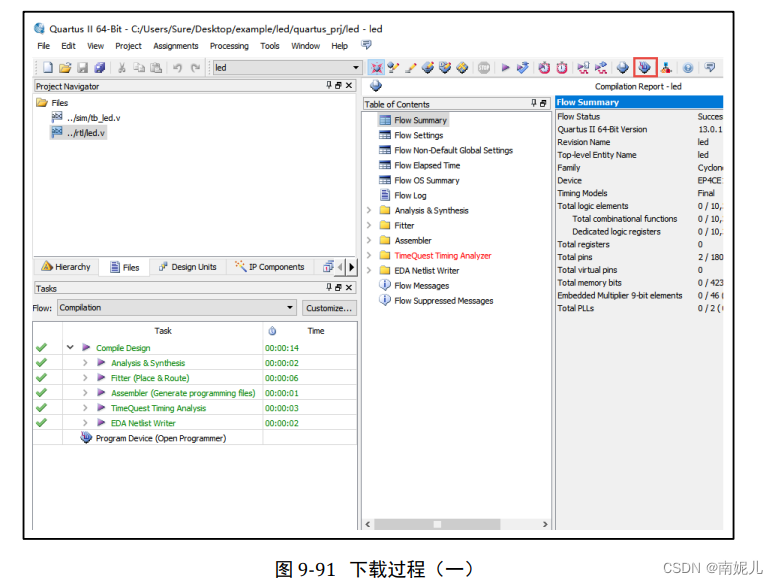

全编译

全编译和分析综合的不同是全编译需要进行布局布线,管脚绑定后就可以对全局进行 布局布线了。

1 框是综合后的资源使用率报告;

2 框是综合后提示的错误警告数,这里没有错误,只有警告和严重警告存在,一共 7 个;

3 框是编译时每一步详细的过程,包括执行每一个部分所使用的具体时间,从上到下 顺序执行,第一个是之前进行过的分析与综合,第二个是布局和布线,第三个是生成程序 文件,第四个是静态时序分析,第五个是写入网表,这 5 个步骤编译后都是自动完成的不 需要进行干涉,如果后期自动完成不能满足需求是需要手动进行设置以实现优化

4 框中从左往右依次是错误、严重警告、警告,只要不出现错误就暂时先不用管,当 警告或者严重警告影响功能时再去分析;

5 框是编译的总进度;

6 框是在编译过程中实时显示的时间,该时间随着工程量对增大而增大,硬件的编译 一次的时间是非常慢的,不像软件那样瞬间就完成了,所以这也是需要进行仿真的原因之 一。

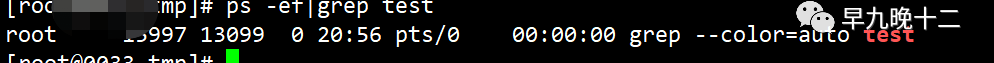

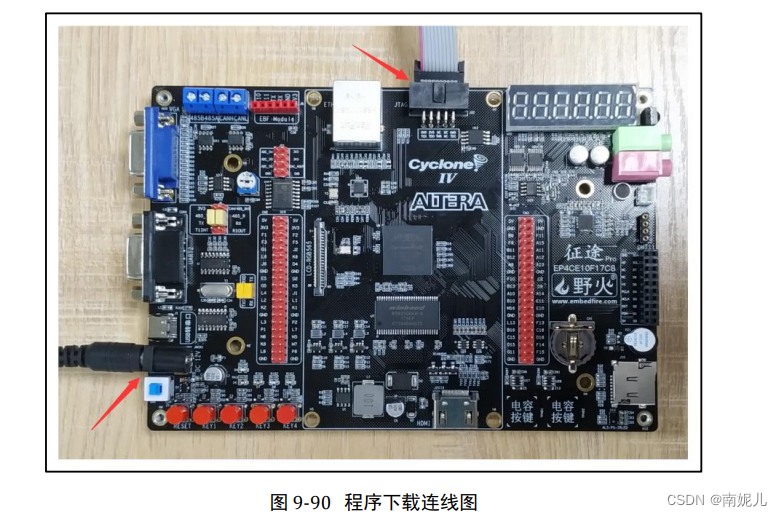

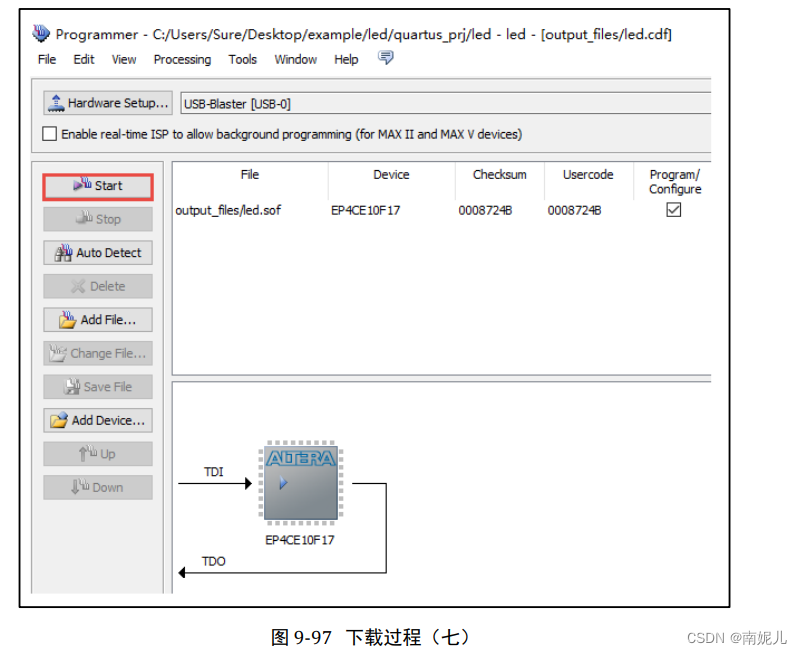

通过 JTAG 将网表下载到开发板

开发板连接 12V 直流电源,USB-Blaster 下载器 JTAG 端连接开发板 JTAG 接口,另一端连接电脑 USB 接口。线路正确连接后,打开开关为板卡上电。

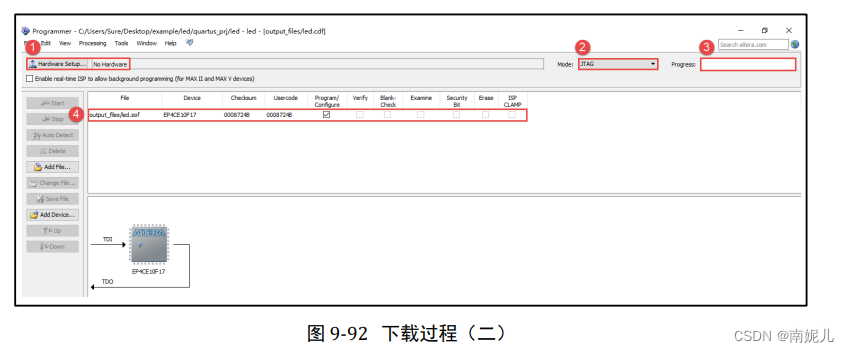

打开下载界面。

1 框是硬件连接设置,当前显示的是“No Hardware” 即 没 有 连 接 到 硬 件 , 我 们 需 要 选 择 连 接 的 硬 件 是 USB-Blaster , 点 击 “ Hardware Setup...”

1 框是硬件连接设置,当前显示的是“No Hardware” 即 没 有 连 接 到 硬 件 , 我 们 需 要 选 择 连 接 的 硬 件 是 USB-Blaster , 点 击 “ Hardware Setup...”

2 框是选择下载的方式,我 们选择“JTAG”下载模式

3 框是下载的进度表,下载成功后会在框内显示绿色并出现 “100%(Successful)”;

4 框是下载的文件,这里是“led.sof”文件。

当设置完成所有的下载设置后

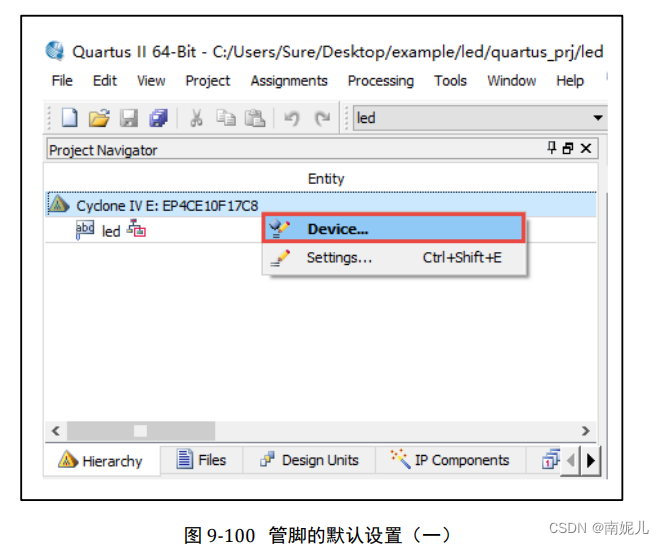

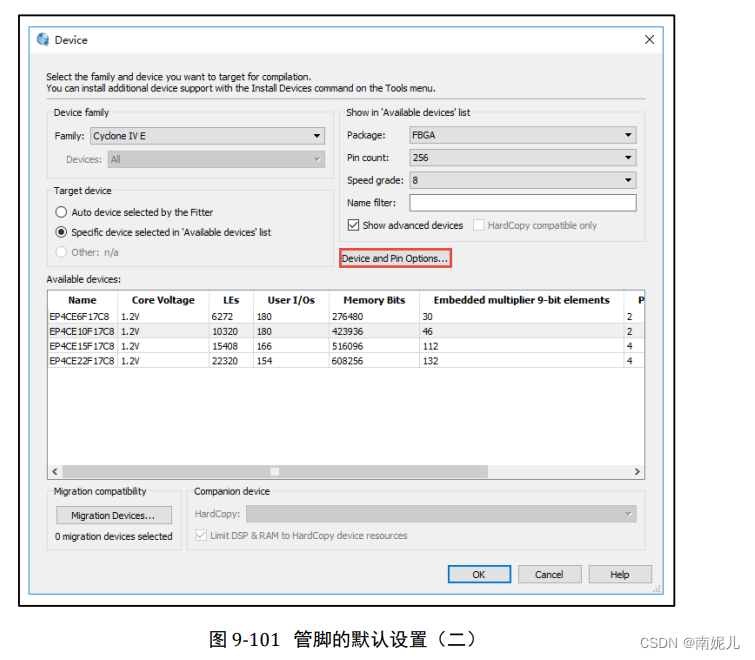

未使用管脚的默认设置

未使用管脚的默认设置

在做一个个例子的时候不可能同时全部用上所有 的 FPGA 管脚,而在 Quartus 软件中默认未使用管脚的状态为弱上拉输入,所以未使用到 的管脚上也是有电压的,只是驱动能力很弱,这往往会导致一些不安全的隐患,所以我们 需要将未使用管脚的状态设置为三态输入

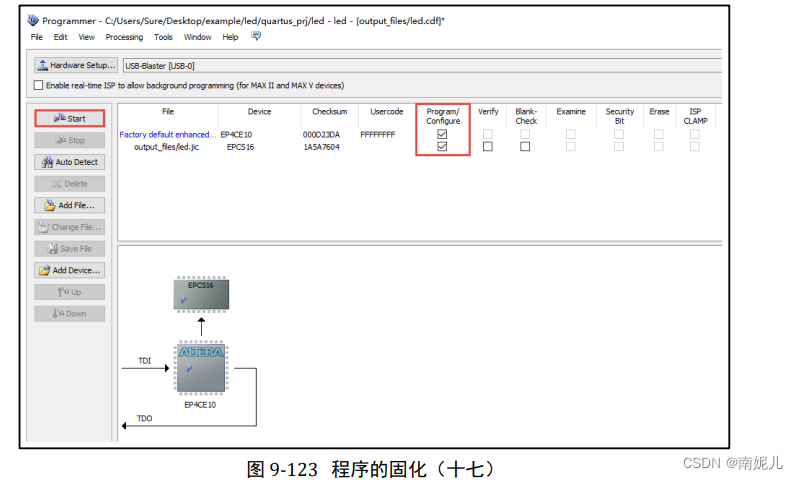

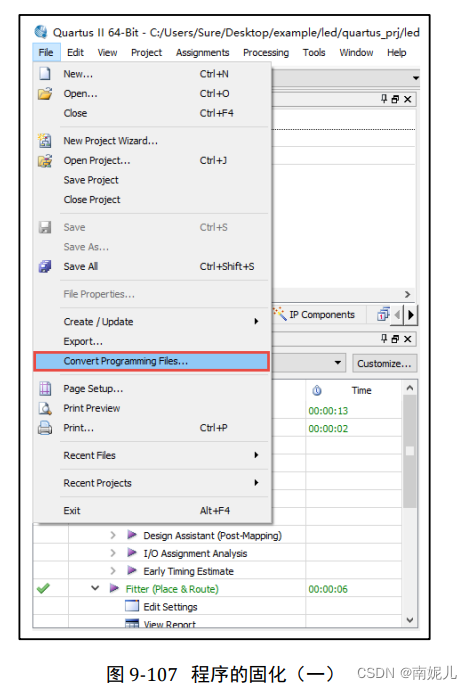

程序的固化

当你把下载网表的上板断电后再重新上电发现 之前的功能已经不存在了,也就是说下载后的网表消失了.我们使用的这款 FPGA 芯片是基于 SRAM 的结构,即下载后的网表存储在 FPGA 内部的 SRAM 中,我们也知道 SRAM 有掉电易失的特性,这也就是我们为什么掉电 后功能就消失的原因

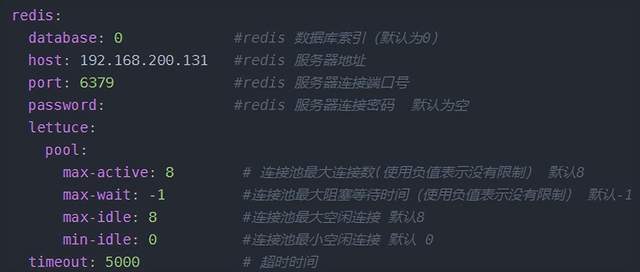

所以我们要想使网表重新上电后仍然存在就需要将网表存储到片外 的 flash 中,flash 芯片型号为 WinBond 25Q16,存储容量为 16Mbit(2M 字节),采用 SPI 协议和 FPGA 进行通信,可做为 FPGA 的配置芯片

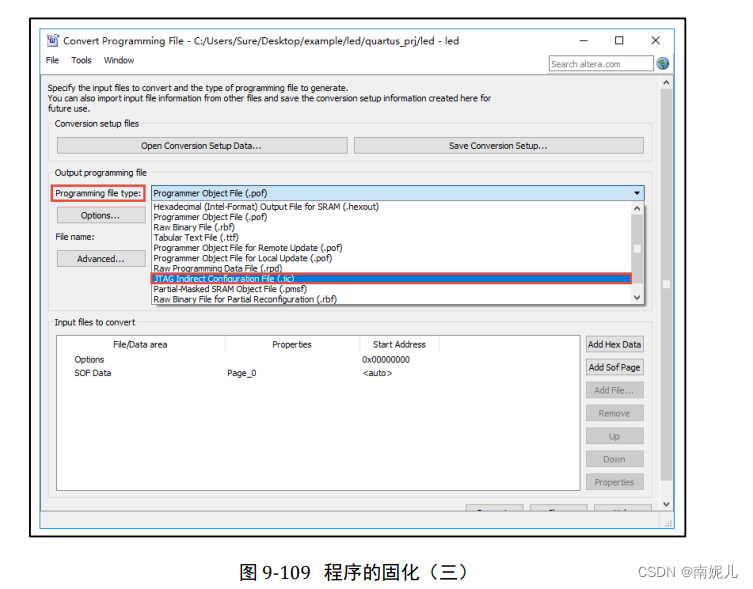

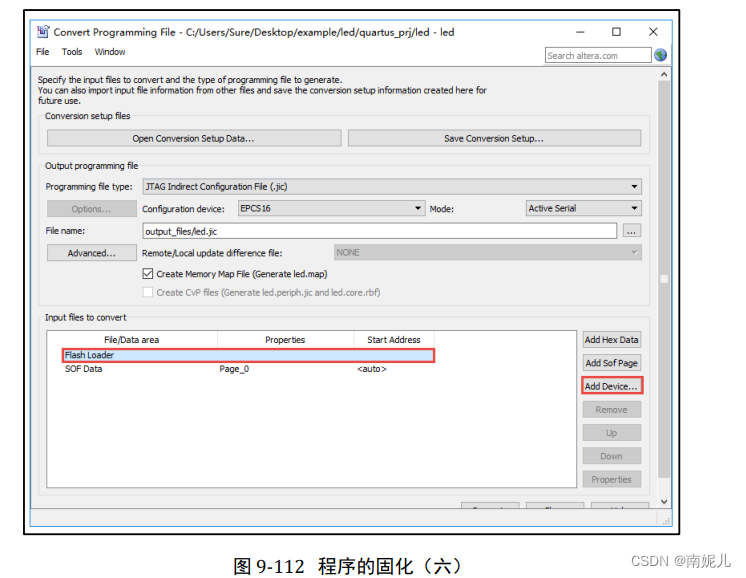

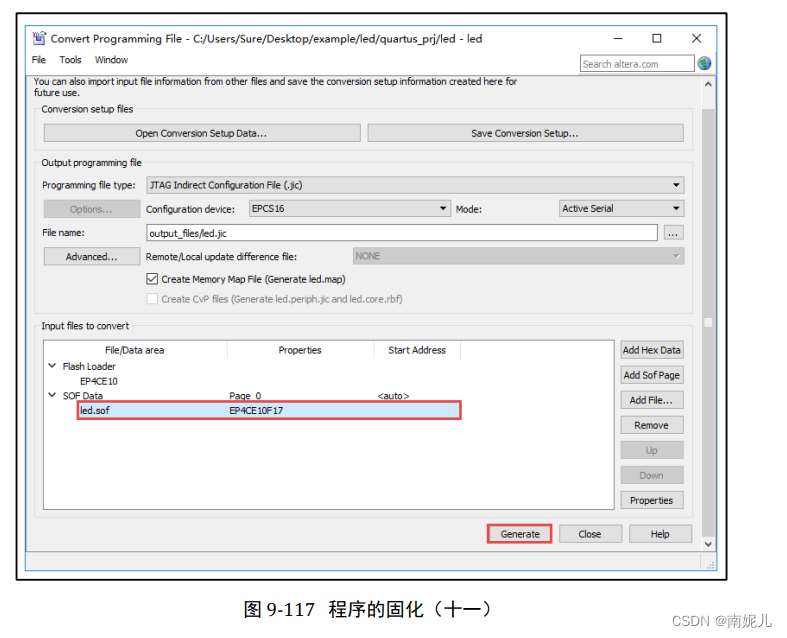

“Programming file type:”栏是选择输出文件的类型,我们选择“JTAG Indirect ConfIguration File(.jic)”

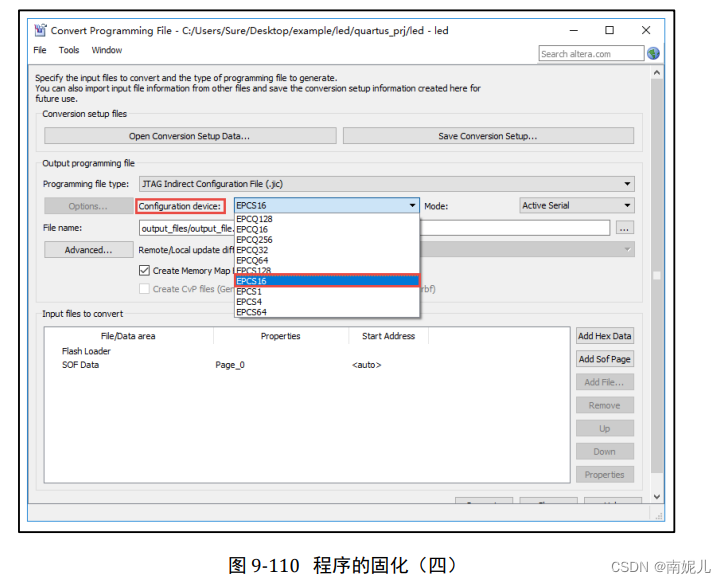

“Configuration device:”栏是 flash 的型号,我们选择“EPCS16”

“Configuration device:”栏是 flash 的型号,我们选择“EPCS16”

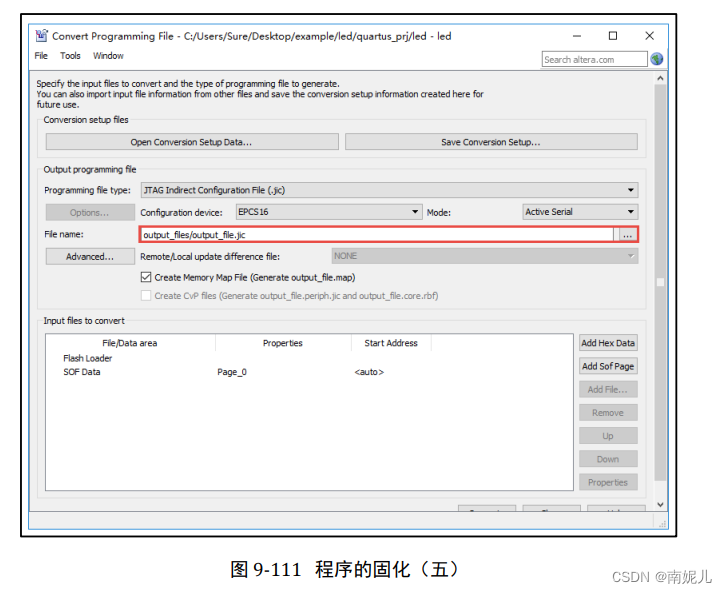

“File name:”栏是选择输出.jic 文件的位置

如图 9-112 所示,点击“Input files to convert”框中的“Flash Loader”后会发现“Add Device...”从不能被选择的情况下可以被选择,然后点击“Add Device...”

如图 9-112 所示,点击“Input files to convert”框中的“Flash Loader”后会发现“Add Device...”从不能被选择的情况下可以被选择,然后点击“Add Device...”

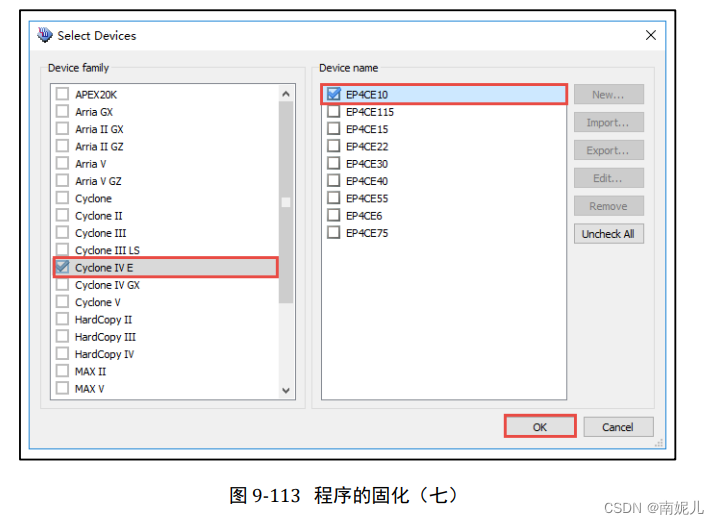

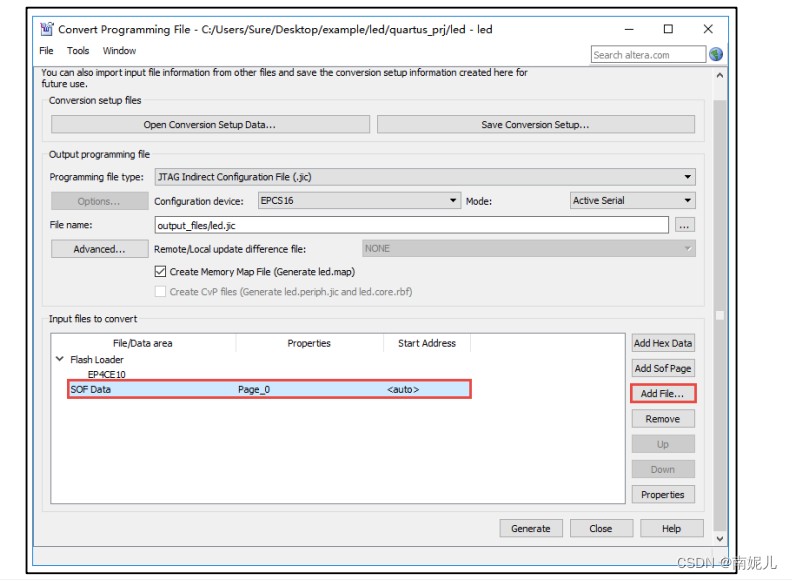

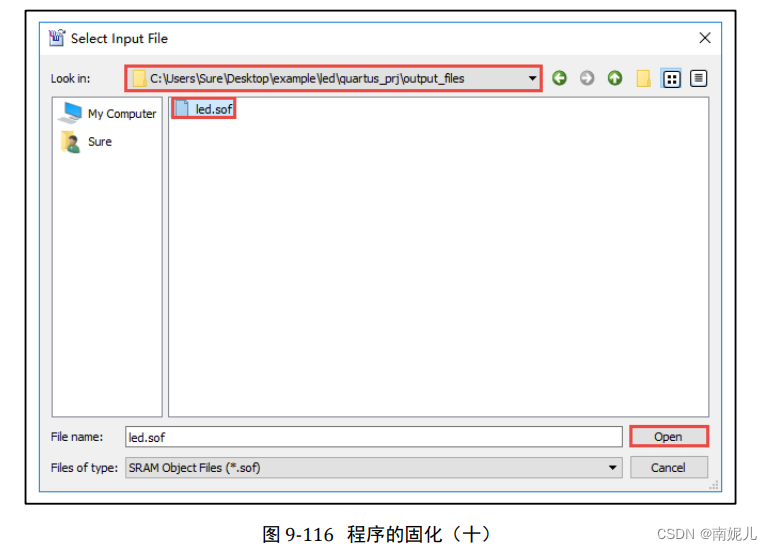

如图 9-113 所示,选择我们使用的 FPGA 芯片所属的型号,在“Device family”框中将 “Cyclone IV E”前的括号勾选上,在“Device name”框中将“EP4CE10”前的括号勾选 上,然后点击“OK”。添加后如图 9-114 所示。

如图 9-113 所示,选择我们使用的 FPGA 芯片所属的型号,在“Device family”框中将 “Cyclone IV E”前的括号勾选上,在“Device name”框中将“EP4CE10”前的括号勾选 上,然后点击“OK”。添加后如图 9-114 所示。

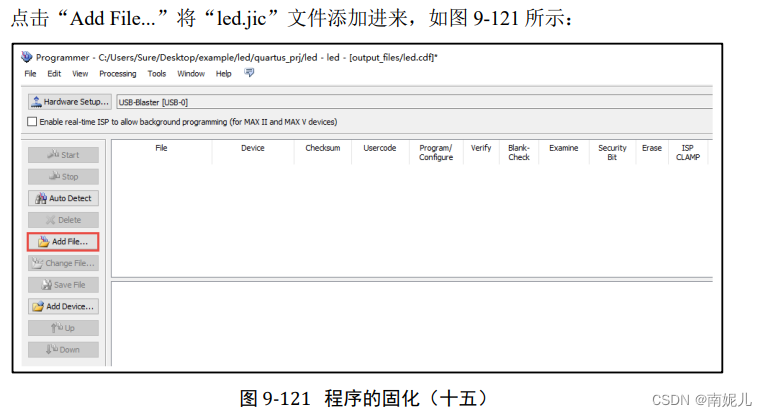

先将“Program/Configure”下的方框打上钩,然后点击“Start”执行 程序的固化。

先将“Program/Configure”下的方框打上钩,然后点击“Start”执行 程序的固化。