一.CPU的组成结构

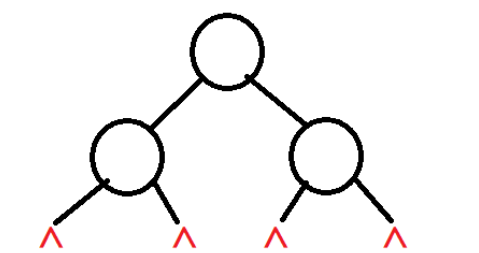

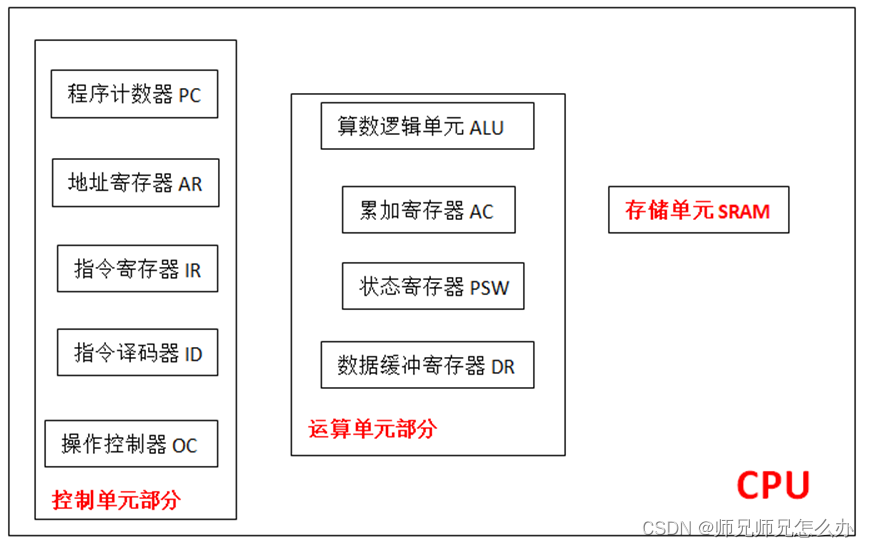

CPU主要有运算器、控制器、寄存器和内部总线等组成,其大概的样子长这样:

看不懂没关系,我们将采用自顶而下的方法来讲解CPU的具体工作原理,我们首先来说一下什么叫寄存器,顾名思义,寄存器就是用于暂存东西的,类似去超市的时候门口放着的那些暂存箱,你把东西临时放进去,等逛完超市之后就把它拿回来,就这么个作用,如果有兴趣想要了解一下寄存器为什么可以暂存东西,可以参考以前写过的文章:【计算机组成原理】寄存器的本质——锁存器

二.CPU的思考过程

首先,CPU摸鱼了很久,终于想起来要干点活了,不然该被优化了,那么它第一件事情就是去领取一下任务,但是任务在哪里找呢?这时候,它就打开了程序计数器PC(作用请看第三节3.1.程序计数器PC)。

程序计数器PC里面保存了下一条待运行指令(也可以称为任务,但是一般都叫指令)的地址,这个程序计数器PC就像个悬赏榜一样,告诉CPU任务发起人在哪里,让CPU去指定的地址找任务发起人,执行相应的指令。

当CPU在程序计数器PC找到地址后,会将当前所访问的内存单元的地址保存到地址寄存器AR(作用请看第三节3.2.地址寄存器AR)中去,然后让程序计数器PC指向下一条待运行的指令:

紧接着,CPU就拿着地址顺着地址总线找到了任务发起人,并且拿到了指令,把指令从数据总线里取出来放到了指令寄存器IR(作用请看第三节3.3.指令寄存器IR)中:

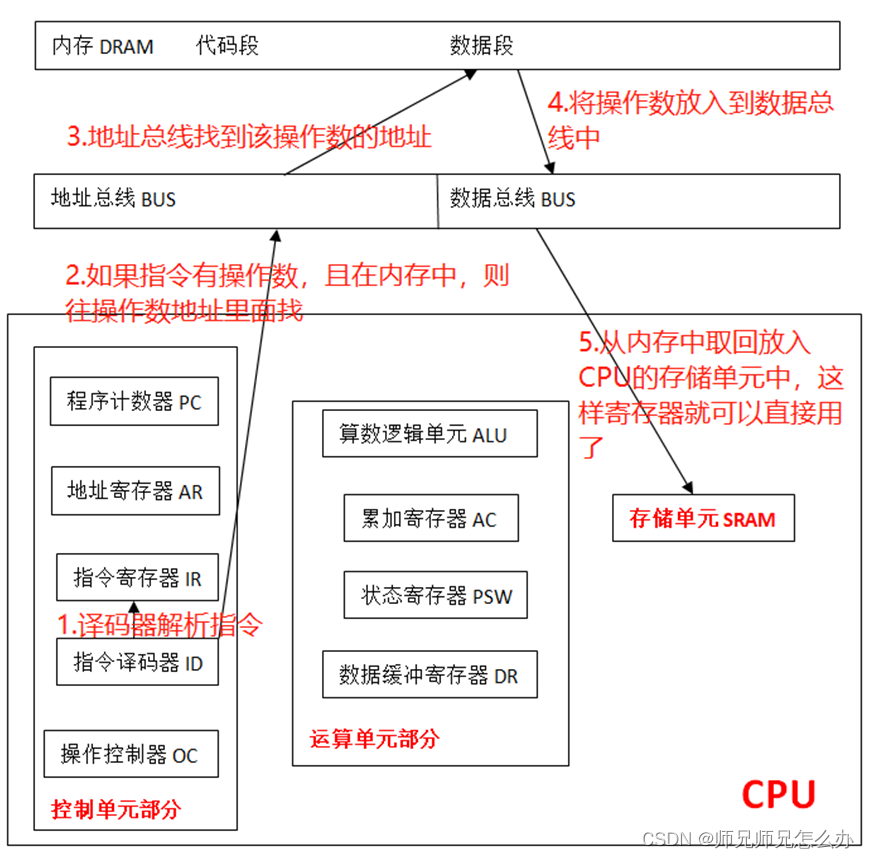

指令寄存器IR拿到指令后,指令译码器ID(作用请看第三节3.4.指令译码器ID)找上门来,根据指令格式(作用请看第三节3.5.指令格式)检查指令寄存器中的指令,分析出来操作码是什么,操作数在哪里之类的,如果操作数在内存中,就需要将相应的操作数从内存中取回至存储单元SRAM处,如果在寄存器中就直接就直接取用了。

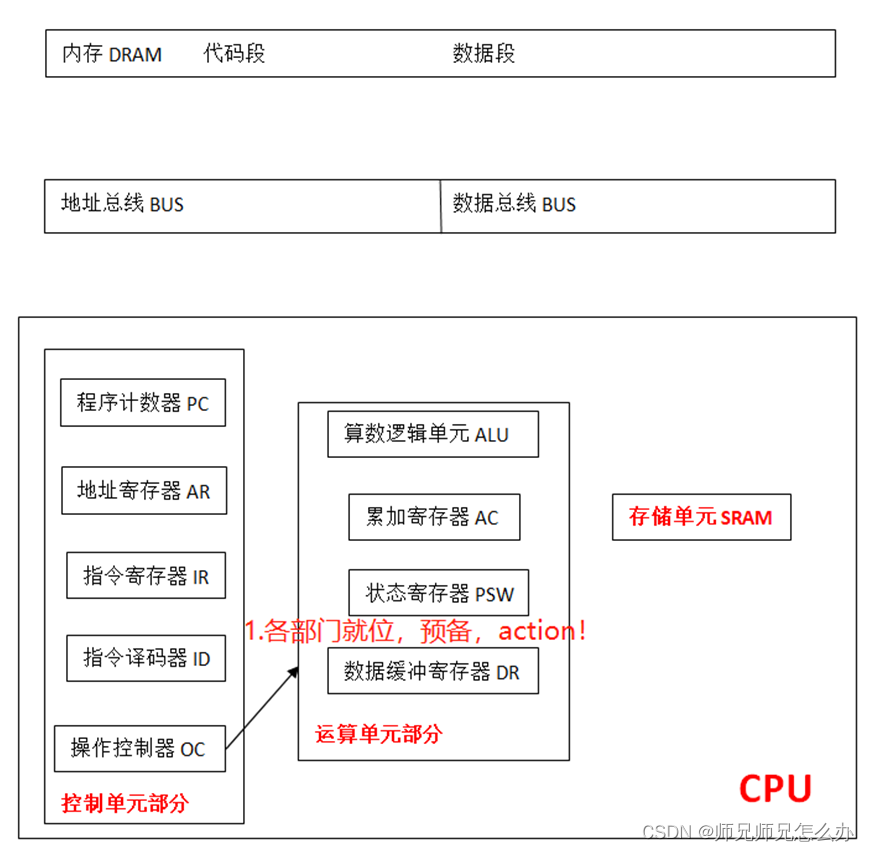

操作控制器OC拿着清单检查发现操作数准备好了,操作码也有了,然后就给CPU的运算部门下达指令,开始运算,这时真正指令执行的时刻才到来。

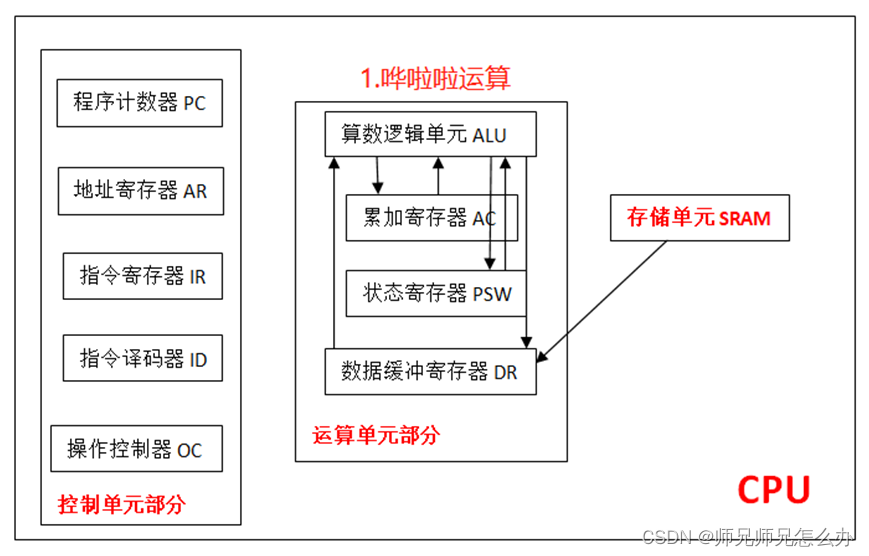

运算器开始工作,算数逻辑单元ALU(作用请看第三节3.6.算数逻辑单元ALU)开始进行运算,期间如果数据过多处理不过来,就将数据暂时存放在累加寄存器AC(作用请看第三节3.7.累加寄存器AC)中,如果有操作数在存储单元里即将需要使用了,就把数据暂存在数据缓冲寄存器DR(作用请看第三节3.8.数据缓冲寄存器DR)中,将计算的状态存放在状态寄存器PSW(作用请看第三节3.9.状态寄存器PSW)中。

运算结束后,CPU继续回到程序计数器PC里面去,看看悬赏榜上的其他任务,周而复始,开始循环。

三.各寄存器的功能作用

3.1.程序计数器PC

程序计数器PC:又称为指令计数器,程序在第一次执行之前会将起始地址存入计数器中,往后每执行一条指令,CPU就自动修改PC的内容,以便随时保持着PC里面存放的地址总是下一条将要执行的指令的地址。程序执行分为顺序执行和转移执行两种。顺序执行时,CPU修改PC的过程就是简单地加1,转移执行时,后续指令的地址会根据当前指令的地址加上转移的偏移量得到,或者根据转移指令给出的直接转移地址得出。在8086CPU中,程序计数器PC就是CS:IP寄存器。CS:IP是怎么用地址加法器找到对应地址以及自加1的,可以以前发过的文章:【汇编语言】CS:IP寄存器

3.2.地址寄存器AR

地址寄存器AR:地址寄存器保存当前CPU所访问的内存单元的地址。存在的意义是由于内存和CPU存在着速度上的差异,需要用到地址寄存器充当缓存的作用,知道内存的读/写操作完成为止。

3.3.指令寄存器IR

指令寄存器IR:当CPU执行一条指令时,会将指令从内存中取出来放到缓冲寄存器,然后再送入指令寄存器IR中暂存。指令译码器会根据指令寄存器IR的内容产生各种位操作指令,控制其他的组成部件工作,完成所需的功能。

3.4.指令译码器ID

指令译码器ID:对指令中的操作码字段进行分析解释,识别该指令规定的操作,向操作控制器发出具体的控制信号,控制各部件工作,完成所需的功能。

3.5.指令格式

一般的指令格式如下:

| 前缀 | 操作码 | 寻址方式、操作数类型 | 立即数 | 偏移量 |

前缀用于记录指令的一些辅助信息,例如rep、段超越前缀等等,操作码就是mov、jmp这种操作码,寻址方式是指CPU的寻址方式(后续会编写一篇关于CPU寻址方式的文章,如果有更新会及时在这里添加链接),比如基址寻址、变址寻址等,操作数类型记录使用什么寄存器之类的,如果指令使用了立即数,就会将其记录在立即数这部分,如果寻址方式使用了偏移量,就会在偏移量部分记录指令格式中的偏移量部分。

3.6.算数逻辑单元ALU

算数逻辑单元ALU:是运算器中最重要的组成部件,负责处理数据,实现对数据的算是运算和逻辑运算

3.7.累加寄存器AC

累加寄存器AC:当运算器的算数逻辑单元执行算术或者逻辑运算时,为ALU提供一个临时工作区。比如进行减法运算时,会先将被减数去除暂存在AC中,再从内存中取出减数,然后通AC的被减数相减,所得到的结果送至AC中,运算结果是放在累加器中的。

3.8.数据缓冲寄存器DR

数据缓冲寄存器DR:对存储单元进行读/写操作时,使用DR暂存有存储单元读/写的一条指令或者数据字,将不同时间段内读/写的数据分隔开来。也可以作为CPU和内存、外部设备之间的数据传输中转站/缓冲区。

3.9.状态寄存器PSW

状态寄存器PSW:用于保存由算数指令和逻辑指令运行或者测试的结果建立的各种条件码内容,只要分为状态标志和控制标志。如进位标志(C)、溢出标志(V)、为0标志(Z)、为负标志(N)、中断标志(I)、方向标志(D)和单步标志等等。