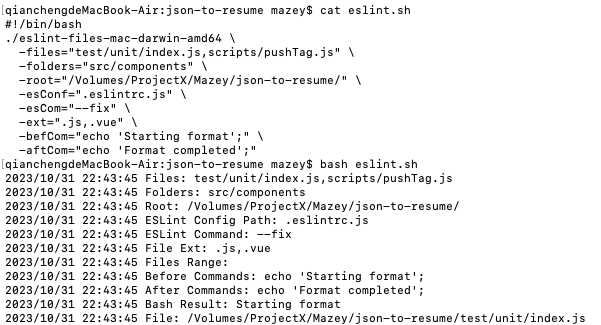

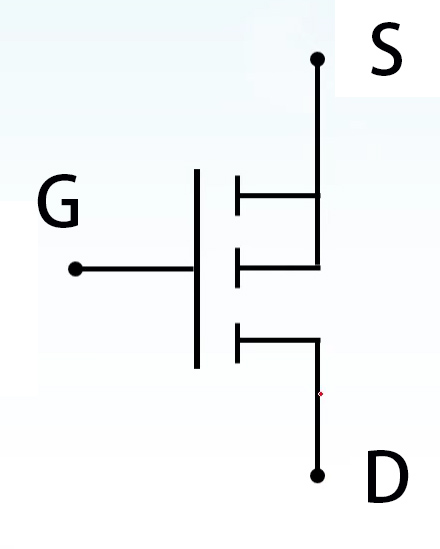

一、电路符号

MOS管分为 G(栅极)、S(源极)、D(漏极) 三极,在图中 S 极有两条线,D 极只有一条线。

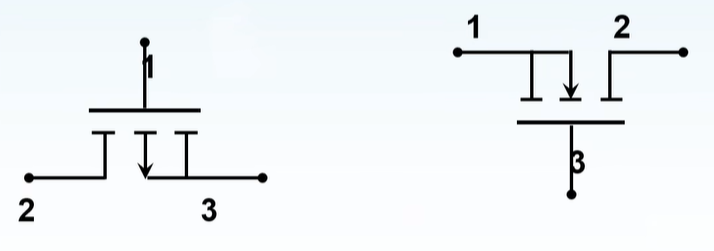

1.1 NMOS 和 PMOS

下图中,左侧是 PMOS,右侧是 NMOS。箭头向外是P,朝内是N。

比较巧妙的记忆办法是放 P 朝外所以是 PMOS。内的拼音是 nei,所以 NMOS 代表内。

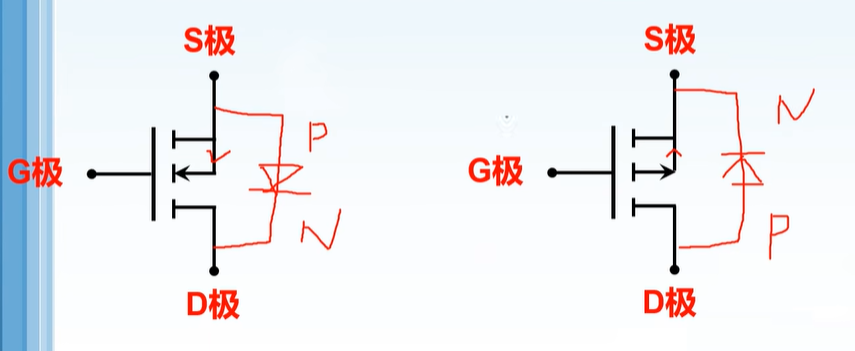

1.2 寄生二极管方向

判断规则是,NMOS中 S 指向 D。PMOS 中 D 指向 S。

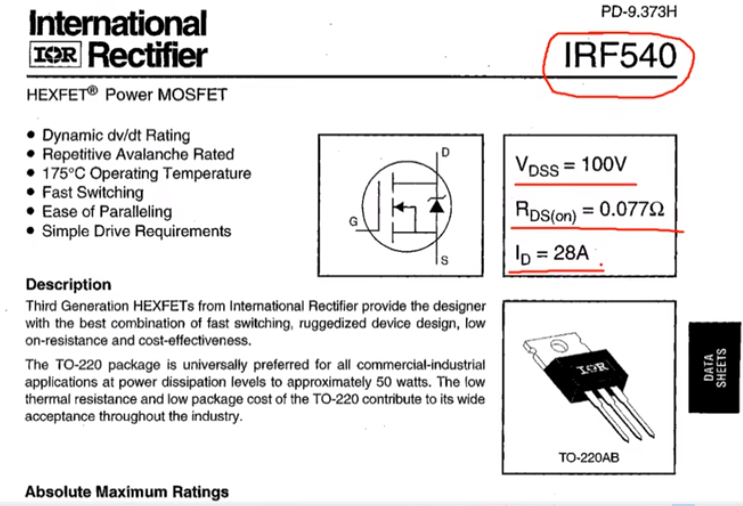

二、NMOS 的参数

2.1 VDSS 最大漏-源电压

在栅源短接,漏-源额定电压(VDSS)是指漏-源未发生雪崩击穿前所能施加的最大电压。根据温度的不同,实际雪崩击穿电压可能低于额定 VDSS。

2.2 VGS 最大栅源电压

VGS额定电压是栅源两极间可以施加的最大电压。设定该额定电压的主要目的是防止电压过高导致的栅氧化层损伤。

2.3 ID 连续漏电流

ID 定义为芯片在最大额定结温 TJ(max)下,管表面温度在 25℃ 或者更高温度下,可允许的最大连续直流电流。

2.4 VGS(th)

是指加的栅源电压能使漏极开始有电流,或关断MOSFET时电流消失时的电压,测试的条件(漏极电流,漏源电压,结温)也是有规格的。正常情况下,所有的 MOS 栅极器件的阈值电压都会有所不同。因此,VGS(th)的变化范围是规定好的。VGS(th)是负温度系数,当温度上升时,MOSFET 将会在比较低的棚源电压下开启。

2.5 RDS(on)导通电阻

RDS(on)是指在特定的漏电流(通常为ID电流的一半)、栅源电压和 25℃ 的情况下测得的漏-源电阻。可以理解为 MOS 管自身的电阻。

2.6 Ciss 输入电容

将漏源短接,用交流信号测得的栅极和源极之间的电容就是输入电容。Ciss是由栅漏电容Cgd和栅源电容Cgs并联而成,或者 Ciss=Cgs +Cgd,当输入电容充电致阈值电压时器件才能开启,放电致一定值时器件才可以关断。因此驱动电路和Ciss对器件的开启和关断延时有着直接的影响。

Qgs、Qgd 和 Qg

棚电荷栅电荷值反应存储在端子间电容上的电荷,既然开关的瞬间,电容上的电荷随电压的变化而变化,所以设计栅驱动电路时经常要考虑栅电荷的影响。

栅极电荷 Qg 是产生开关损耗的主要原因。栅极电荷是 MOS 管门极充放电所需的能量,相同电流、电压规格的 MOSFET,具有比较大的栅极电荷意味着在 MOS 开关过程中会损耗更多的能量。所以,为了尽可能降低 MOS 管的开关损耗,工程师在电源设计过程中需要选择同等规格下 Qg 更低的 MOS 管作为主功率开关管。

三、开关电源效率问题

影响开关电源电源效率的两个损耗因素是:导通损耗和开关损耗。导通损耗具体来讲是由 MOS 管的导通阻抗 Rds 产生的,Rds 与栅极驱动电压 Vgs 和流经 MOS 管的电流有关。如果想要设计出效率更高体积更小的电源,必须充分降低导通阻抗。

开关损耗,栅极电荷 Qg 是产生开关损耗的主要原因。栅极电荷是 MOS 管门极充放电所需的能量,相同电流、电压规格的MOSFET具有比较大的栅极电荷意味着在 MOS 开关过程中会损耗更多的能量。所以,为了尽可能降低MOS管的开关损耗,工程师在电源设计过程中需要选择同等规格下 Qg 更低的 MOS 管作为主功率开关管。

四、使用方式

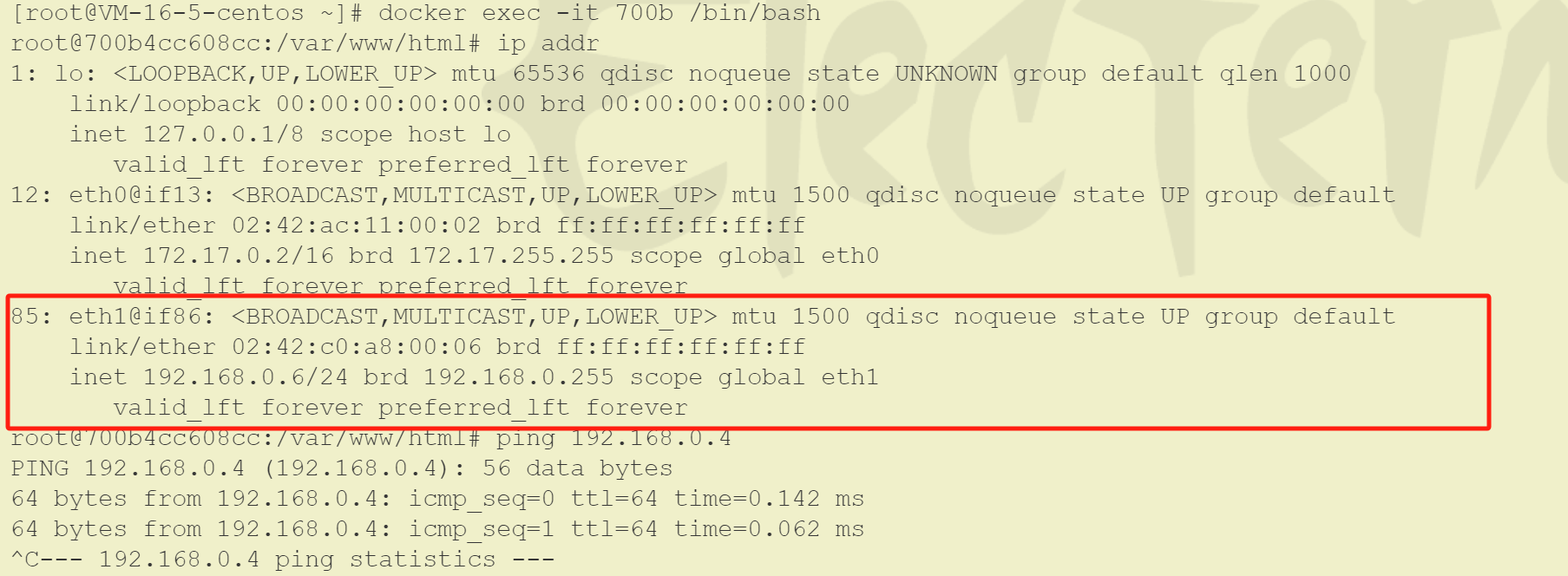

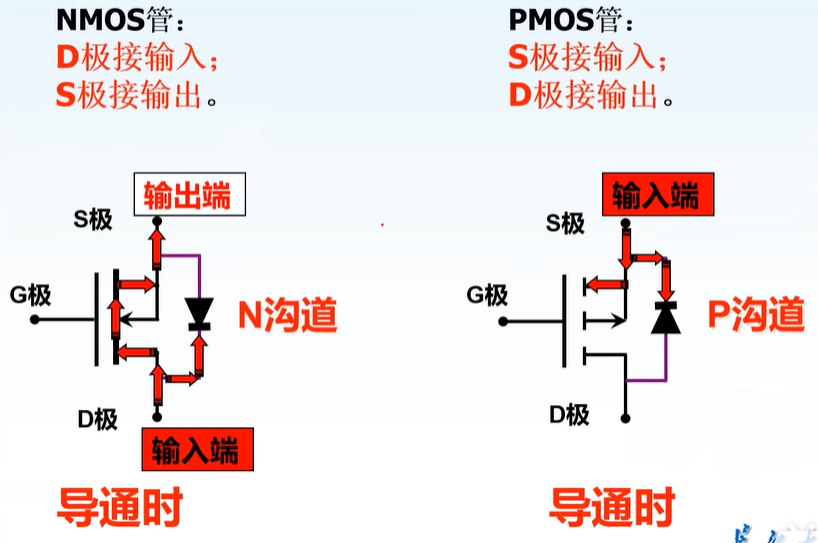

4.1 导通方向

NMOS 下 G 极高电平导通,低电平断开;PMOS 反之,G 极低电平导通,高电平断开。

导通方向与寄生二极管方向相反。

如果我们顺着寄生二极管方向使用 mos 管,将是一直导通的。

如下图 LED 灯会常亮不受控制。

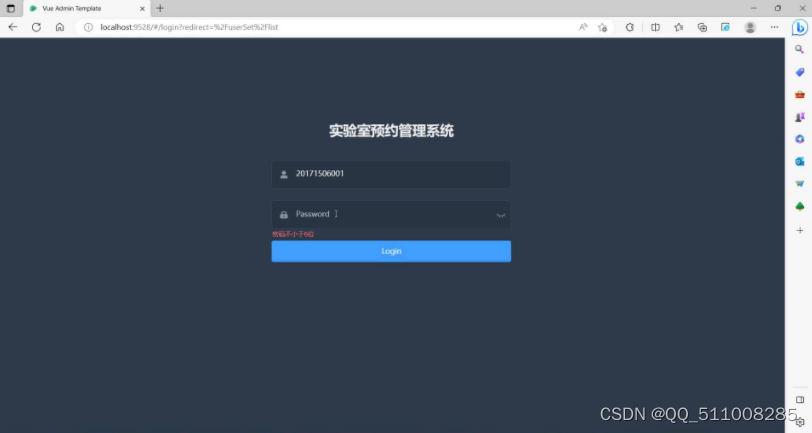

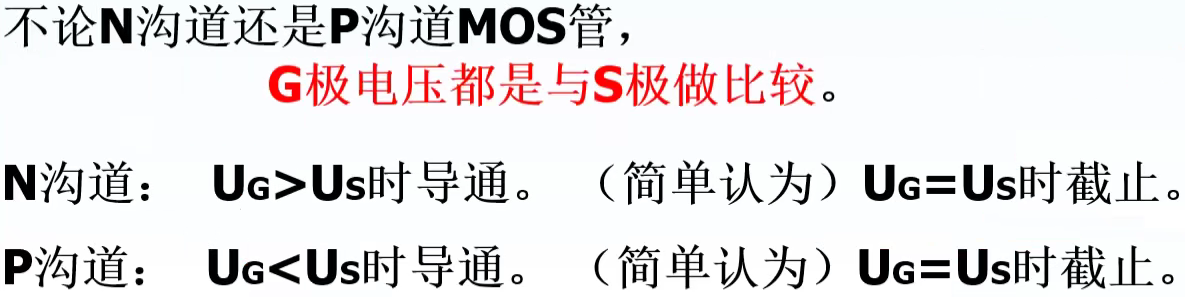

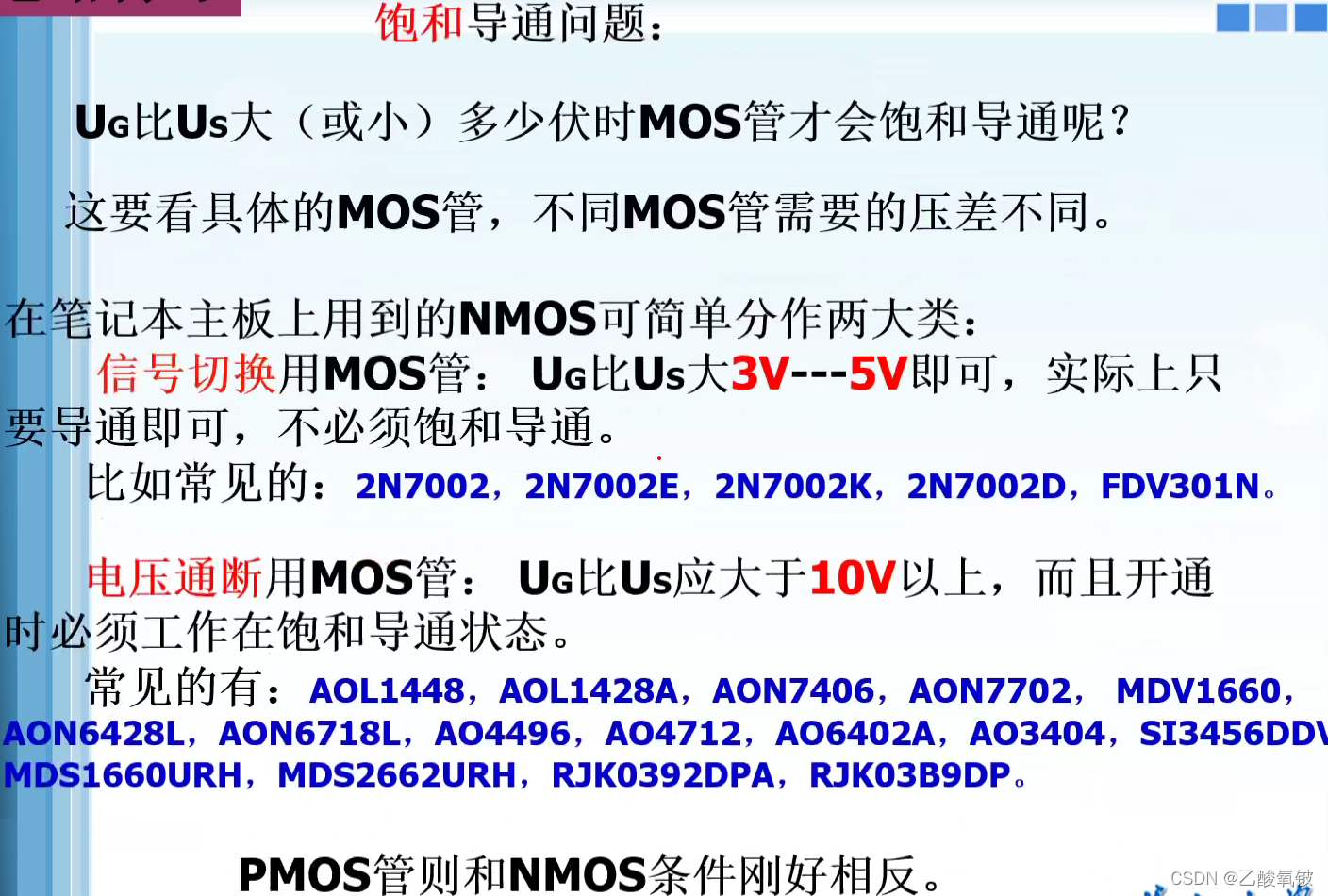

4.2 导通问题

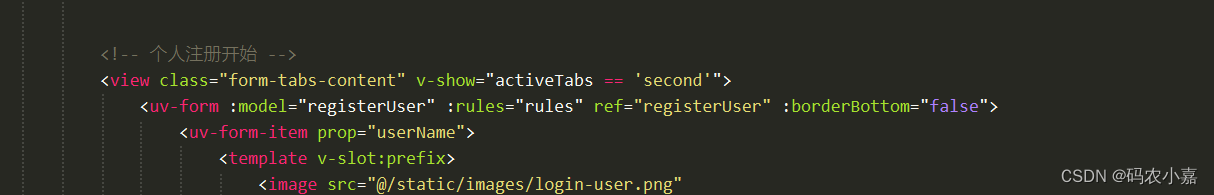

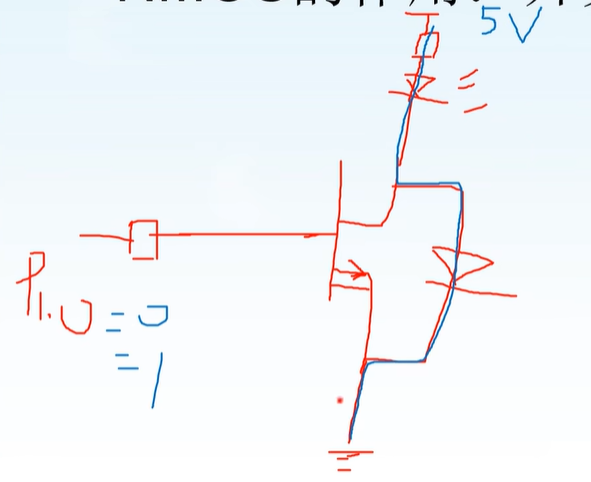

4.2.1 NMOS导通情况

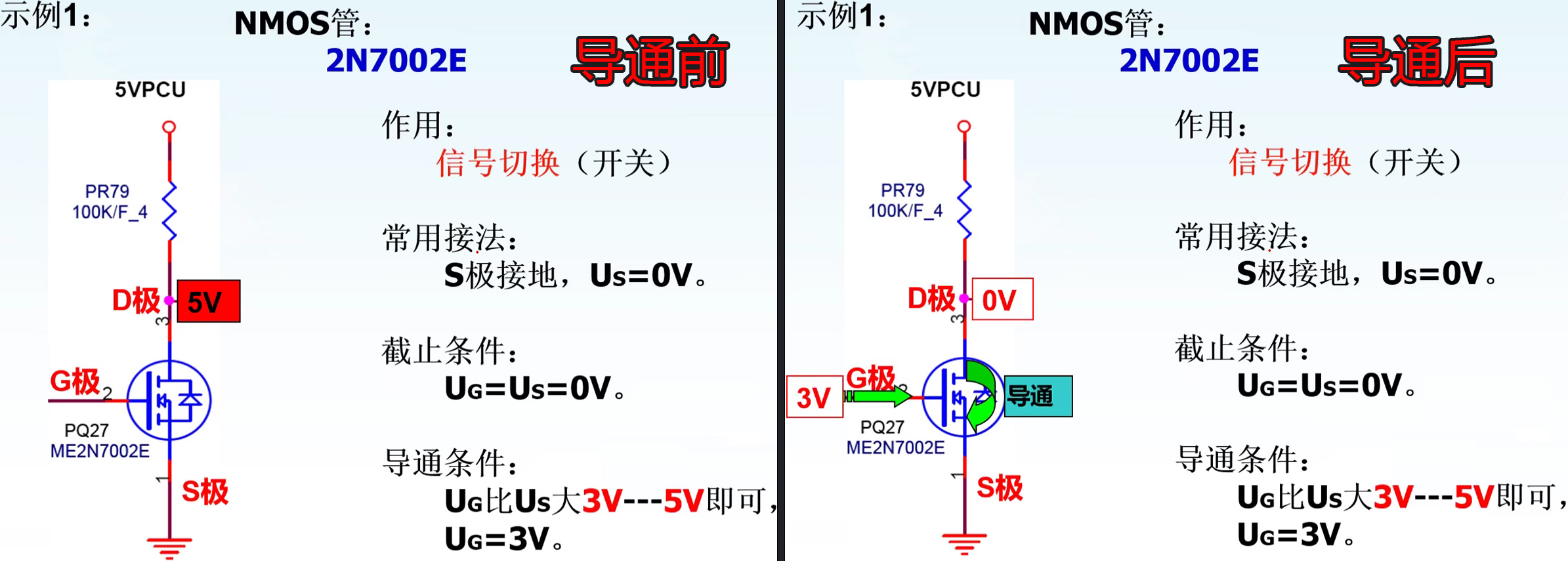

示例1:

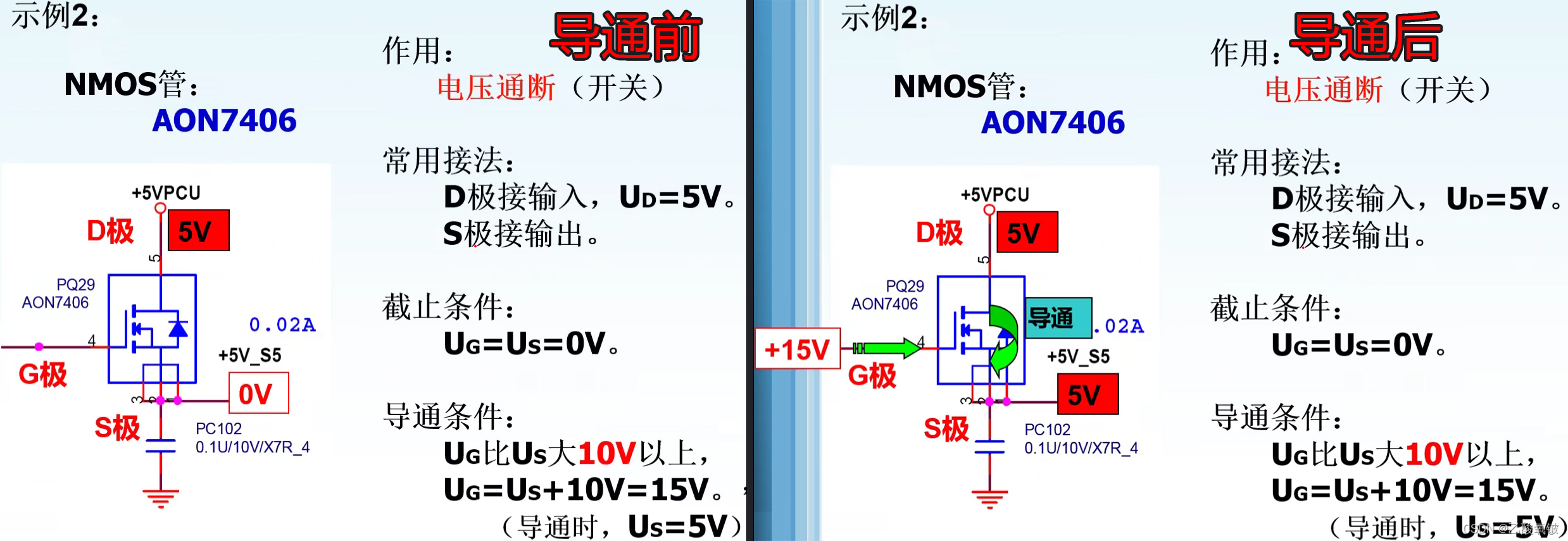

示例2:

4.2.2 PMOS 导通情况

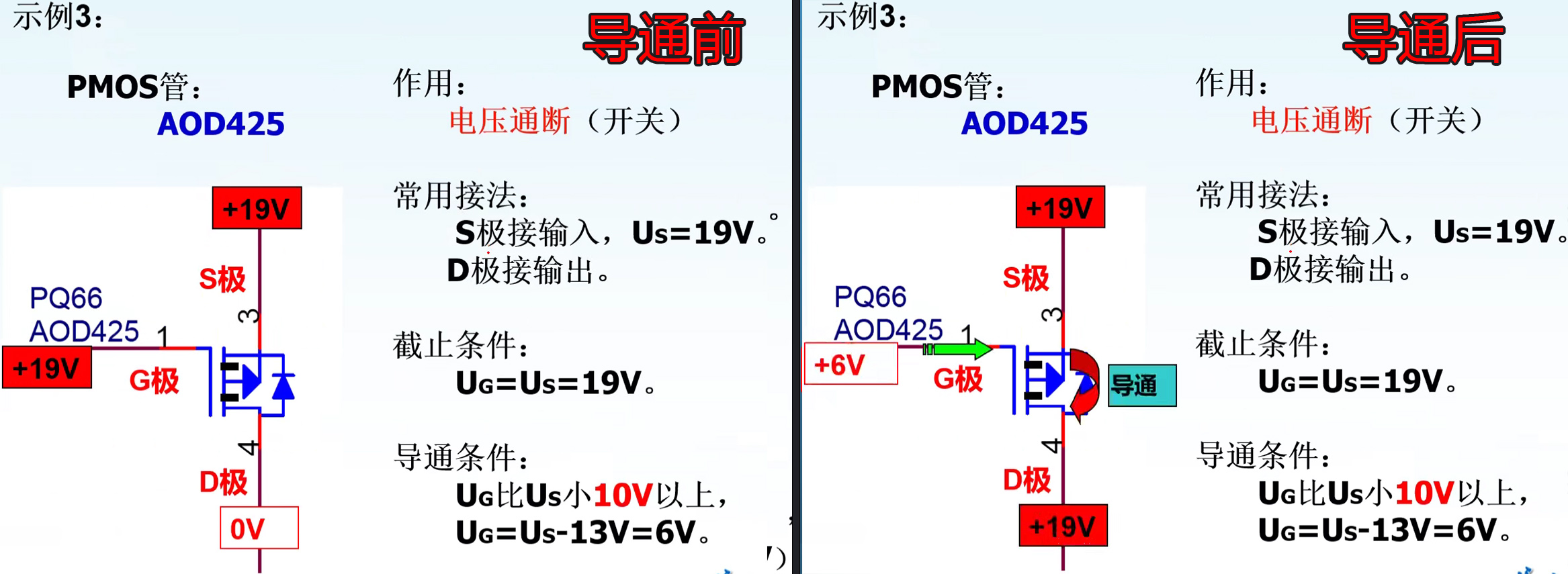

实例3:

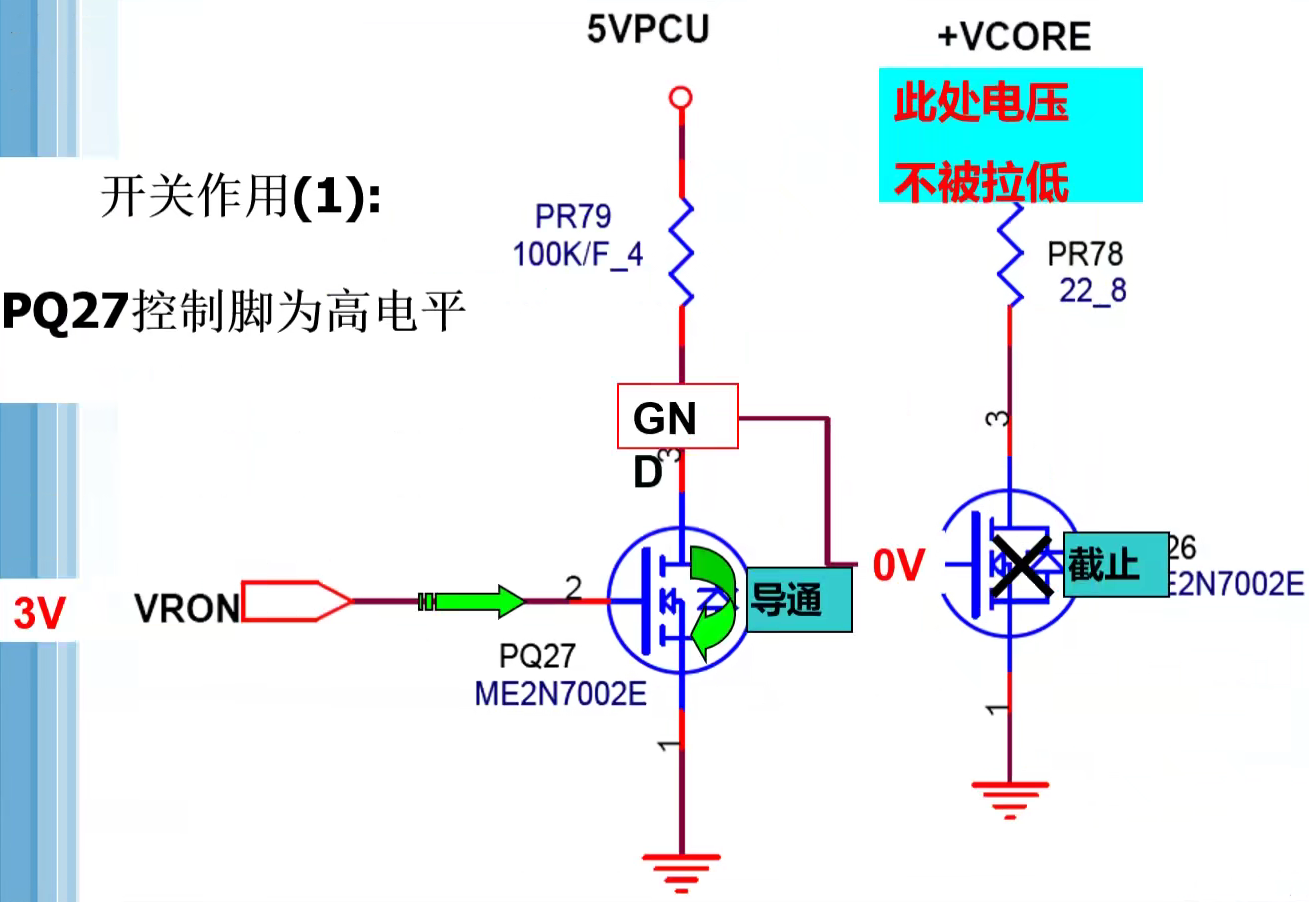

开关作用:

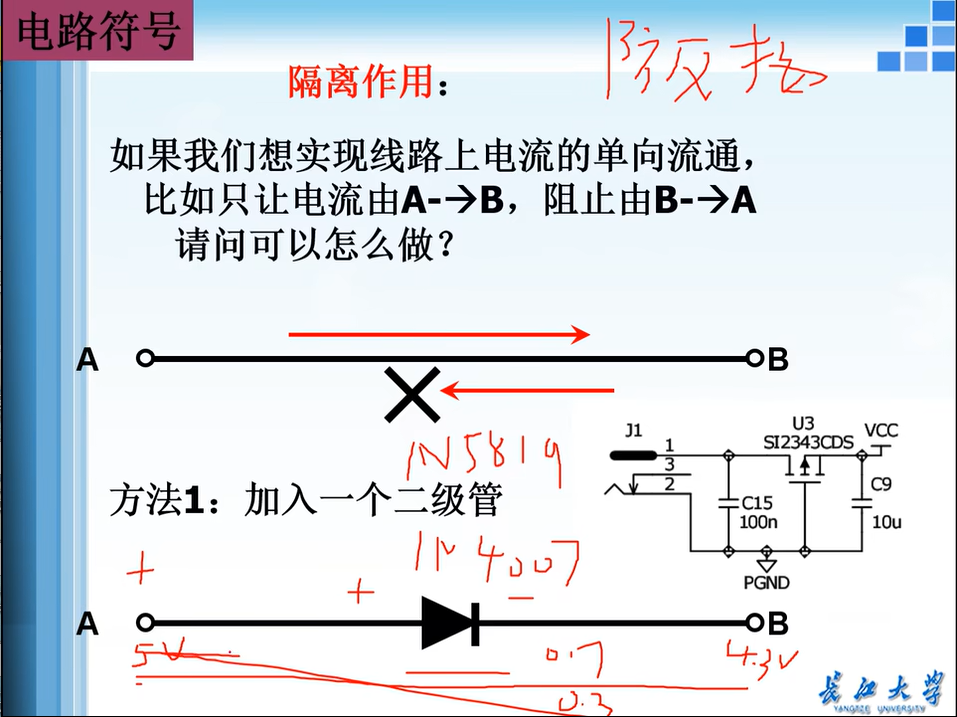

4.3 防反接

使用如 1N407 或者 1N5819 之类的二极管防反接有压降,但是如果使用 PMOS 管做防反接就没问题了。