很多同学想要了解IC后端,今天大家分享了数字IC后端的学习入门笔记,供大家学习参考。

很多人对于后端设计的概念比较模糊,需要做什么也都不甚清楚。

有的同学认为就是跑跑 flow、掌握各类工具。

事实上,后端设计的工作远不止于此。可以说是包含但不限于上述的内容。

如果非要用一句简单的话概括后端设计需要做的工作的话。

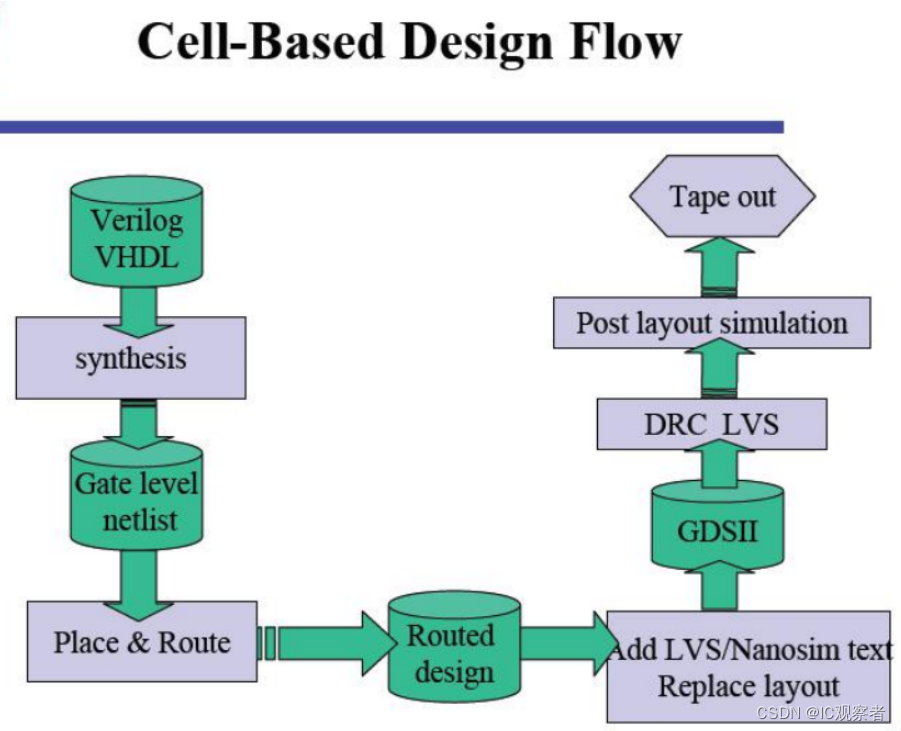

就是将前端设计的 RTL 代码转化成门级网表,最终生成 GDSⅡ文件,到这里就可以拿到工厂进行流片生产了。

为了完成上述的工作,后端设计工程师就需要进行逻辑综合、形式验证、物理实现、时钟树综合、寄生参数提取、版图物理验证等一系列高端操作。

在整个芯片设计流程中数字IC后端也是举足轻重的。发展下去,是越老越吃香的,做技术专家也只是时间问题。

布局与布线(Auto Placement & Route ,AP&R)

传统上将布局与布线前的工作称之为前端(Front End),而布局与布线之后的工作称为后端(Back End)。布局的目的在于产生制作掩膜所需的GDSII文件。同时也产生布局后的网表文件(Netlist)及标准延迟文件(SDF)。

后端设计所用到的工具

• 仿真工具:Mentor modelsim/Questasim

• 综合工具(带DFT):Synopsys DC

• 时序分析:Synopsys PT

• 形式验证:Cadence LEC

• 后端APR(Auto Placement &Route)Cadence SoC Encounter

• 后端参数提取:Mentor Calibre

IC设计全流程

- 设计输入 (Ultraedit,Vi等)

- 仿真(前、后,Modelsim)

- 综合(DC,with DFT)

- 形式验证 (Confrml,LEC)

- 时序分析 (PT,STA)

- 后端APR(Encounter)

- 参数提取、验证(Calibre)

关于IC设计全流程介绍,芯学长网有详细介绍,也有IC设计岗位查询等,对于IC设计不了解的同学,可以点进去网站去看看,对于IC设计有个整体的认识。

理解流程,明确概念

主要流程:

RTL——仿真——综合——自动布局布线——参数提取

• 穿插时序分析,形式验证等步骤

列举一例,演示一下流程!

所选实例为:MY_CHIP.v ;

RTL——仿真——综合

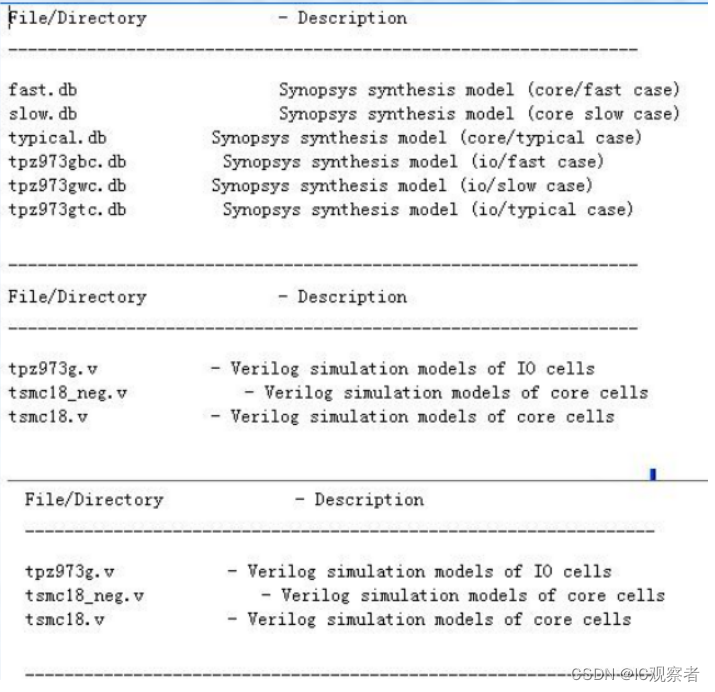

所使用的工艺为TSMC018

关于库的一些说明

数据准备

• 1、新建一个文件夹(如:soce_pad)将所用到的库copy进来:

lib+addbonding.pl+addIoFiller.cmd+ioPad.list

• 2、将要用到的源文件添加进来:

MY_CHIP.vg+MY_CHIP_PAD.v+pad_locs.

io+MY_CHIP_PAD.sdc

• 3、实验时使用TSMC 0.18工艺,

2、关于1中源文件的说明

MY_CHIP.vg是DC综合之后生成的门级网表文件。

• MY_CHIP_PAD.v是chip-level Netlist (自己编写),就是输入输出端口,用以IC系统与外部环

境的接口。与组成集成电路核心电路的单元不同,I/O PAD 是直接与外部世界相连接的特殊单元。

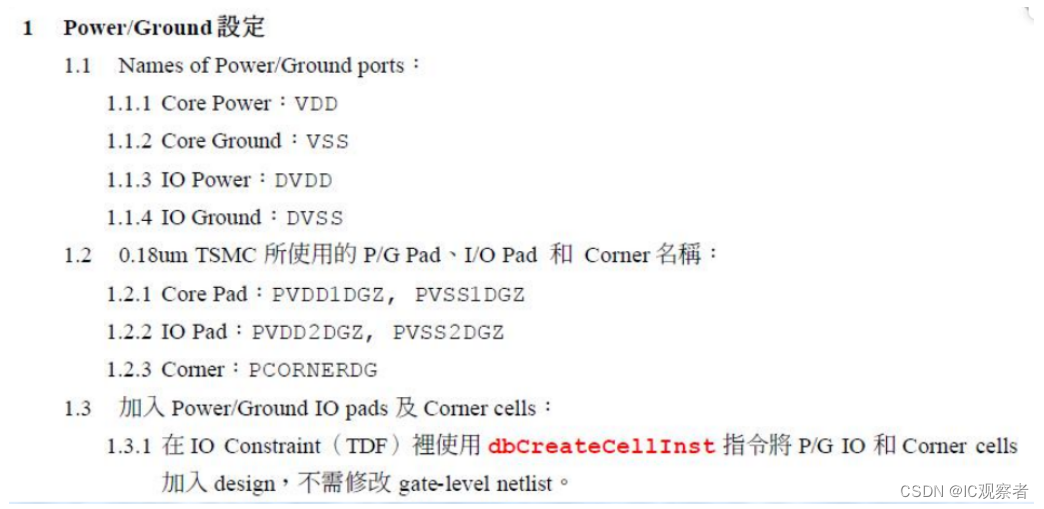

请参看文档DTS-041028-00-000.pdf,列出了TSMC 0.18所使用的P/G Pad、I/O Pad 和Corner

名称。参看lib库中tpz973g.lef技术库,列出了相关Pad的宏模块。结合所给例子MY_CHIP_PAD.v,

编写自己的chip-level Netlist 。

注意我们使用的是TSMC18工艺,pad名称的部分截图:

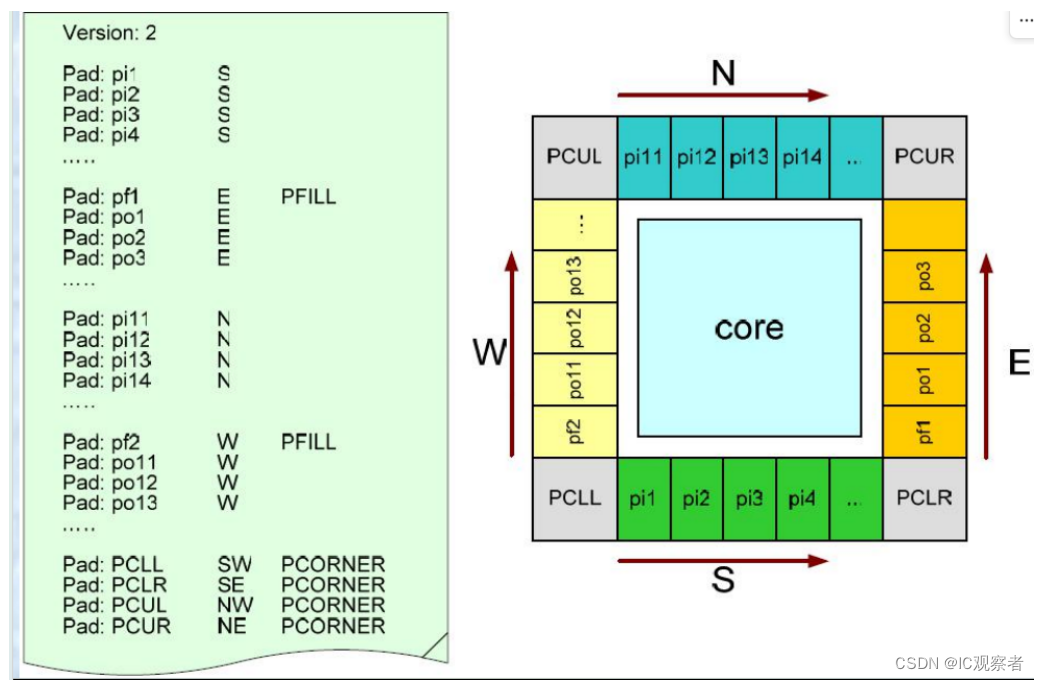

pad_locs.io文档就是编写添加进来的pad的摆放位置,如图示:

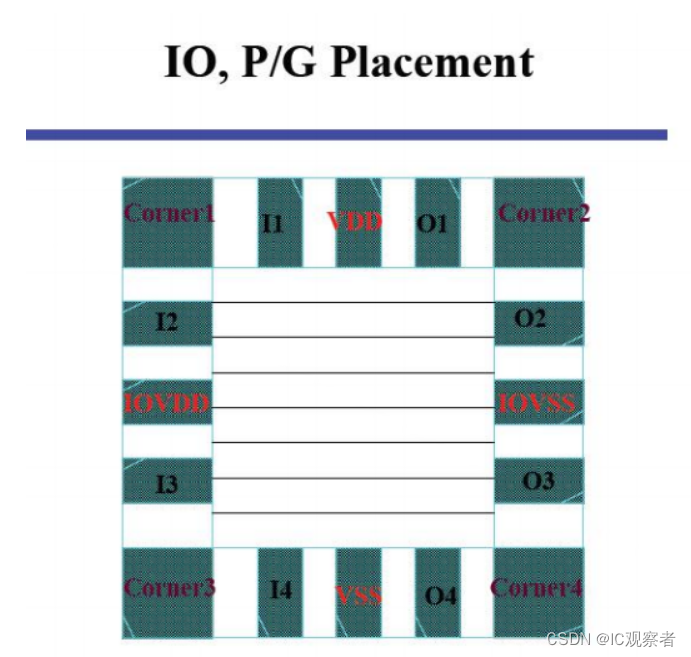

输入、输出、电源和地的摆放位置示例

MY_CHIP_PAD.sdc文件是DC综合之后的时序约束文件,需要进行修改!只需保留clk和输入输出的

延迟约束信息,其他删除!修改输入输出信号:输入信号前要加i,输出信号前加o,clk信号不变。参考示例文件进行修改。