〇、综述

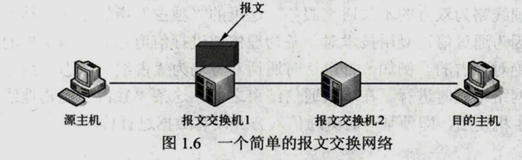

本章介绍并行数据端口(P0_D P1_D)和串行外设接口(SPI),用于在AD9361和BBP之间传输数据和控制/状态信息。

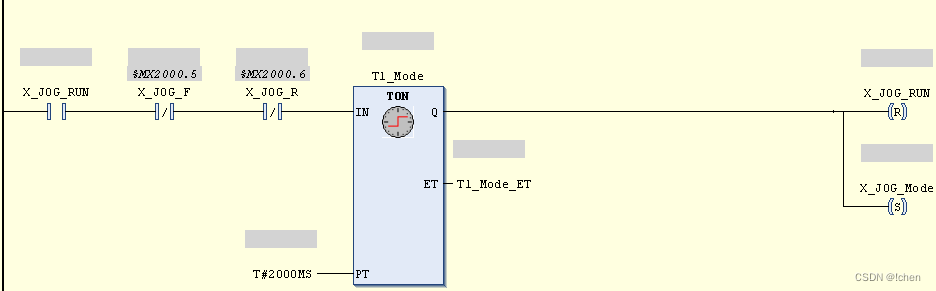

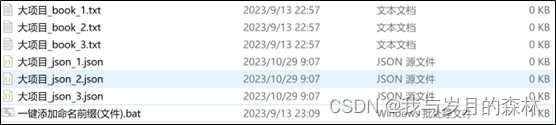

下图显示了这些接口,并提供了AD9361和BBP在宽带无线系统中的使用方式的高级视图。数据接口工作在两种模式之一:标准CMOS兼容模式或低压差分信号(LVDS)兼容模式。每个接口都具有以下各节中所述的独特特征。

-

使用 CMOS 模式时

• 保持单端CMOS逻辑兼容性。

• 可以使用一个或两个数据端口。使用两个端口可实现更高的数据吞吐量。

• 一个或两个数据端口支持频分双工 (FDD) 和时分双工 (TDD) 操作。 -

使用 LVDS 模式时:

• 数据端口信号为差分LVDS,允许AD9361和BBP之间实现高达30cm的PCB走线/连接器互连。{划重点,这就是做FMC或者多片Catalina使用时一般使用LVDS的一个原因,对的,ADI早些年就这样叫AD9361的,直译的捷变频收发器没有灵魂}

• 只有数据端口(包括时钟和其他相关定时信号)与LVDS兼容。

• 支持FDD和TDD操作。

AD9361 数字接口

一、CMOS 模式数据路径和时钟信号

在这种模式下,AD9361数据路径接口可以使用一个或两个并行数据端口在AD9361和BBP之间传输数据样本。总线传输使用简单的硬件握手信号进行控制。这两个端口可以在FDD模式或双向TDD模式下运行。在FDD模式下,一半的位同时发送数据,另一半同时接收数据。在TDD模式下,发射数据和接收数据在不同时隙的同一引脚上的AD9361和BPP之间交替传输。对于不需要快速有效数据速率的应用,可以使用单个端口来最大限度地减少与AD9361的连接。数据路径接口由以下各节中描述的信号组成。

[1] P0_D[11:0] & P1_D[11:0]

- 端口0(P0)和端口1(P1)都有一个12位并行数据总线(D[11:0]),用于在BBP和AD9361之间传输数据。每条总线在大小和功能上都与另一条总线相同,因此 D[11:0] 用于指代 P0 或 P1。这些总线可以配置为仅传输、仅接收或双向。

[2] DATA_CLK

DATA_CLK信号作为Rx数据路径的主时钟提供给BBP。在CMOS模式下,它在内部产生,并在DATA_CLK_P引脚上输出(DATA_CLK_N未连接)。P0、P1 或两个端口使用相同的时钟,具体取决于数据总线配置。BBP使用此主时钟作为接口数据传输和基带数据处理的定时基准。DATA_CLK在接收操作期间通过双边沿捕获 (DDR) 或单上升沿捕获 (SDR) 数据传输提供源同步时序。 产生的DATA_CLK频率取决于系统架构(例如,RF通道数、过采样程度和带宽模式)。

[3] FB_CLK

FB_CLK是在CMOS模式下从BBP驱动到FB_CLK_P引脚的反馈(环回)版本的DATA_CLK(FB_CLK_N未连接)。FB_CLK允许源同步定时和突发控制信号(TX_FRAME、ENABLE 和 TXNRX)的上升沿捕获。FB_CLK 还提供具有双边沿捕获 (DDR) 或单上升沿捕获 (SDR) 的源同步时序,用于 Tx 突发期间的 D[11:0] 数据信号(P0 和 P1)。请注意,FB_CLK必须是DATA_CLK的回馈版本(完全相同的频率和占空比),但两个时钟信号之间没有相位关系要求。

[4] RX_FRAME

RX_FRAME由AD9361驱动,以识别Rx数据路径(P0和P1)的有效数据。跳变高电平表示帧的开始。RX_FRAME可以设置为突发开始时的单个高转换并在整个突发期间保持高电平,也可以设置为在每个帧开始时具有上升沿的脉冲序列(50% 占空比)。在CMOS模式下,该信号从RX_FRAME_P引脚输出(RX_FRAME_N可以保持未连接状态)。

[5] TX_FRAME

TX_FRAME由 BBP 驱动,用于识别 Tx 数据路径(P0 和 P1)的有效数据。跳变高电平表示帧的开始。BBP可以将TX_FRAME设置为突发开始时的单个高转换,在整个突发期间保持高电平,也可以TX_FRAME设置为在每个帧开始时具有上升沿的脉冲序列(50%占空比)。

AD9361接受任一格式。在CMOS模式下,该信号输入到TX_FRAME_P引脚(TX_FRAME_N接地)。AD9361发送零数据(全部为零),直到第一个TX_FRAME指示有效数据。当 Tx 路径在 FDD 独立模式下完成传输操作并且数据路径未自动刷新时,此功能非常有用。在这种情况下,TX_FRAME引脚可以保持低电平以完成数据刷新操作。

[6] ENABLE

ENABLE由BBP驱动至AD9361,以在TDD模式下提供数据传输突发控制(以及TXNRX)。BBP 在单个DATA_CLK周期内置位 ENABLE 以指示每个突发的开始。随后再次断言至少一个DATA_CLK周期,以指示每个突发的结束。

AD9361在内部跟踪ENABLE脉冲序列,以将每个脉冲正确解释为每个突发的开始或结束。ENABLE 信号也可以配置为电平模式,在该模式下,边沿转换(不是脉冲)确定 ENSM 何时在状态之间移动。在每个 ENABLE 启动事件期间在 TXNRX 上采样的电平控制 TDD 模式下的总线方向。开始和结束延迟(从AD9361采样的ENABLE脉冲与总线上存在的第一个和最后一个有效数据样本之间)因数据路径配置而异。RX_FRAME和TX_FRAME信号分别用于通过BBP和AD9361确定有效数据。FB_CLK信号用于对该输入进行采样。

在FDD模式下,使能信号用作单个控制输入,以确定ENSM的状态。还有一种替代FDD模式,在该模式下,使能信号可以重新定义为RxON,这是控制Rx功能的ENSM的直接硬件控制输入。在这种模式下(称为FDD独立控制模式),BBP独立控制Rx功能,从而节省功耗。

[7] TXNRX

TXNRX由BBP驱动至AD9361,并在数据总线处于TDD模式时提供数据传输突发控制(以及ENABLE)。当AD9361对ENABLE进行高电平采样以启动突发时,还会对TXNRX上的电平进行采样以确定数据方向。在TDD模式下,TXNRX采样高表示发射突发,TXNRX采样低表示接收突发。

在整个数据传输突发期间,必须保持 TXNRX 信号电平(有效逻辑电平)。TXNRX信号可以在对ENABLE启动脉冲进行采样之前建立任意数量的周期(≥0),并且可以在对ENABLE完成脉冲进行采样后改变任意数量的周期(≥0)。需要注意的是,TXNRX 信号只应在 ENSM 处于 ALERT 状态时更改状态,因为 TXNRX 信号直接在 TDD 模式下为合成器上电和断电。

在正常的FDD模式下,TXNRX信号被忽略,但必须保持在有效的逻辑电平。还有一种替代的FDD模式,在该模式下,TXNRX信号可以重新定义为TxON,这是控制Tx功能的ENSM的直接硬件控制输入。在这种模式下(称为FDD独立控制模式),BBP独立控制Tx功能,从而节省功耗。

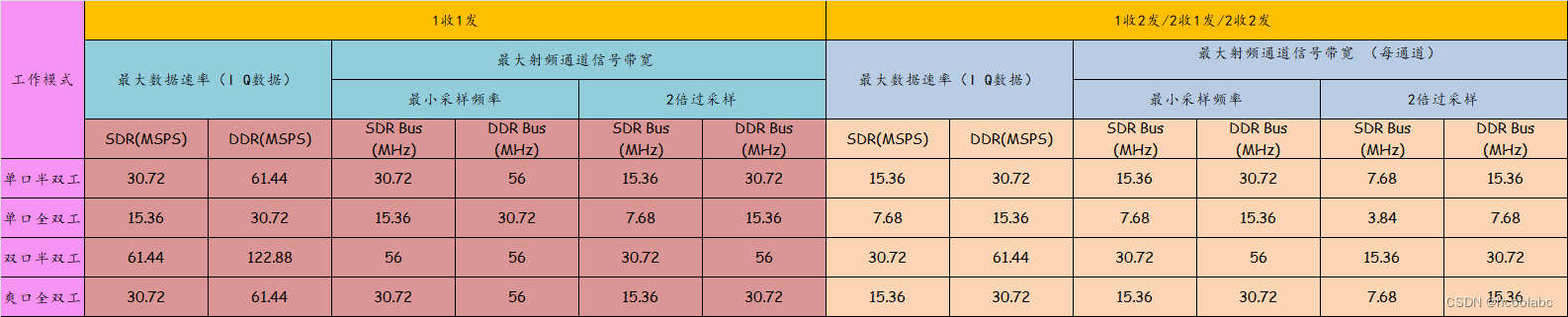

[8] CMOS MAXIMUM CLOCK RATES AND SIGNAL BANDWIDTHS

下表列出的数据比较了CMOS数据总线配置在不同允许工作模式下的最大数据时钟速率和最大RF信号带宽。列出了两种情况下的最大RF带宽:使用避免混叠的最小采样速率进行采样,以及使用2×过采样。每种模式的详细信息将在后续部分中给出。最大DATA_CLK速率限制为61.44 MHz,因此数据速率受此系数和56 MHz最大模拟滤波器带宽的限制。