来源:A SiC Trench MOSFET concept offering improved channel mobility and high reliability

SiC MOSFET设计挑战

虽然碳化硅的使用由于是一种宽带隙材料而具有许多优点,但与硅也存在一些值得注意的差异,这导致在制造基于4H-SiC多晶型的SiC MOSFET时面临许多挑战,4H-SiC是用于功率半导体器件的最突出的碳化硅多晶型。

SiC MOSFET面临的一个首要挑战是由于热氧化产生的碳相关界面缺陷,导致SiO2/SiC界面处的电子迁移率较低。由于在界面处此类带电点缺陷处的电子散射和电荷俘获效应,沟道迁移率在5-70 cm2/Vs范围内,这通常只占体迁移率(约400 cm2/Vs)的一小部分(等于沟道掺杂浓度的体掺杂浓度下的值)。能量水平位于SiC较大带隙内的缺陷可以通过捕获或发射电子在更长的时常范围内相互作用。这种效应会导致阈值电压的滞后。在这些近界面陷阱(NIT)处反型和积累电荷的捕获和发射会导致更复杂的阈值电压变化,这取决于施加的栅极电压波形和温度。尽管观察到的变化大部分是完全可逆的,但需要更复杂的栅极氧化工艺来限制阈值电压不稳定性的更永久部分。

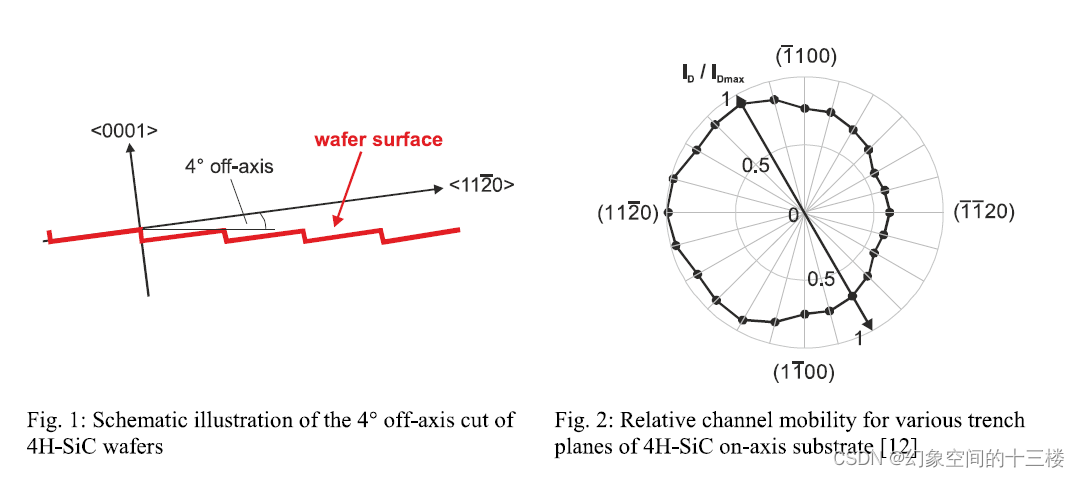

另一个需要解决的当今SiC器件的问题是商业上可用的SiC衬底的4度偏离轴倾斜。这是外延层生长所必需的,因此无法避免。由于倾斜,晶圆表面与(0001)晶体c平面不完全重合,导致表面粗糙和台阶,如图1所示。实验表明,沟道迁移率强烈依赖于所选的晶面,如图2所示,最差和最佳沟道迁移率之间预计有近2倍的差距。

通过使用适当的后氧化退火步骤(例如一氧化氮退火),可以改善介电常数和界面特性,从而降低界面态密度。此处任何改进通常还会由于库仑散射和电荷俘获的影响减少而增加沟道迁移率。此外,阈值电压随温度和时间的漂移量也变小。由于SiC器件允许的电场强度比Si器件高约10倍,因此必须限制栅极氧化物中的电场强度以保持器件所需的可靠性。如下一节所讨论的,这种电场强度降低或限制必须通过适当的器件设计措施来实现。

元胞概念

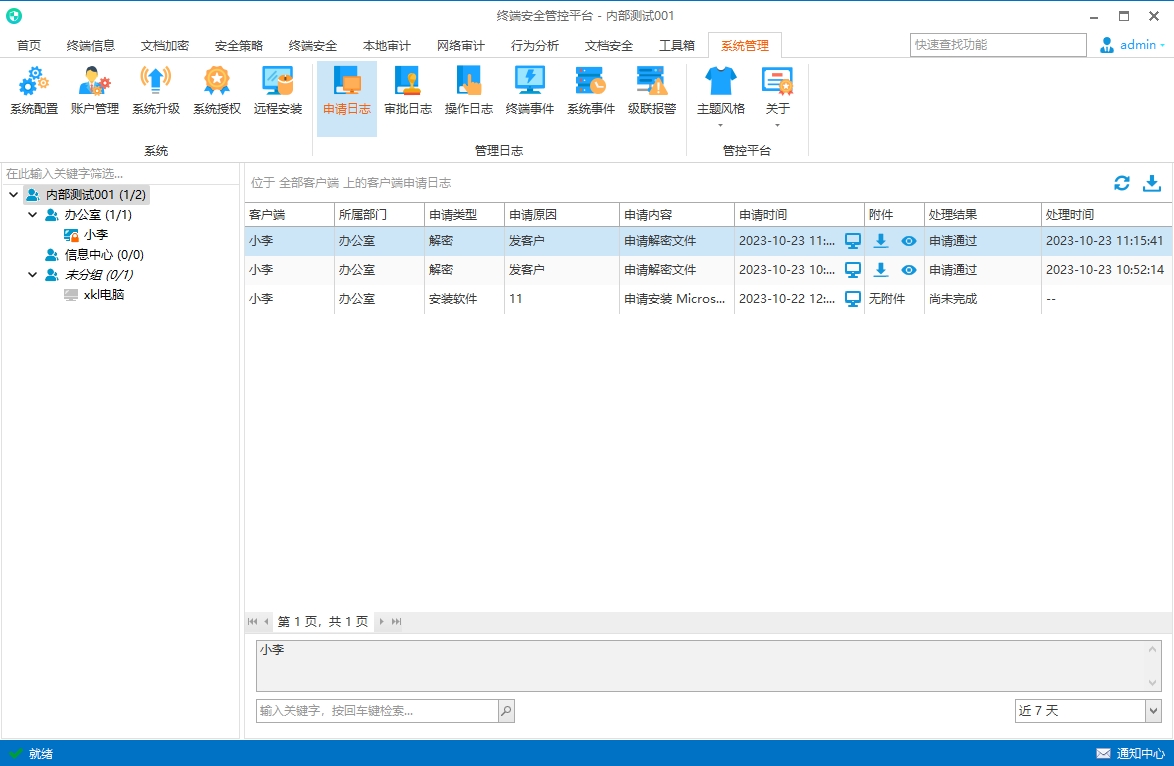

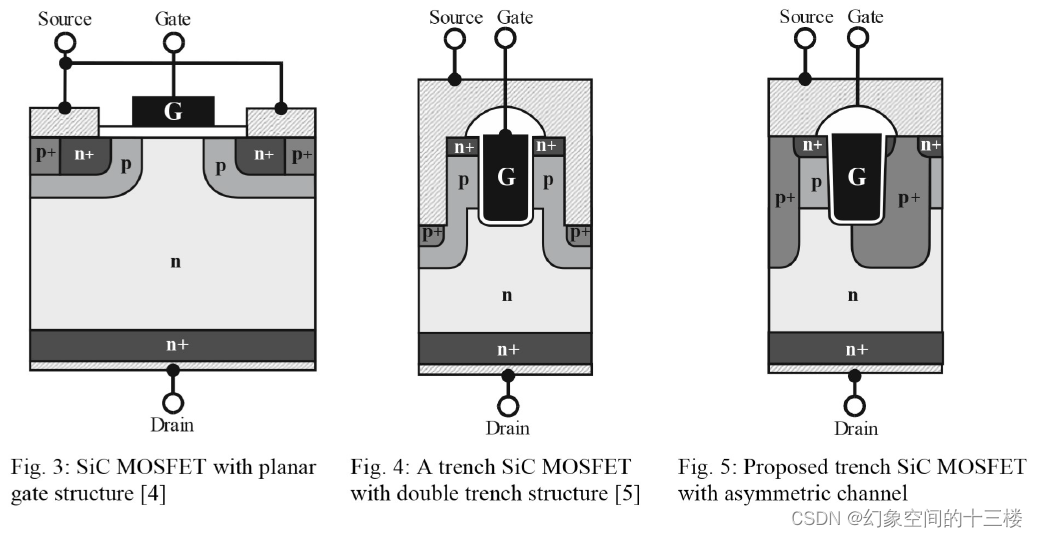

实现 SiC MOSFET 的第一个也是迄今为止最广泛使用的方法是使用平面栅极和准垂直结构,如图 3 所示。由于必须限制到达 SiO2/SiC 界面的电场,因此由结构的 p 阱代表的寄生 JFET 不像硅对应物那样不利。然而,横向沟道结构限制了结构的可扩展性,因此限制了可以实现的单位面积导通电阻。另一个缺点来自于横向沟道方向,这与之前讨论的低沟道迁移率和相对较高的界面陷阱密度有关。

图4显示了另一种使用双沟槽结构的方法。使用沟槽栅极会增加沟道宽度,即使使用非轴向材料,也能提供更高的沟道迁移率。然而,由于沟道沿不同的侧壁定向,对应于不同的晶面,每个沟道的特性会彼此不同。第二个沟槽连接到一个深的 p 阱,确保在 SiO2/SiC 界面处限制所需的电场,同时为体二极管导通提供足够大的区域。另一方面,需要第二个沟槽会对单元间距产生负面影响,从而限制可实现的沟道宽度。

文中的方法如图5所示。主沟道完全沿a平面定向,这提供了最佳的沟道迁移率和最低的界面陷阱密度。因此,以牺牲第二个沟槽侧壁作为活性沟道为代价,实现了最佳的沟道特性。 SiO2/SiC 界面再次被深p阱屏蔽。深度p型区域还充当体二极管的发射极,可用于续流运行。总之,这允许了非常紧凑的单元设计,并补偿了第二个侧壁上缺失的沟道,从而实现了单位面积导通电阻,约为典型DMOS单元的一半。由于沟道性能的提高,该器件可以很容易地由常用的栅极源极电压Vgs =+ 15V驱动。单元结构本身具有米勒电荷QGD与栅极源极电荷QGS的有利的较小比率。QGS相当大,因为沟道的很大一部分对它有贡献,即n*-型区域和所有通过衬底连接到源极的p-型区域。总之,这允许进行良好的开关控制,并具有非常低的动态损耗。特别是,该特性对于抑制由半桥拓扑中的寄生导通引起的额外损失至关重要。