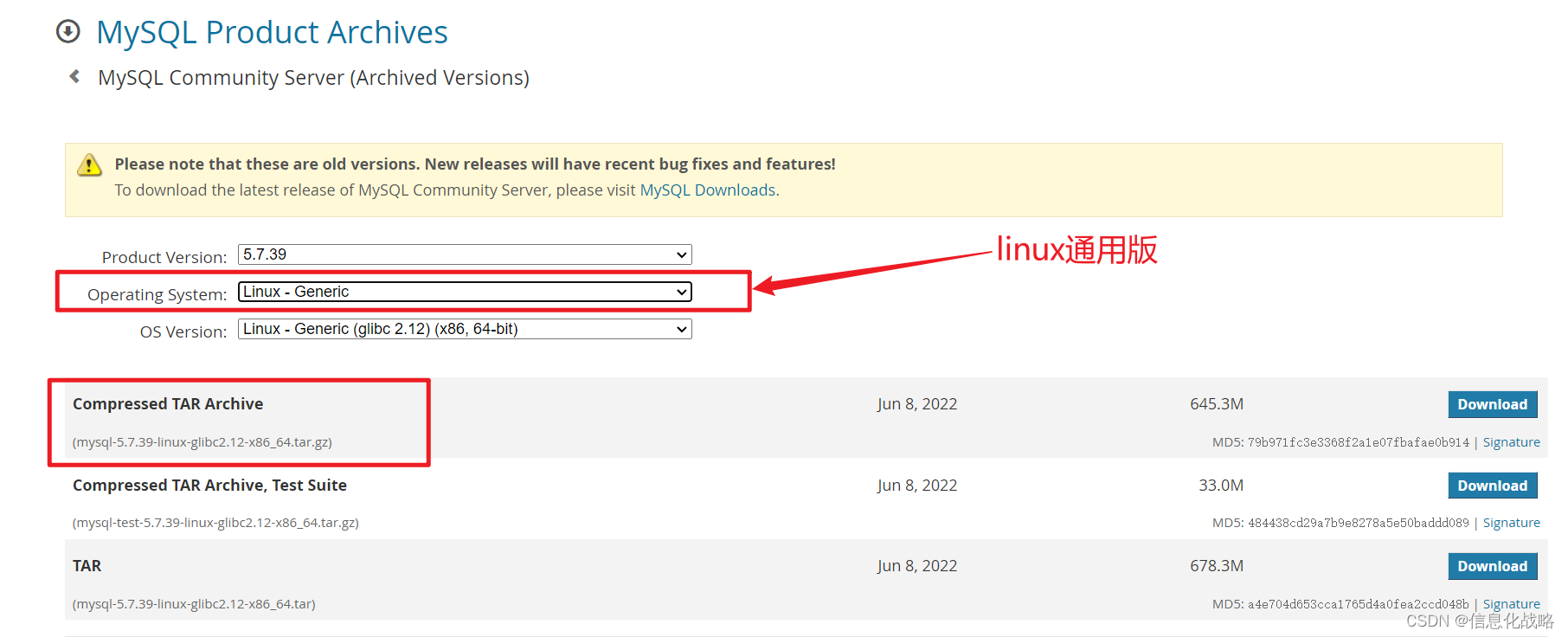

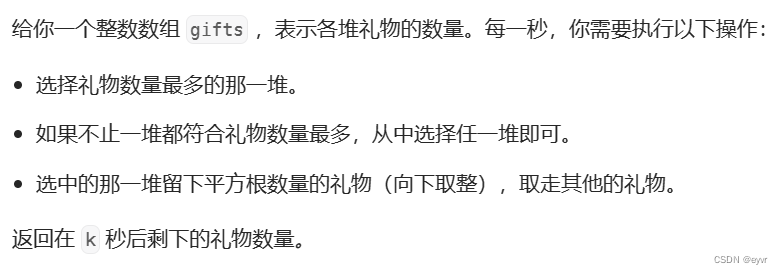

名称:ADI模数转换AD7091的SPI驱动

软件:QuartusII

语言:Verilog

代码功能:

完成ADI单通道模数转换器AD7091R的逻辑接口设计。1 MSPS、超低功耗、12-Bit ADC

(1)实现全部逻辑接口功能,完成对外设AD7091R访问;

(2)自行设计应用场景,构造相应数据;

(3)实现数据手册中的最高数据率;

(4)硬件平台以拿到手的开发板为准,自行完成设计与验证;

(5)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、时序仿真、下载验证等

演示视频:ADI模数转换AD7091的SPI驱动接口verilog_Verilog/VHDL资源下载

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

ADI模数转换AD7091的SPI驱动接口verilog_Verilog/VHDL资源下载名称:ADI模数转换AD7091的SPI驱动(代码在文末付费下载)软件:QuartusII语言:Verilog代码功能:完成ADI单通道模数转换器AD7091R的逻辑接口设计。1 MSPS、超低功耗、12-Bit ADC(1)实现全部逻辑接口功能,完成对外设AD7091R访问;(2)自行设计应用场景,构造相应数据;(3)实现数据手册中的最高数据率;(4)硬件平台以拿到手的开发板为准,自行完成设计与![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=217

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=217

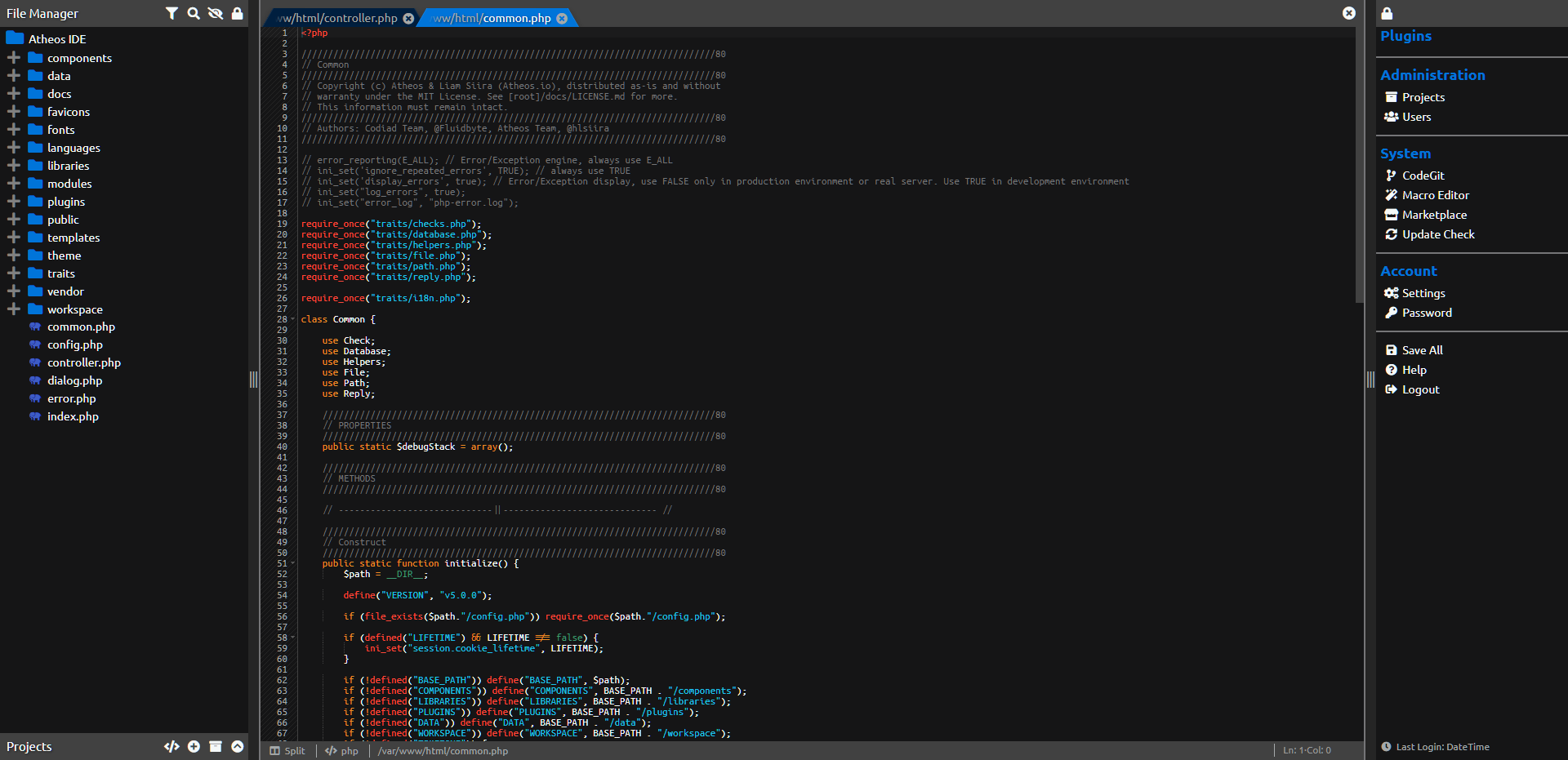

部分代码展示

module AD7091( input clk,//50MHz input reset,//高电平复位 //AD接口 output reg convst,//AD转换信号 output reg CS,//使能信号 output reg SCLK,//AD时钟 input SDO,//AD数据输入 output reg [11:0] AD_data//AD转换结果 ); reg [2:0] state=3'd0; parameter s_idle=3'd0;//空闲状态 parameter s_convst_low=3'd1; parameter s_convst_high=3'd2; parameter s_CS_low=3'd3; parameter s_SCLK=3'd4; parameter s_CS_high=3'd5; reg [7:0] convst_cnt=8'd0;//convst高电平时间计数 reg [3:0] bit_cnt=4'd0;//bit计数 reg [3:0] CS_high_cnt=4'd0;//CS高电平计数 always@(posedge clk or posedge reset) if(reset) state<=3'd0; else case(state) s_idle: state<=s_convst_low; s_convst_low://转换信号低电平状态 state<=s_convst_high; s_convst_high://转换信号高电平状态(等待t8最大650ns) if(convst_cnt>=8'd40)//等待800ns>650ns state<=s_CS_low; else state<=s_convst_high; s_CS_low: //CS低电平状态 state<=s_SCLK; s_SCLK: //SCLK读数状态 if(bit_cnt>=4'd13)//计数13bit state<=s_CS_high; else state<=s_SCLK; s_CS_high: if(CS_high_cnt>=4'd4)//延迟4*20ns,tquiet至少50ns state<=s_idle; else state<=s_CS_high;

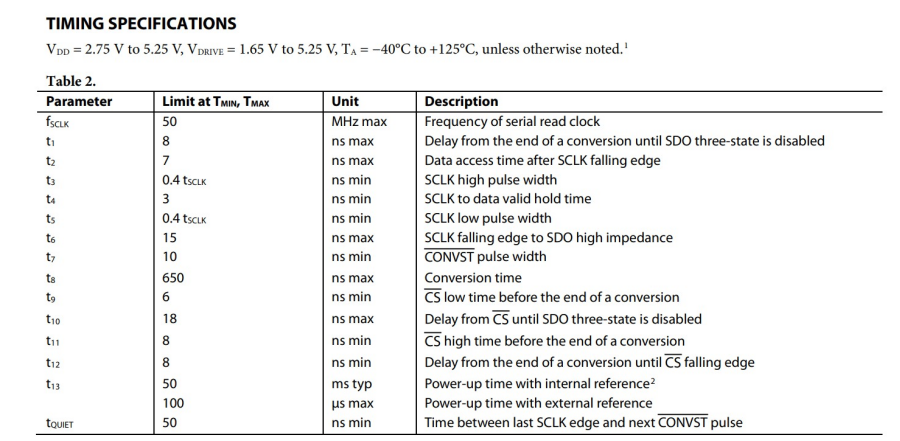

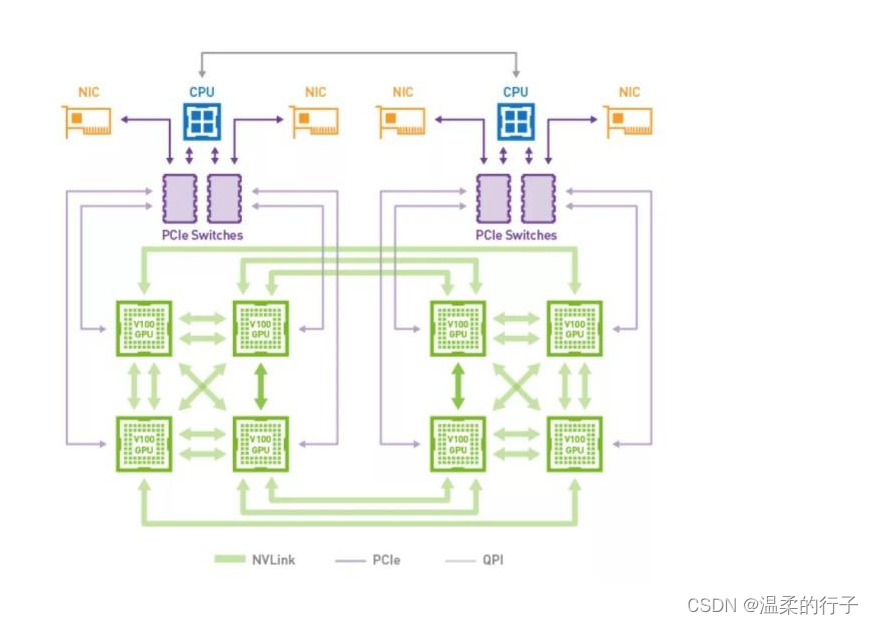

时序要求:

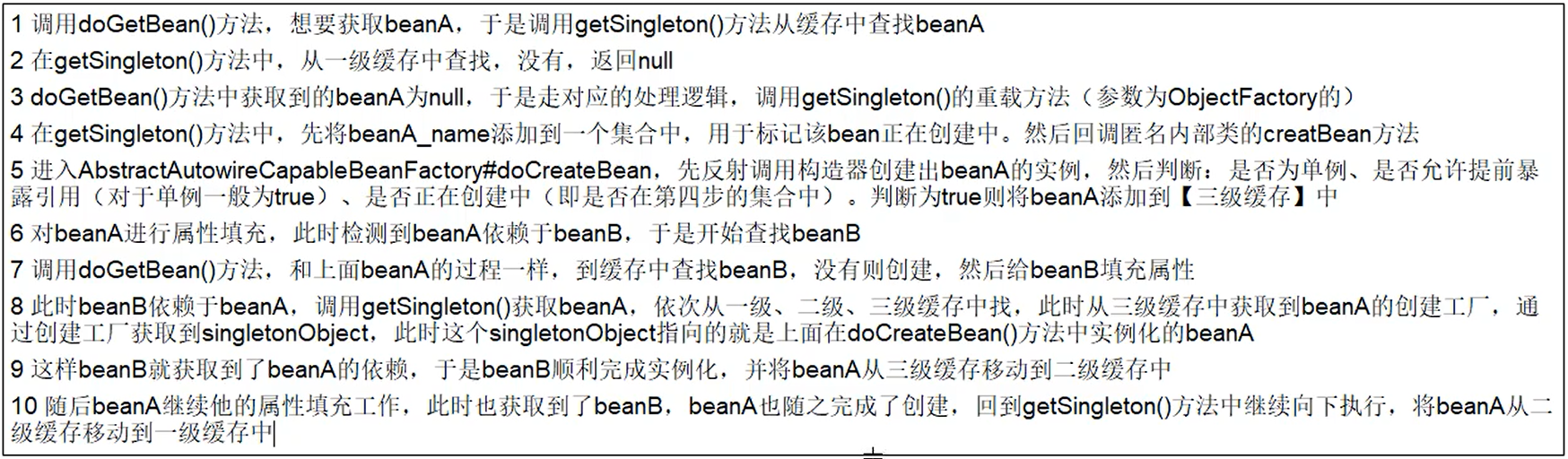

设计文档:

![]()

设计文档.doc

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图

附:AD7091R时序图和时序表