1、ARM架构中断机制介绍

本文不是从零开始讲解中断,对于中断的基本知识不再赘述,对中断不是很了解可以先学习ARM中断的文章。参考博客:《ARM架构的外部中断介绍(S5PV210芯片)》;

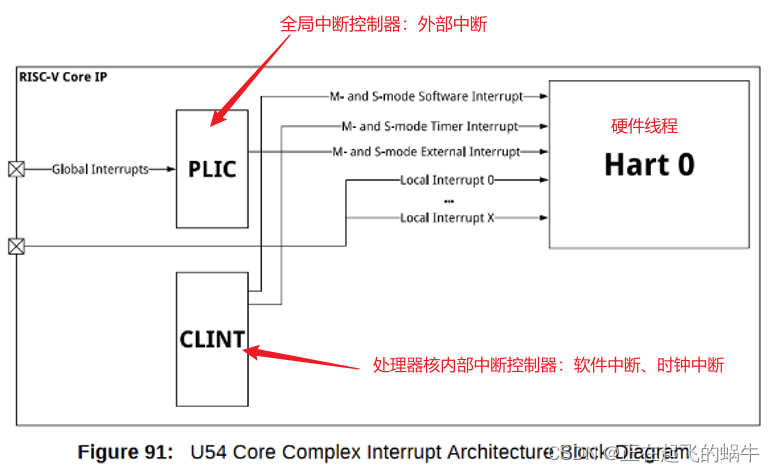

2、RIAC_V架构的中断控制器架构

(1)CLINT:负责处理器核内部产生的中断,包括软件中断和时钟中断,这些中断都是不依赖外部硬件的;

(2)PLIC:负责外部中断的调度。比如:可以给外部中断设置优先级,当多个外部中断同时发生时,PLIC按优先级进行排序,将高优先级的中断号发生到处理器核进行处理;

3、中断处理中的关键问题

3.1、如何注册异常处理函数?

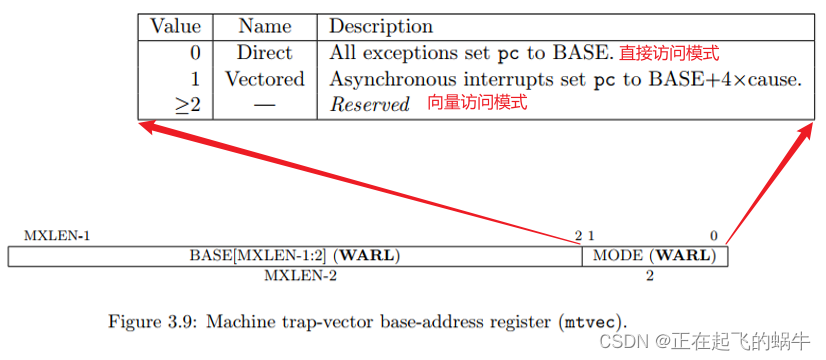

3.1.1、异常向量表基地址寄存器:mtvec寄存器

(1)将异常处理函数的地址写到mtvec寄存器中,低两位是模式位;

(2)当发生陷入时,硬件会自动跳转到mtvec寄存器中保存的函数地址执行;

补充:S模式也是类似的,有一个stvec寄存器;

3.1.2、异常向量表:直接访问模式

当M模式/S模式发生陷入时,硬件会自动跳转到异常向量表基地址寄存器中保存的地址处执行,需要在异常处理函数中读取mcause/scause寄存器开查询异常或者中断触发的原因;

3.1.2、异常向量表:向量访问模式

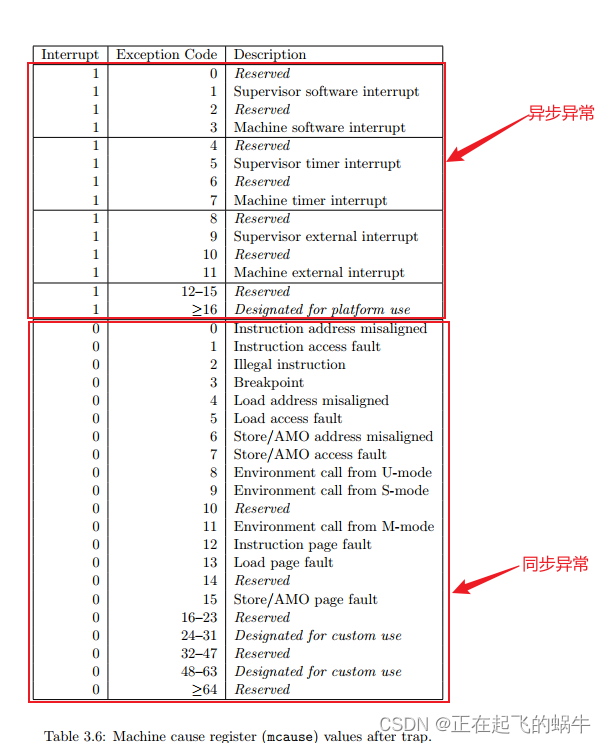

(1)中断触发后,同步异常会跳转到BASE(异常向量表基地址寄存器中保存的地址)处执行,异步异常(中断)会跳转到“BASE + 4 x 中断号”处执行。

(2)同步异常还是需要去查询mcause寄存器来知道是发生的哪个异常,而异步异常则是硬件直接跳转到对于的地址处执行。比如:发生M模式下的时钟中断,硬件会跳转到“BASE + 4 x 7”地址处执行。

总结:向量访问模式下,异步异常的处理效率会更高,因为是硬件直接跳转,但是构建异常处理函数也会更复杂;

3.2、发生异常时怎么跳转到异常处理函数执行?

(1)首先异常发生时跳转到异常处理函数时硬件完成的,软件只需要提前将异常处理函数地址写到异常向量表基地址寄存器中;

(2)硬件在跳转前会做一些处理。比如:报错当前PC到mepc中,把异常类型更新到mcause中等等;

3.3、怎么保护/恢复中断现场?

在异常处理函数的开始阶段保存异常上下文到栈中,包括通用寄存器、部分CSR寄存器;然后执行真正的处理异常的函数,异常处理完成,在返回前将栈中保存的异常上下文恢复;

3.4、异常处理函数中,怎么区分是哪个中断或者哪个异常?

进入到异常处理函数后,查询mcause和scause寄存器。

4、中断委托和中断注入

参考博客:《RISC-V架构——中断委托和中断注入》;

5、PLIC:中断控制器

5.1、中断控制器初始化

(1)设置中断优先级阈值。当发生的外部中断小于阈值时会被屏蔽,不会上报到处理器进行处理;

(2)设置各个中断的优先级和使能;

5.2、中断控制器工作流程

(1)当发生大于阈值的中断后,首先跳转到异常处理函数处执行,判断属于外部中断;

(2)读取中断请求寄存器(claim),查询发生的哪个外部中断;

(3)调用对应外部中断的处理函数;

(4)处理完中断后,写中断完成寄存器(complete),告诉PLIC中断控制器该中断已经处理完成;