最近在使用Xilinx 7系列FPGA XC7A100T时,运行MicroBlaze软核处理器,添加了AXI TIMER IP核,并使能定时器溢出中断,发现定时器触发中断后,无法返回主函数的问题,最后发现修改编译器优化等级就正常了。

FPGA型号是XC7A100T-FGG484,开发环境是Vivado 2018.3。

应用代码大致如下结构:

uint32_t cnt_1ms = 0;

int main(void)

{

//1. 定时器初始化

//2. 定时器中断初始化1ms

while(1)

{

if(cnt_1ms > 500)

{

cnt_1ms = 0;

set_led_toggle();

}

}

return 0;

}

void mb_timer0_handler(void)

{

//1ms溢出

cnt_1ms++;

//xil_printf("cnt_1ms = %d\r\n", cnt_1ms);

//清除中断

XTmrCtr_ClearStats(&timer0);

return;

}

编译版本选择Debug版本,LED正常500ms闪烁一次。

编译版本选择Release版本,LED状态无变化,中断打印的cnt_1ms变量的值一直在增加,没有清零,说明定时器溢出中断触发之后,没有返回主函数。

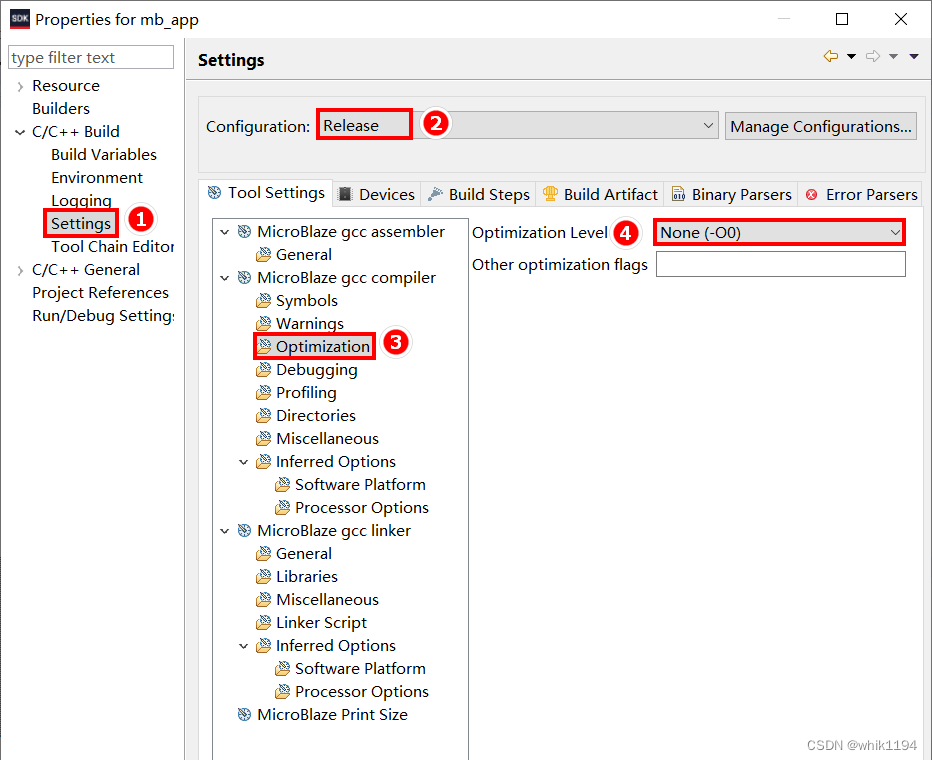

最后发现,把Release版本的编译器优化等级改为0就正常。

这种情况不是所有的工程都会出现,只有在一些特定情况下会出现,目前不清楚发生的规律。