一、spi基础知识

1.1、spi基础知识一

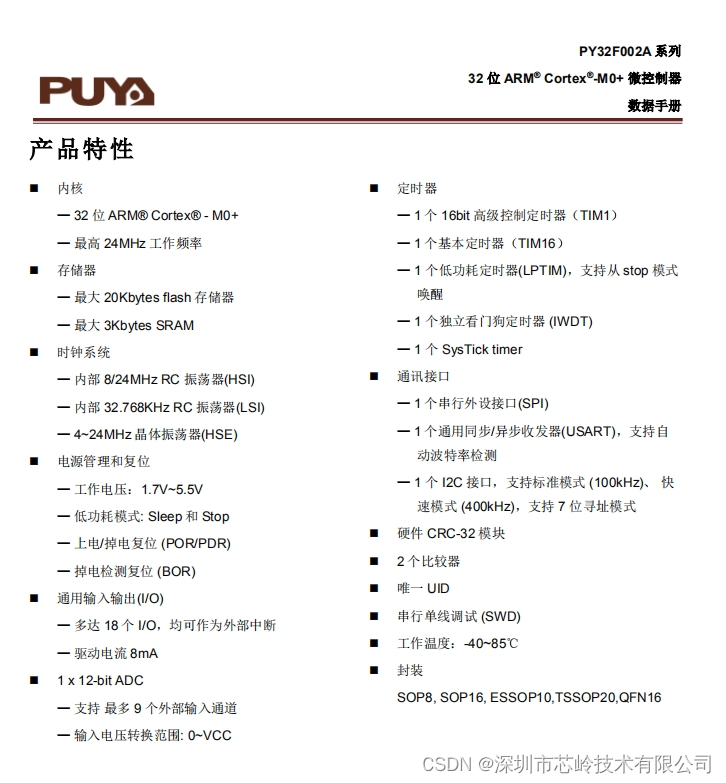

SPI(Serial Peripheral Interface,串行外设接口)是由摩托罗拉(Motorola)在1980前后提出的一种全双工同步串行通信接口,它用于MCU与各种外围设备以串行方式进行通信以交换信息,通信速度最高可达25MHz以上。

SPI接口主要应用在EEPROM、FLASH、实时时钟、网络控制器、OLED显示驱动器、AD转换器,数字信号处理器、数字信号解码器等设备之间。

SPI通常由四条线组成,一条主设备输出与从设备输入(Master Output Slave Input,MOSI),一条主设备输入与从设备输出(Master Input Slave Output,MISO),一条时钟信号(Serial Clock,SCLK),一条从设备使能选择(Chip Select,CS)。与I²C类似,协议都比较简单,也可以使用GPIO模拟SPI时序。

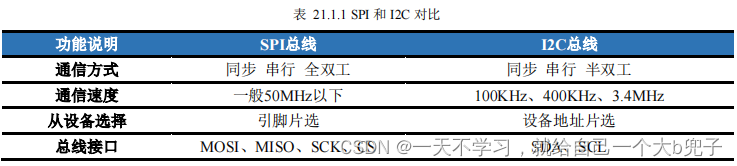

SPI和I²C对比如表 21.1.1 所示。SPI可以同时发出和接收数据,因此SPI的理论传输速度比I²C更快。SPI通过片选引脚选择从机,一个片选一个从机,因此在多从机结构中,需要占用较多引脚,而I²C通过设备地址选择从机,只要设备地址不冲突,始终只需要两个引脚。

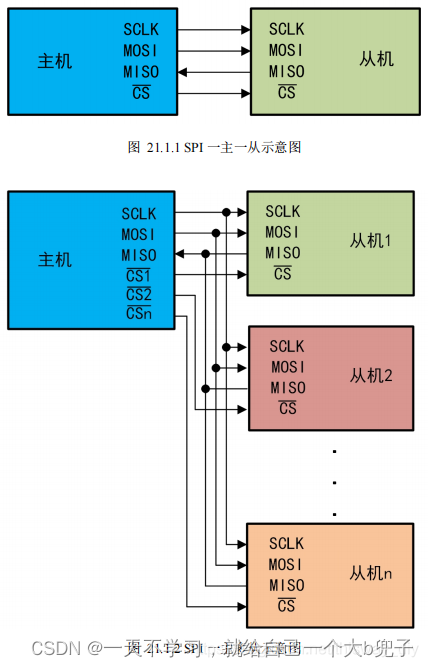

物理拓扑结构

SPI可以一个主机连接单个或多个从机,每个从机都使用一个引脚进行片选,物理连接示意图如图21.1.1 和 图 21.1.2 所示。

传输模式

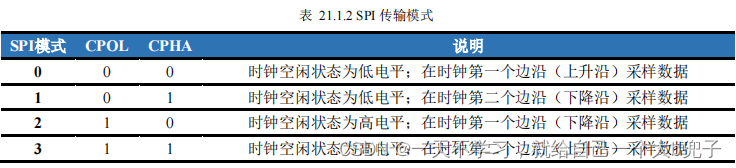

SPI有四种传输模式,如表 21.1.2 所示,主要差别在于CPOL和CPHA的不同。

CPOL(Clock Polarity,时钟极性)表示SCK在空闲时为高电平还是低电平。当CPOL=0,SCK空闲时为低电平,当CPOL=1,SCK空闲时为高电平。

CPHA(Clock Phase,时钟相位)表示SCK在第几个时钟边缘采样数据。当CPHA=0,在SCK第一个边沿采样数据,当CPHA=1,在SCK第二个边沿采样数据。

1.2、spi的四种模式

spi一般都是四线的(SCLK、MOSI、MISO、CS),一般还会有DC引脚,用来控制SPI通讯是发送命令还是发送数据。但是DC引脚是不一定需要的。下面将介绍spi的四种模式的时序。

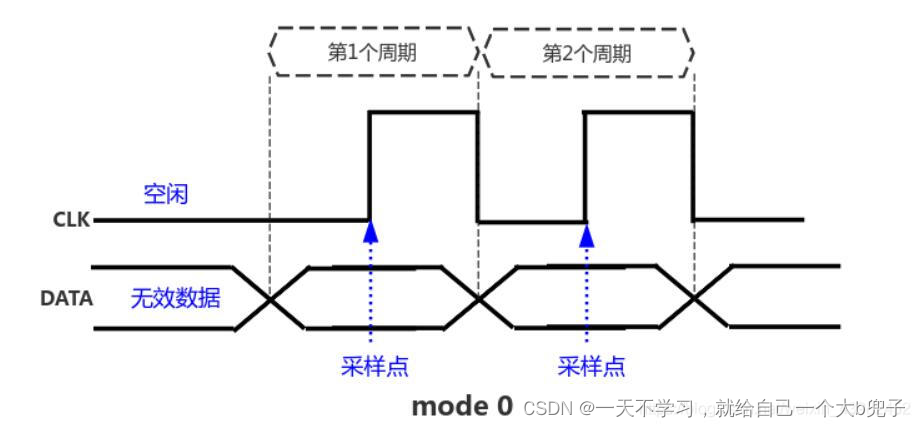

1.2.1、模式0 (CPOL=0 CPHA=0)

CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿。

CPHA = 0:数据在第1个跳变沿(上升沿)采样。

时序图如下:

(1)在clk方波信号的第一个上升沿对MOSI(发送数据)或者MISO(接收数据)的电平信号进行检测。

(2)在clk方波的第一个上升沿的前后一段时间内,DATA数据引脚的电平一定要保持稳定。

(3) 在每次数据传输完成之后,必须保证CLK的电平处于空闲状态,clk的空闲状态与CPOL相关。

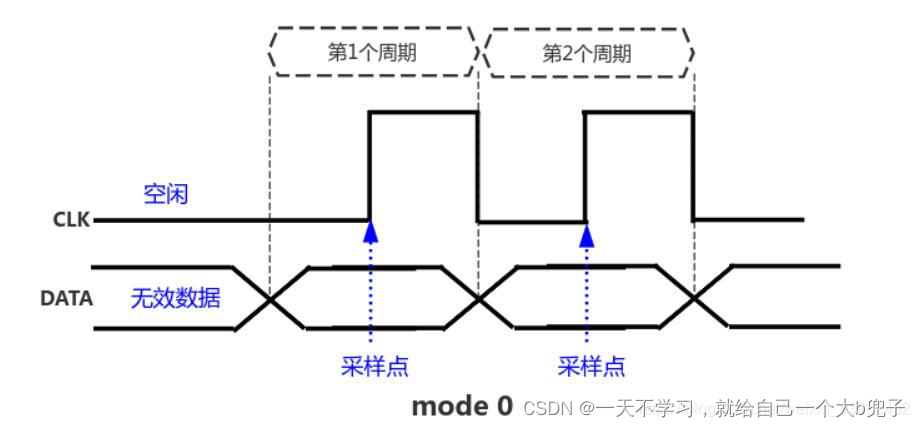

1.2.2、模式1 (CPOL=0 CPHA=0)

CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 0:数据在第1个跳变沿(上升沿)采样

时序图如下:

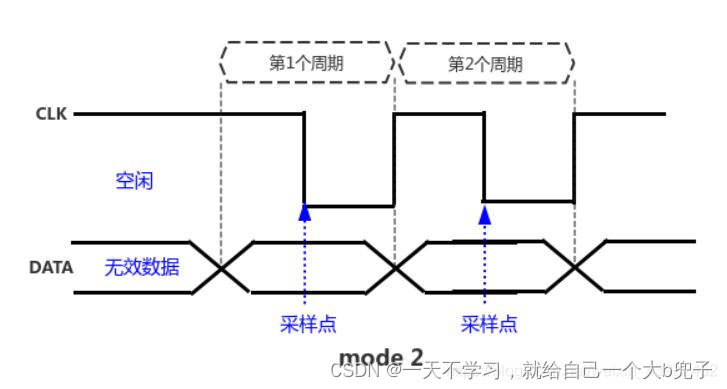

1.2.3、模式2 (CPOL=1 CPHA=0)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 0:数据在第1个跳变沿(下降沿)采样

时序图如下:

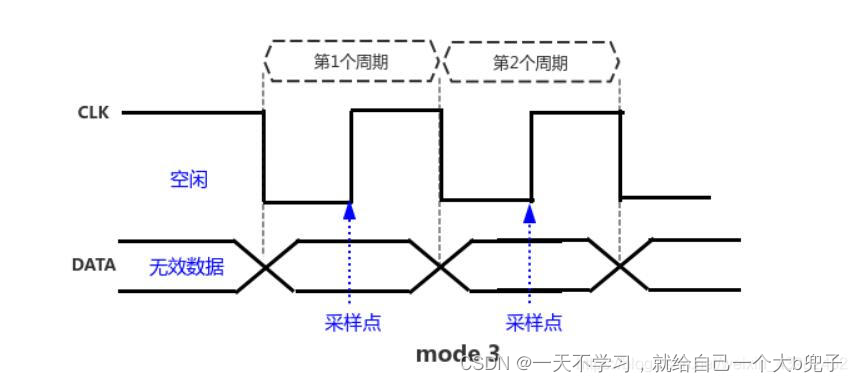

1.2.4、模式3 (CPOL=1 CPHA=1)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 1:数据在第2个跳变沿(上升沿)采样

时序图如下:

spi比较重要参数就是四种模式,以及clk的频率,传输的电平之间延时的时间。

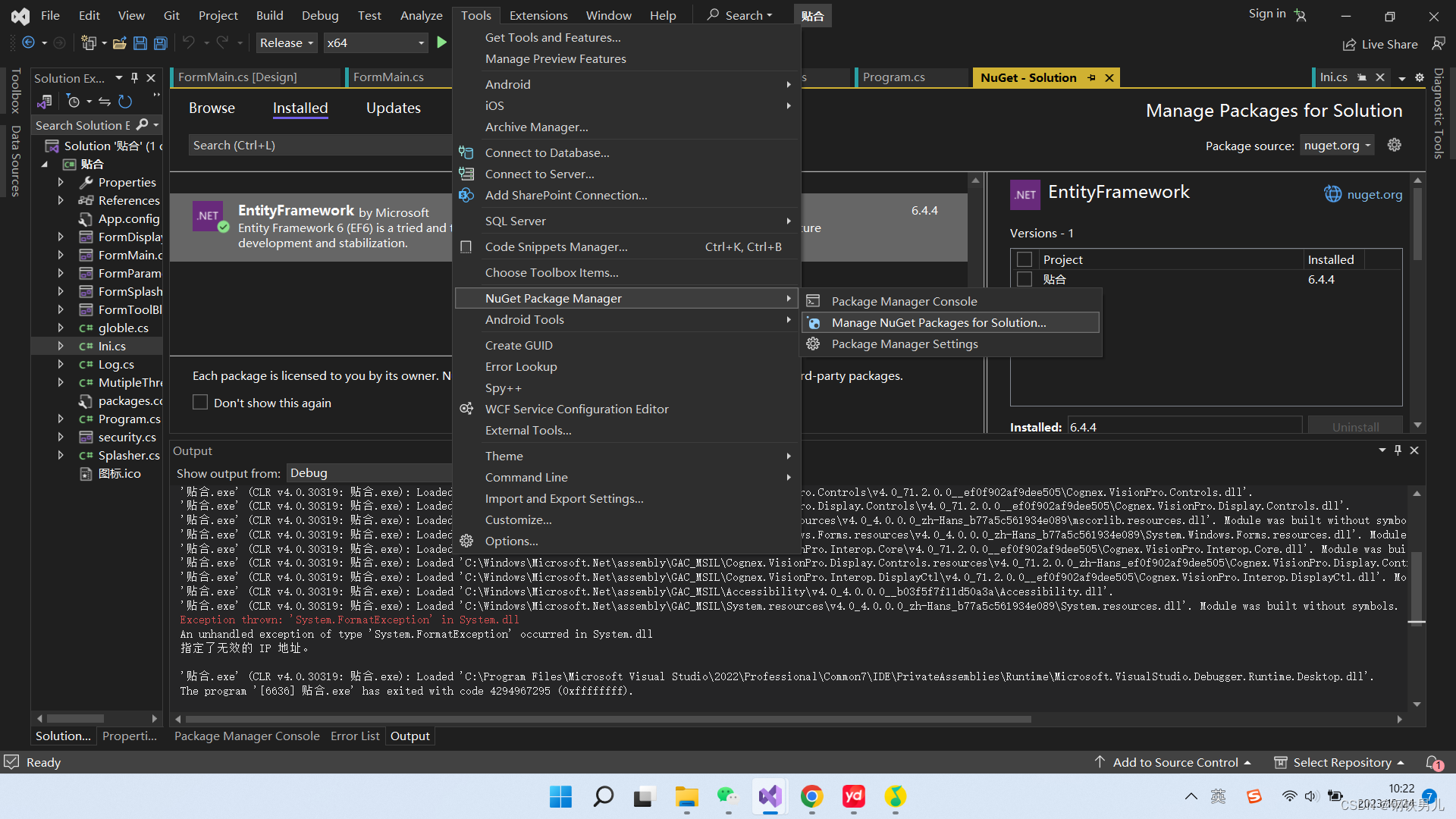

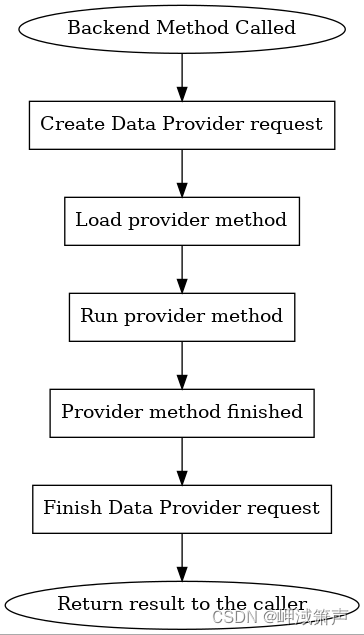

二、软件spi的使用(ADXL362为例)

软件spi的时序是比较简单的,没有IIC的时序复杂,并没有起始信号,停止信号,以及ACK和NACK应答信号。只需要在CLK的跳变沿利用MOSI发送数据,利用MISO接收数据就可以了。数据电平需要在CLK的跳变沿前后保持稳定。

不同的模式对应的时序不同,软件SPI的代码也是不同的,下面以ADXL362姿态传感器芯片为例,进行软件SPI的设计。

2.1、ADXL362姿态传感器介绍

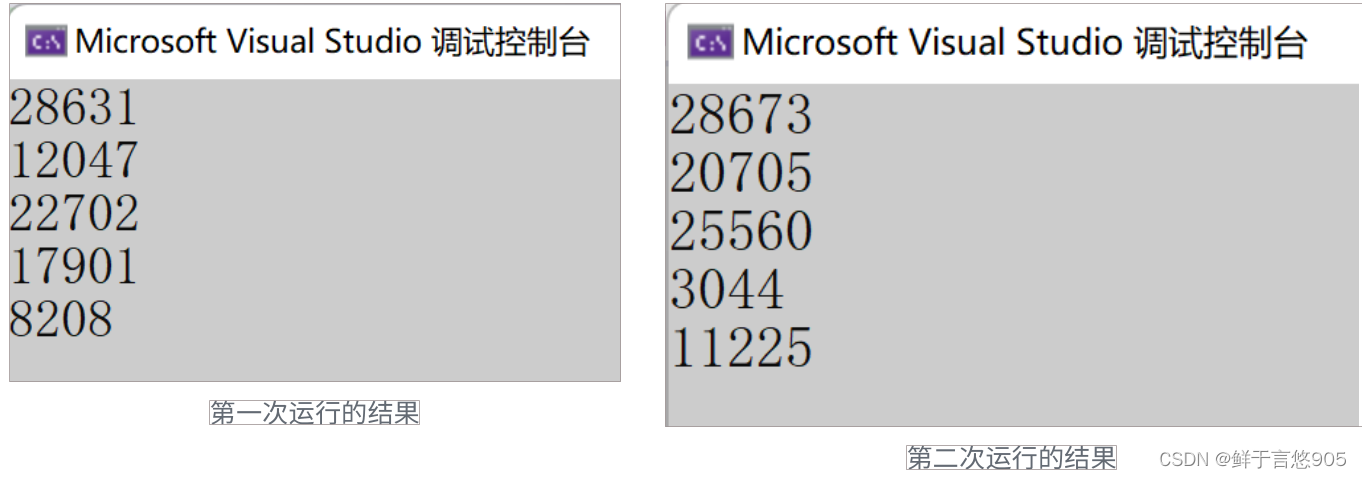

对ADXL362的软件SPI的测试,(1)首先的通过软件SPI读取芯片的id。(2)利用ADXL362的可读可写寄存器,向寄存器中写入数据之后,在读出写入寄存器的数据,观察是否相同。

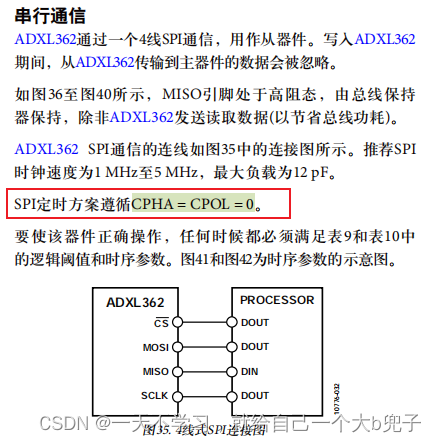

下图所示的是ADXL362芯片需要使用的SPI的模式。CPHA=CPOL=0。

下面是SPI的相关的读写指令的使用。操作寄存器前,需要先写入SPI命令。

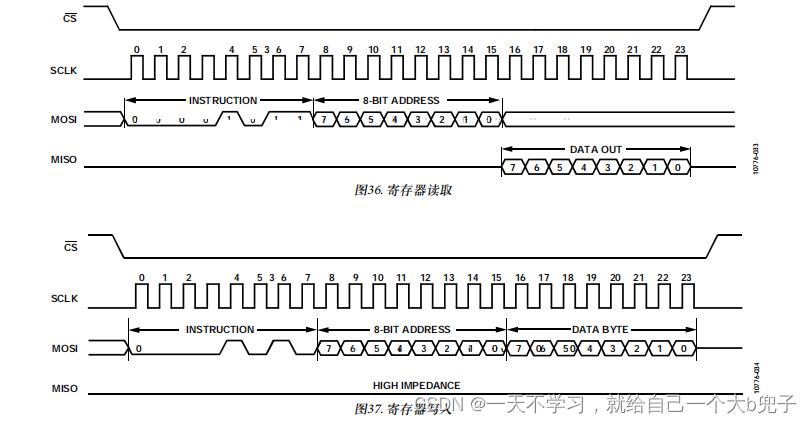

下面是SPI的时序,模拟SPI就需要根据下面的时序来写。

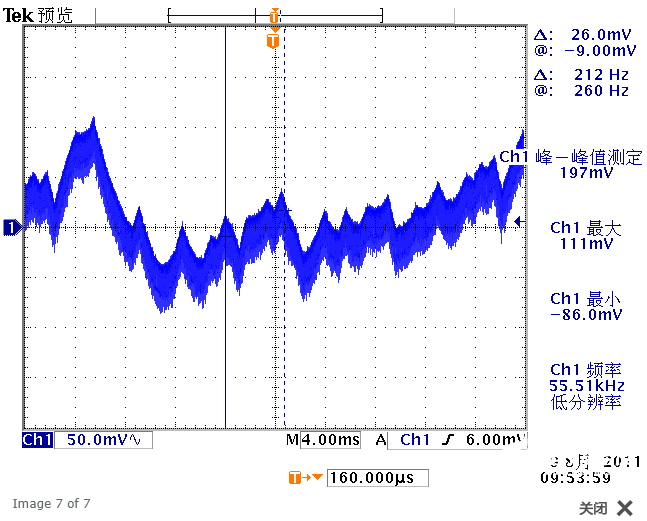

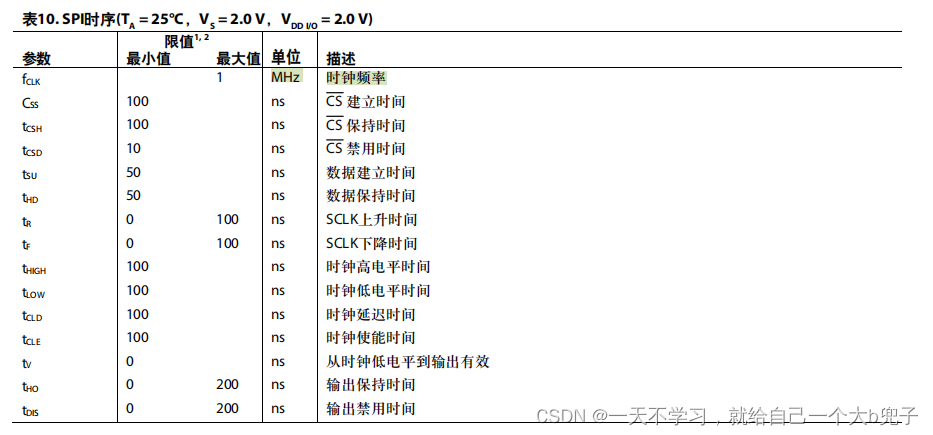

下面是对SPI时序中的延时的规定,其他基本都符合要求,需要注意的是时钟频率,也就是CLK的跳变的频率。例如使用STM32f103zet6进行控制,时钟频率为72Mhz,clk的频率至少是AHB的72Mhz时钟的72分频才能够满足ADXL362的最低通讯时钟频率的要求。

下面是ADXL362芯片的ID读取的寄存器。

2.2、模式0的模拟SPI的软件设计(基于ADXL362)

模式0的spi是在CLK的第一个跳变沿(上升沿)进行信号的检测。